Video to SDI Tx Bridge模块video_data(SD-SDI)处理过程

Posted on 2017-08-08 16:33 沉默改良者 阅读(1847) 评论(0) 编辑 收藏 举报Video to SDI Tx Bridge模块video_data(SD-SDI)处理过程

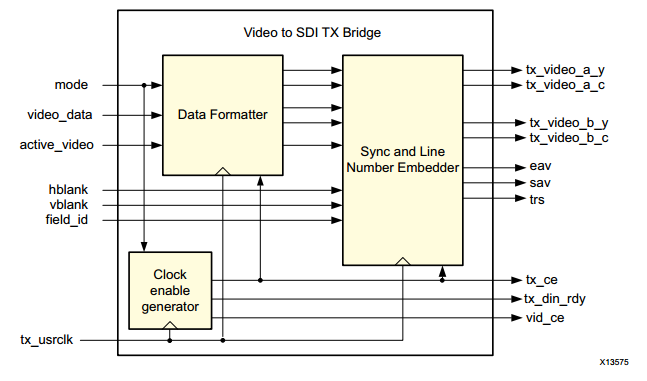

1.Top Level Block Diagram of Video to SDI TX Bridge

Video_data首先进入Data Formatter模块

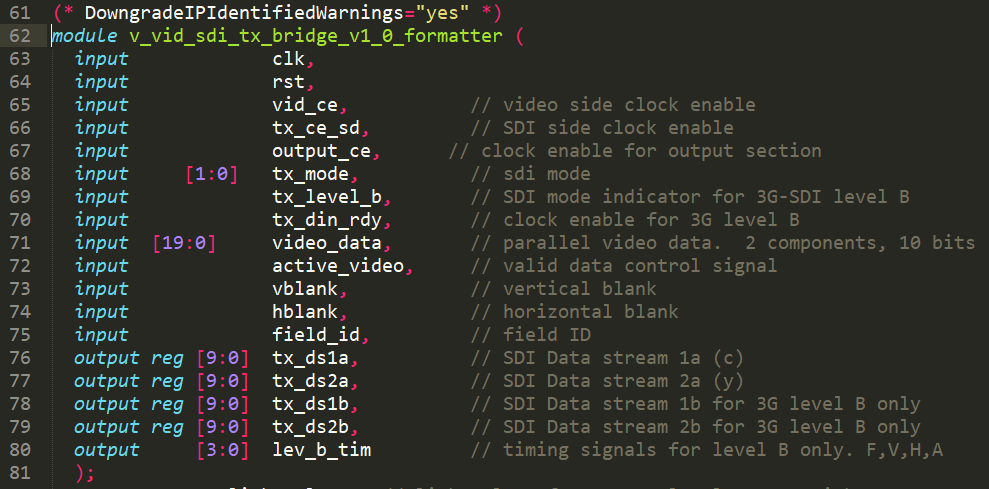

Input [19:0]video_data

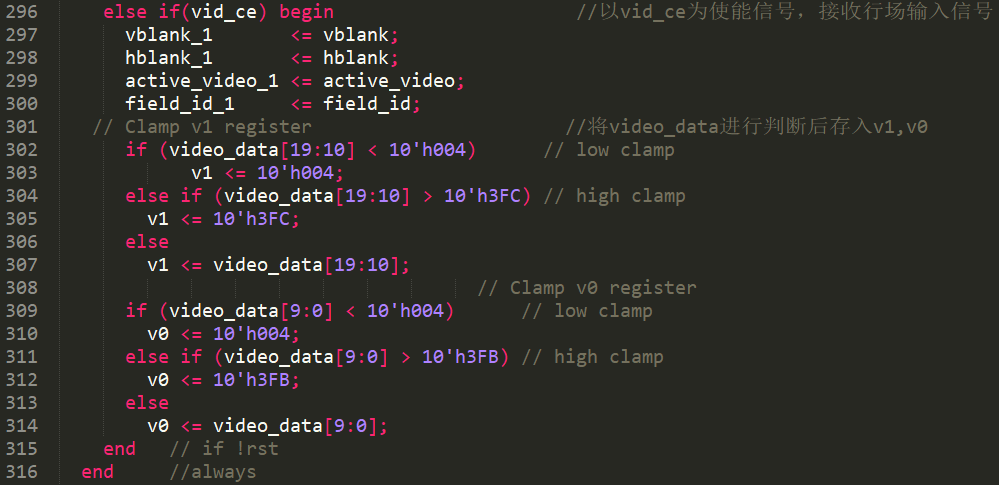

打入Data Formatter模块的video_data数据首先是判断上下限,(004,3FC,3FB).然后video_data高10位存入v1寄存器,低10位存入v0寄存器。

Hblank_1和vblank_1信号对vid_a_c和vid_a_y进行填充。

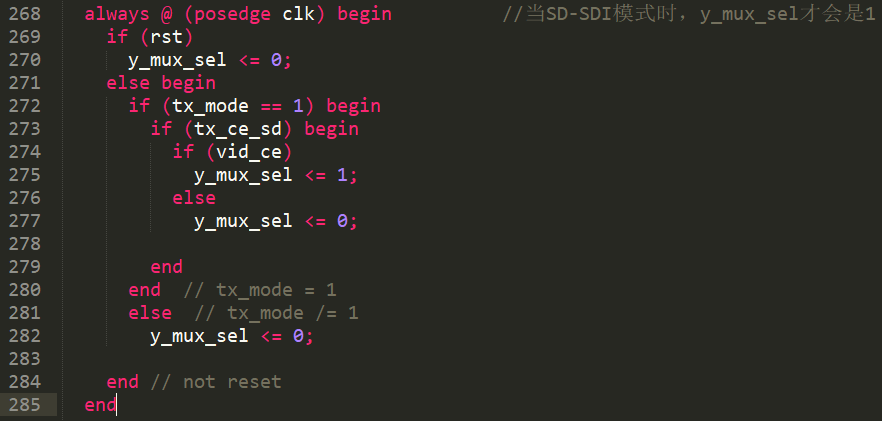

v1和v0寄存器中的数据分别存入vid_a_c和vid_a_y两个寄存器。需要注意的是:y_mux_sel信号来选择v1,v0传递到vid_a_y,也就是说当源是SD-SDI模式的时候,vid_a前十位和后十位是一样的数据。

然后,vid_a_c,vid_a_y信号融合,存入vid_a信号中。

然后,vid_a_c,vid_a_y信号融合,存入vid_a信号中。

从video_data到vid_a需要两个时钟周期。

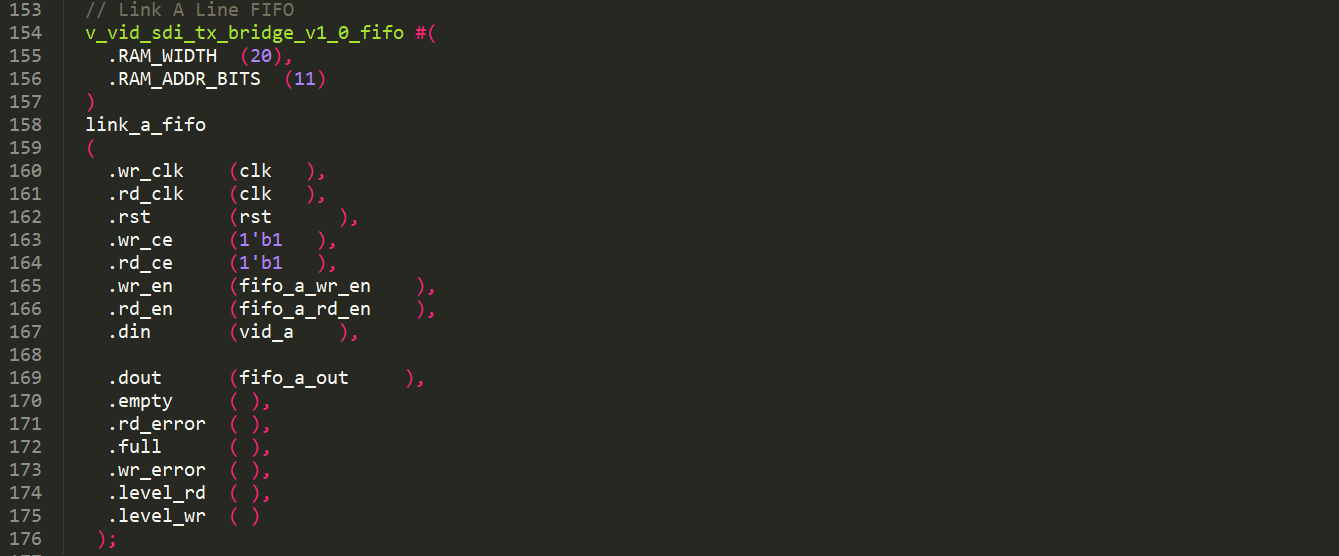

Vid_a信号会进入fifo中,现在暂且不分析fifo:

对于SD-SDI模式的信号,不用分析fifo:

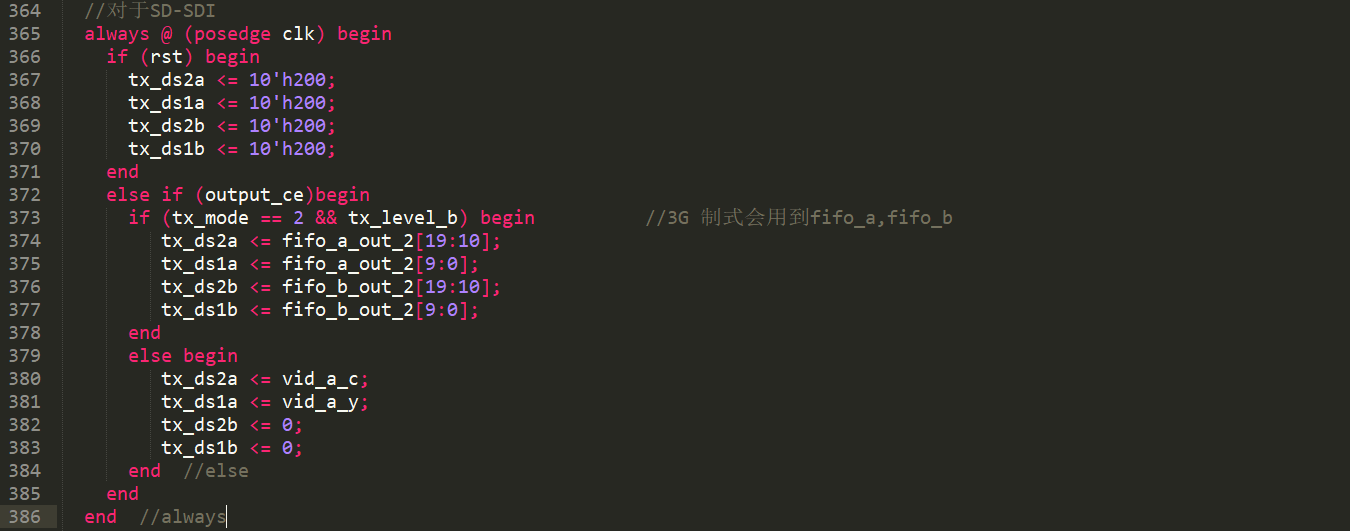

3G-SDI模式的数据需要通过fifo,但是SD-SDI模式的数据直接通过tx_ds2a,tx_ds1a输出。

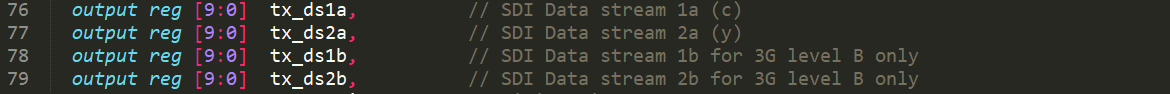

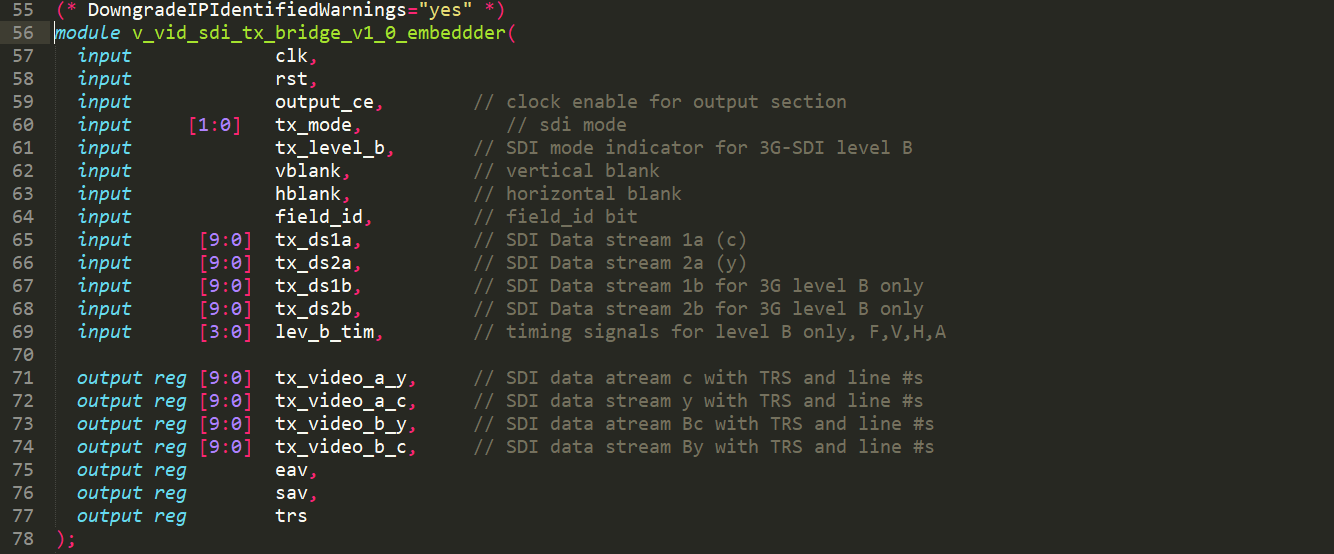

tx_ds2a,tx_ds1a数据进入了Sync and line Number Embedder模块。

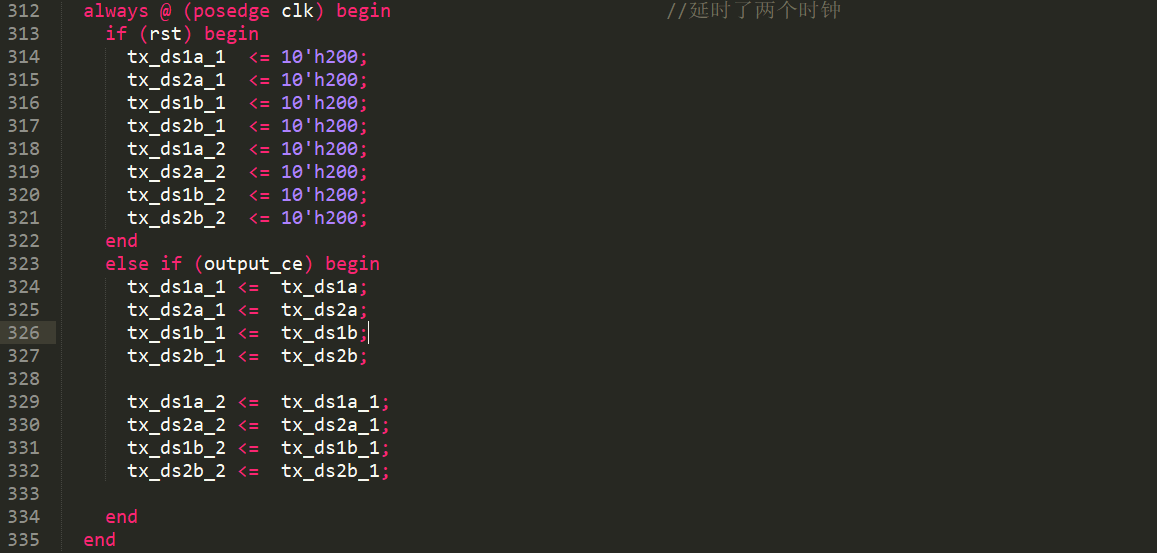

进入embedder模块的数据先延时两个时钟周期

为什么会需要这么处理,需要继续研究。

TRS信号的生成:

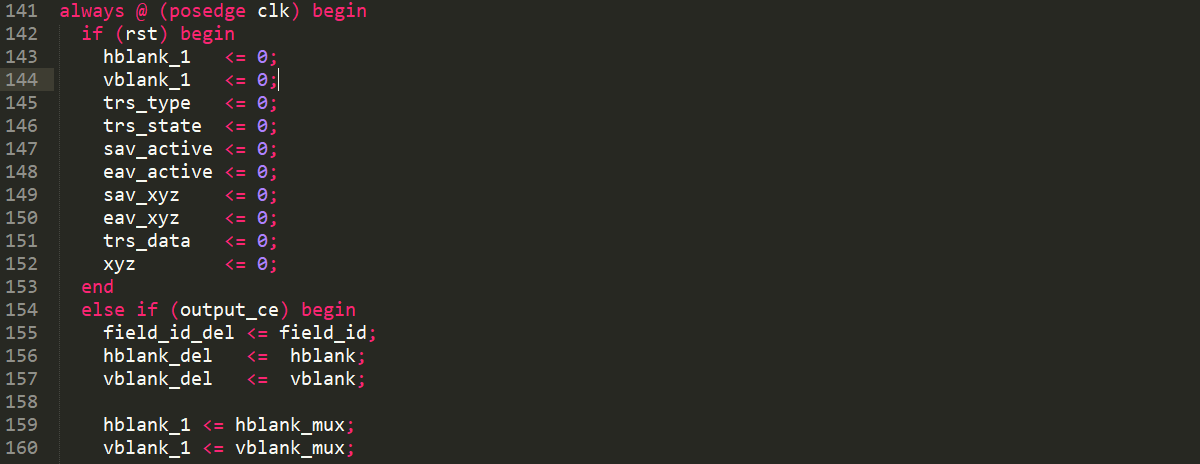

当output_ce使能时,接收hblank,vblank信号

hblank,vblank存入hblank_del,vblank_del,当信号为SD-SDI模式信号时,hblank_del,vblank_del存入vblank_mux,hblank_mux,vblank_mux,hblank_mux存入hblank_1和vblank_1(为什么需要这样做延时处理)

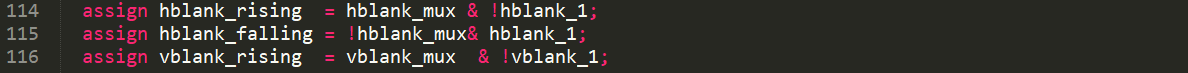

程序中对hblank和vblank进行上升沿检测和下降沿检测。

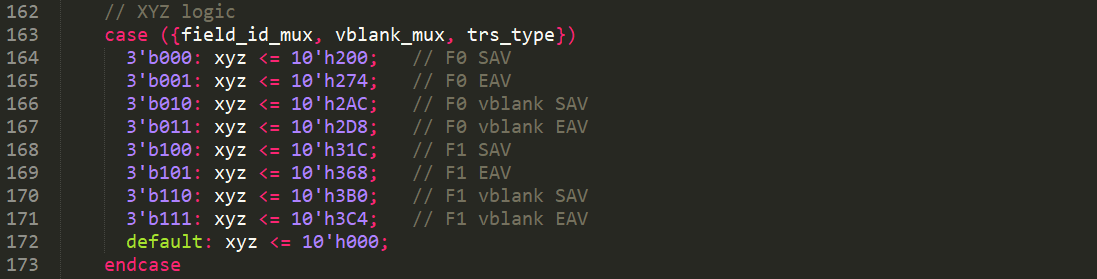

XYZ序列的产生逻辑:

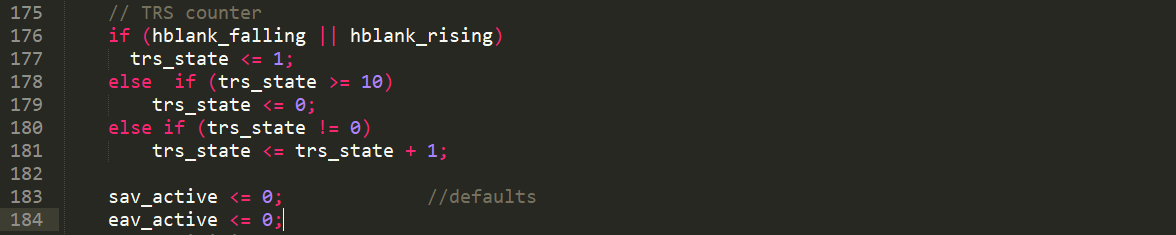

TRS状态计数器(需要hblank的边沿触发):

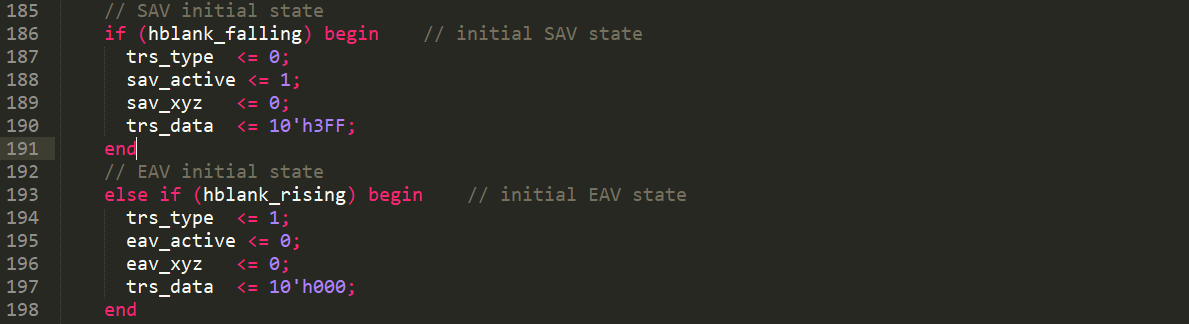

SAV和EAV的初始化:

trs_type的值确定数据是SAV还是EAV,sav_active,sav_xyz代表当前传入的trs_data数据是哪一部分的,是放在XYZ位上还是3FF,或是000上。

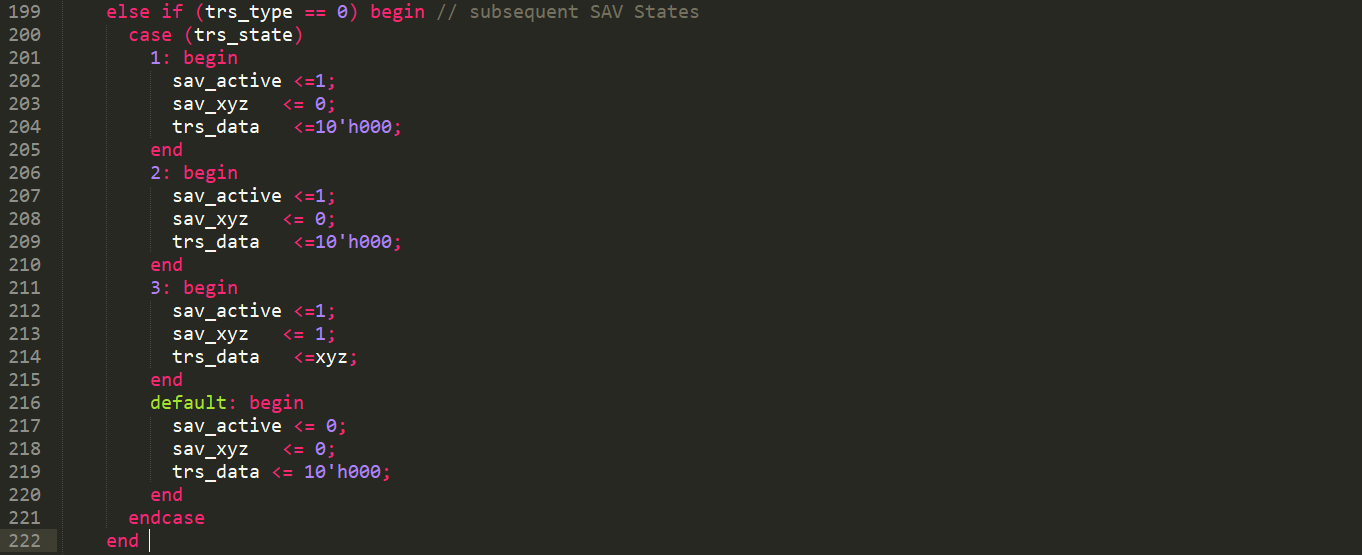

当trs_type==0时,对SAV序列进行填充,先前传入了3FF,下面依次传入000,000,XYZ的数据,这样就构成了trs_data数据序列。

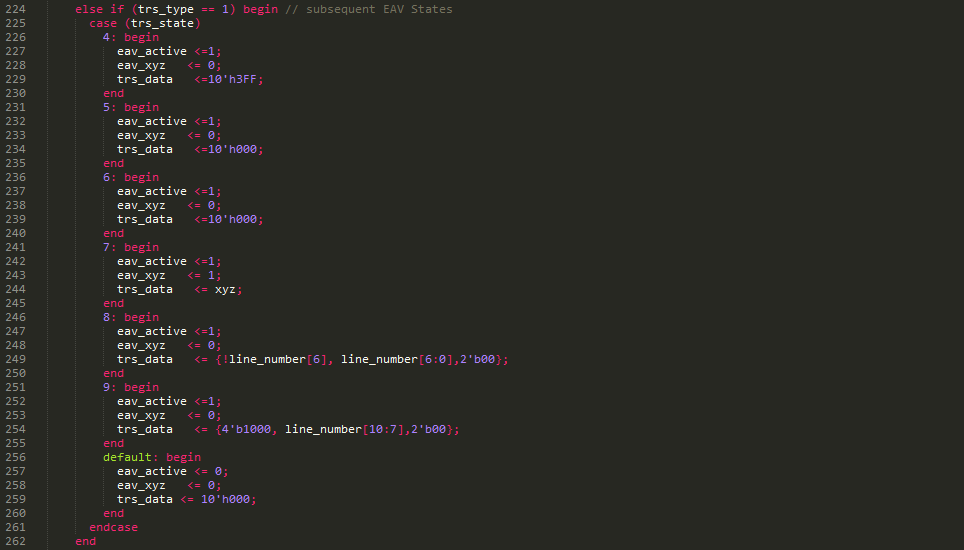

当trs_type==1时,对EAV序列进行填充,3FF,000,000,再加上一些其它的序列。

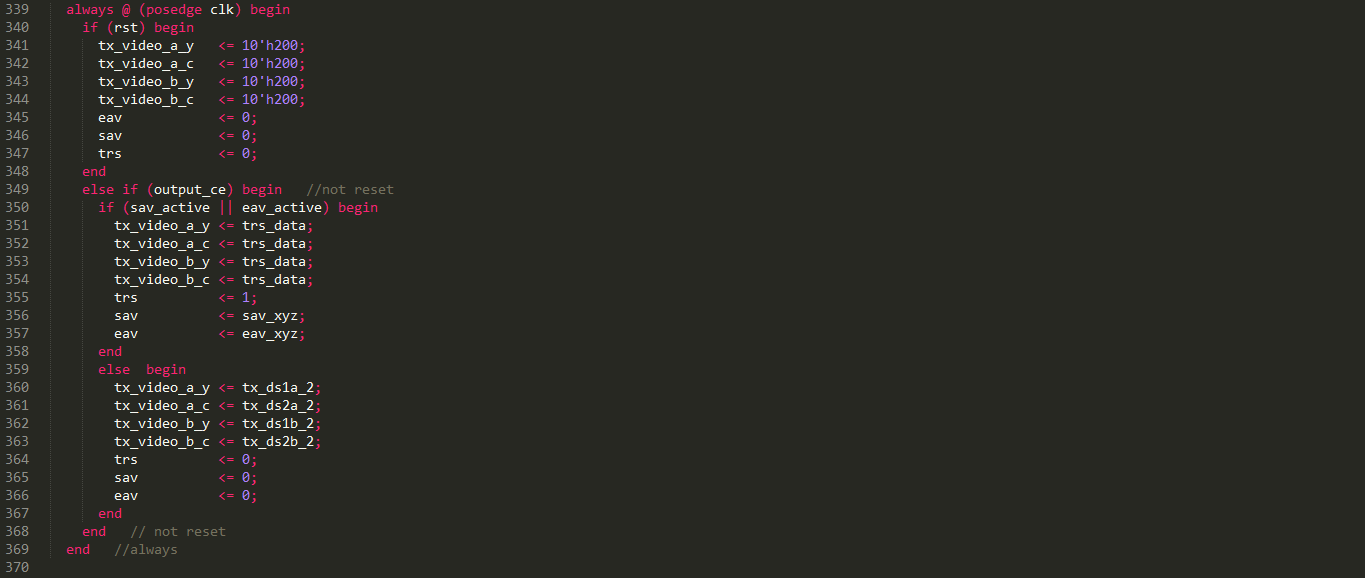

视频数据的输出:

当标志位sav_active或者eav_active,高电平时,trs_data数据传给tx_video_a_y,tx_video_a_c

SAV和EAV之间的数据用tx_ds1a_2,tx_ds2a_2填充来传递给tx_video_a_y,tx_video_a_c.

tx_video_a_y,tx_video_a_c即是最终需要传递给SDI播出的数据流。