时钟分频方法---verilog代码

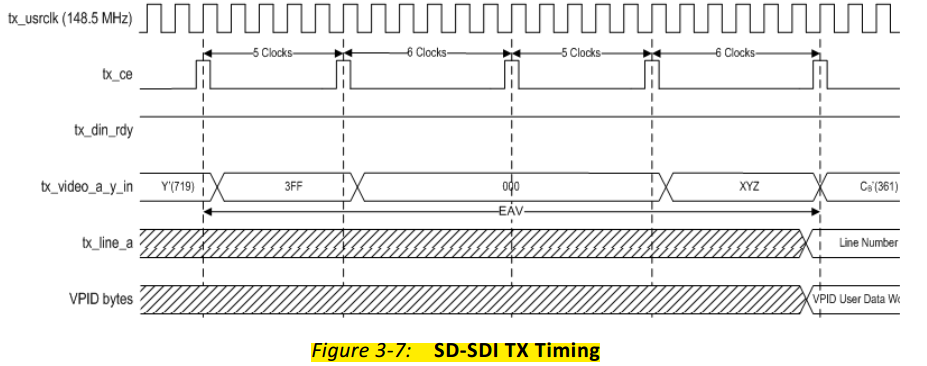

本文以SDI播出部分的工程为例,来说明一种时钟分频的写法。SD-SDI工程中播出时钟tx_usrclk为148.5MHz,但tx_video_a_y_in端的数据采样与tx_ce(门控时钟)有关。通过对tx_usrclk时钟进行分频,5clocks---6clocks---5clocks---6clocks,得到tx_ce信号。

verilog代码写法如下:

reg [2:0] tx_ce = 3'b111; reg tx_sd_ce = 1'b0; reg [10:0] tx_gen_sd_ce = 11'b00000100001; // Generates 5/6/5/6 cadence SD-SDI TX clock enable wire tx_ce_mux; // Used to generate the tx_ce signals // // TX clock enable generator // // sd_ce runs at 27 MHz and is asserted at a 5/6/5/6 cadence // tx_ce is always 1 for 3G-SDI and HD-SDI and equal to sd_ce for SD-SDI // // Create 3 identical but separate copies of the clock enable for loading purposes. // always @ (posedge tx_usrclk) if (tx_fabric_reset) //复位信号来源于? tx_gen_sd_ce <= 11'b00000100001; else tx_gen_sd_ce <= {tx_gen_sd_ce[9:0], tx_gen_sd_ce[10]}; //此段代码用于产生 always @ (posedge tx_usrclk) tx_sd_ce <= tx_gen_sd_ce[10]; assign tx_ce_mux = tx_mode == 2'b01 ? tx_gen_sd_ce[10] : 1'b1; always @ (posedge tx_usrclk) tx_ce <= {3 {tx_ce_mux}};

重点关注tx_gen_sd_ce = 11'b00000100001信号,用来生成5/6/5/6序列。

always @ (posedge tx_usrclk) if (tx_fabric_reset) //复位信号来源于? tx_gen_sd_ce <= 11'b00000100001; else tx_gen_sd_ce <= {tx_gen_sd_ce[9:0], tx_gen_sd_ce[10]}; //此段代码用于产生

always @ (posedge tx_usrclk) tx_sd_ce <= tx_gen_sd_ce[10];

每当tx_usrclk上升沿到来时,tx_gen_sd_ce左移一位,最高位移到最低位。tx_sd_ce取tx_gen_sd_ce的最高位,需要注意的是:tx_gen_sd_ce 和tx_sd_ce是同时变化的,都由tx_usrclk上升沿控制。

当tx_gen_sd_ce = 10000100000时,tx_sd_ce为高电平,由此开始,当下一次tx_sd_ce为高电平时,tx_gen_sd_ce = 10000010000需要花费5clocks,当tx_sd_ce再次为高电平时,tx_gen_sd_ce = 10000100000需要花费6clocks,循环下去,由此就产生了5/6/5/6序列。

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 10年+ .NET Coder 心语,封装的思维:从隐藏、稳定开始理解其本质意义

· .NET Core 中如何实现缓存的预热?

· 从 HTTP 原因短语缺失研究 HTTP/2 和 HTTP/3 的设计差异

· AI与.NET技术实操系列:向量存储与相似性搜索在 .NET 中的实现

· 基于Microsoft.Extensions.AI核心库实现RAG应用

· 10年+ .NET Coder 心语 ── 封装的思维:从隐藏、稳定开始理解其本质意义

· 地球OL攻略 —— 某应届生求职总结

· 提示词工程——AI应用必不可少的技术

· Open-Sora 2.0 重磅开源!

· 周边上新:园子的第一款马克杯温暖上架