阅读 RAM-Based Shift Register(ALTSHIFT_TAPS) IP Core User Guide

Posted on 2017-03-10 09:53 沉默改良者 阅读(1347) 评论(0) 编辑 收藏 举报阅读 RAM-Based Shift Register(ALTSHIFT_TAPS) IP Core User Guide

说明:本文档自带测试工程:

DE_ALTSHIFT_TAPS.zip

1.支持单bit与多bit传输模式

可以理解为:一个时钟周期内,可以传送1bit数据,也可以传送多bit数据。

2.关于taps 的理解

Taps 相当于把整串数据分段,而且必须要遵循等分的原则,taps的最高位段的数据存储的是这串数据的第一个数据。

3.参数配置

4.仿真与分析

解压工程文件得到:

关于shift Register配置表如图:

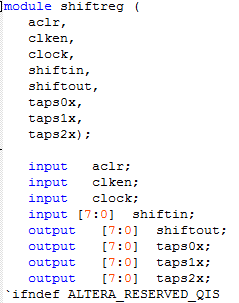

shiftreg.v文件如下:

// megafunction wizard: %Shift register (RAM-based)% // GENERATION: STANDARD // VERSION: WM1.0 // MODULE: altshift_taps // ============================================================ // File Name: shiftreg.v // Megafunction Name(s): // altshift_taps // // Simulation Library Files(s): // altera_mf // ============================================================ // ************************************************************ // THIS IS A WIZARD-GENERATED FILE. DO NOT EDIT THIS FILE! // // 8.0 Build 211 05/07/2008 SJ Full Version // ************************************************************ //Copyright (C) 1991-2008 Altera Corporation //Your use of Altera Corporation's design tools, logic functions //and other software and tools, and its AMPP partner logic //functions, and any output files from any of the foregoing //(including device programming or simulation files), and any //associated documentation or information are expressly subject //to the terms and conditions of the Altera Program License //Subscription Agreement, Altera MegaCore Function License //Agreement, or other applicable license agreement, including, //without limitation, that your use is for the sole purpose of //programming logic devices manufactured by Altera and sold by //Altera or its authorized distributors. Please refer to the //applicable agreement for further details. // synopsys translate_off `timescale 1 ps / 1 ps // synopsys translate_on module shiftreg ( aclr, clken, clock, shiftin, shiftout, taps0x, taps1x, taps2x, taps3x); input aclr; input clken; input clock; input [7:0] shiftin; output [7:0] shiftout; output [7:0] taps0x; output [7:0] taps1x; output [7:0] taps2x; output [7:0] taps3x; wire [31:0] sub_wire0; wire [7:0] sub_wire7; wire [15:8] sub_wire5 = sub_wire0[15:8]; wire [7:0] sub_wire6 = sub_wire0[7:0]; wire [23:16] sub_wire4 = sub_wire0[23:16]; wire [23:16] sub_wire3 = sub_wire4[23:16]; wire [31:24] sub_wire2 = sub_wire0[31:24]; wire [31:24] sub_wire1 = sub_wire2[31:24]; wire [7:0] taps3x = sub_wire1[31:24]; wire [7:0] taps2x = sub_wire3[23:16]; wire [7:0] taps1x = sub_wire5[15:8]; wire [7:0] taps0x = sub_wire6[7:0]; wire [7:0] shiftout = sub_wire7[7:0]; altshift_taps altshift_taps_component ( .clken (clken), .aclr (aclr), .clock (clock), .shiftin (shiftin), .taps (sub_wire0), .shiftout (sub_wire7)); defparam altshift_taps_component.lpm_hint = "RAM_BLOCK_TYPE=MLAB", altshift_taps_component.lpm_type = "altshift_taps", altshift_taps_component.number_of_taps = 4, altshift_taps_component.tap_distance = 3, altshift_taps_component.width = 8; endmodule // ============================================================ // CNX file retrieval info // ============================================================ // Retrieval info: PRIVATE: ACLR NUMERIC "1" // Retrieval info: PRIVATE: CLKEN NUMERIC "1" // Retrieval info: PRIVATE: GROUP_TAPS NUMERIC "1" // Retrieval info: PRIVATE: INTENDED_DEVICE_FAMILY STRING "Stratix III" // Retrieval info: PRIVATE: NUMBER_OF_TAPS NUMERIC "4" // Retrieval info: PRIVATE: RAM_BLOCK_TYPE NUMERIC "0" // Retrieval info: PRIVATE: SYNTH_WRAPPER_GEN_POSTFIX STRING "0" // Retrieval info: PRIVATE: TAP_DISTANCE NUMERIC "3" // Retrieval info: PRIVATE: WIDTH NUMERIC "8" // Retrieval info: CONSTANT: LPM_HINT STRING "RAM_BLOCK_TYPE=MLAB" // Retrieval info: CONSTANT: LPM_TYPE STRING "altshift_taps" // Retrieval info: CONSTANT: NUMBER_OF_TAPS NUMERIC "4" // Retrieval info: CONSTANT: TAP_DISTANCE NUMERIC "3" // Retrieval info: CONSTANT: WIDTH NUMERIC "8" // Retrieval info: USED_PORT: aclr 0 0 0 0 INPUT VCC aclr // Retrieval info: USED_PORT: clken 0 0 0 0 INPUT VCC clken // Retrieval info: USED_PORT: clock 0 0 0 0 INPUT NODEFVAL clock // Retrieval info: USED_PORT: shiftin 0 0 8 0 INPUT NODEFVAL shiftin[7..0] // Retrieval info: USED_PORT: shiftout 0 0 8 0 OUTPUT NODEFVAL shiftout[7..0] // Retrieval info: USED_PORT: taps0x 0 0 8 0 OUTPUT NODEFVAL taps0x[7..0] // Retrieval info: USED_PORT: taps1x 0 0 8 0 OUTPUT NODEFVAL taps1x[7..0] // Retrieval info: USED_PORT: taps2x 0 0 8 0 OUTPUT NODEFVAL taps2x[7..0] // Retrieval info: USED_PORT: taps3x 0 0 8 0 OUTPUT NODEFVAL taps3x[7..0] // Retrieval info: CONNECT: @shiftin 0 0 8 0 shiftin 0 0 8 0 // Retrieval info: CONNECT: shiftout 0 0 8 0 @shiftout 0 0 8 0 // Retrieval info: CONNECT: taps0x 0 0 8 0 @taps 0 0 8 0 // Retrieval info: CONNECT: taps1x 0 0 8 0 @taps 0 0 8 8 // Retrieval info: CONNECT: taps2x 0 0 8 0 @taps 0 0 8 16 // Retrieval info: CONNECT: taps3x 0 0 8 0 @taps 0 0 8 24 // Retrieval info: CONNECT: @clock 0 0 0 0 clock 0 0 0 0 // Retrieval info: CONNECT: @clken 0 0 0 0 clken 0 0 0 0 // Retrieval info: CONNECT: @aclr 0 0 0 0 aclr 0 0 0 0 // Retrieval info: LIBRARY: altera_mf altera_mf.altera_mf_components.all // Retrieval info: GEN_FILE: TYPE_NORMAL shiftreg.v TRUE // Retrieval info: GEN_FILE: TYPE_NORMAL shiftreg.inc TRUE // Retrieval info: GEN_FILE: TYPE_NORMAL shiftreg.cmp TRUE // Retrieval info: GEN_FILE: TYPE_NORMAL shiftreg.bsf TRUE // Retrieval info: GEN_FILE: TYPE_NORMAL shiftreg_inst.v TRUE // Retrieval info: GEN_FILE: TYPE_NORMAL shiftreg_bb.v TRUE // Retrieval info: GEN_FILE: TYPE_NORMAL shiftreg_waveforms.html TRUE // Retrieval info: GEN_FILE: TYPE_NORMAL shiftreg_wave*.jpg FALSE // Retrieval info: LIB_FILE: altera_mf

testbench如下:

// Copyright (C) 1991-2008 Altera Corporation // Your use of Altera Corporation's design tools, logic functions // and other software and tools, and its AMPP partner logic // functions, and any output files from any of the foregoing // (including device programming or simulation files), and any // associated documentation or information are expressly subject // to the terms and conditions of the Altera Program License // Subscription Agreement, Altera MegaCore Function License // Agreement, or other applicable license agreement, including, // without limitation, that your use is for the sole purpose of // programming logic devices manufactured by Altera and sold by // Altera or its authorized distributors. Please refer to the // applicable agreement for further details. // ***************************************************************************** // This file contains a Verilog test bench with test vectors .The test vectors // are exported from a vector file in the Quartus Waveform Editor and apply to // the top level entity of the current Quartus project .The user can use this // testbench to simulate his design using a third-party simulation tool . // ***************************************************************************** // Generated on "06/11/2008 17:15:53" // Verilog Test Bench (with test vectors) for design : shiftreg // // Simulation tool : 3rd Party // `timescale 1 ps/ 1 ps module shiftreg_vlg_vec_tst(); // constants // general purpose registers reg aclr; reg clken; reg clock; reg [7:0] shiftin; // wires wire [7:0] shiftout; wire [7:0] taps0x; wire [7:0] taps1x; wire [7:0] taps2x; wire [7:0] taps3x; // assign statements (if any) shiftreg i1 ( // port map - connection between master ports and signals/registers .aclr(aclr), .clken(clken), .clock(clock), .shiftin(shiftin), .shiftout(shiftout), .taps0x(taps0x), .taps1x(taps1x), .taps2x(taps2x), .taps3x(taps3x) ); initial begin #1000000 $stop; end // clock always begin clock = 1'b0; clock = #5000 1'b1; #5000; end // clken initial begin clken = 1'b0; clken = #10000 1'b1; end // aclr initial begin aclr = 1'b0; aclr = #150000 1'b0; aclr = #5000 1'b1; aclr = #8000 1'b0; aclr = #825000 1'bX; aclr = #12000 1'b0; aclr = #9000 1'bX; aclr = #6000 1'b0; end // shiftin[ 7 ] initial begin shiftin[7] = 1'b1; shiftin[7] = #40000 1'b0; shiftin[7] = #10000 1'b1; shiftin[7] = #10000 1'b0; shiftin[7] = #10000 1'b1; shiftin[7] = #10000 1'b0; shiftin[7] = #80000 1'b1; shiftin[7] = #20000 1'b0; shiftin[7] = #10000 1'b1; shiftin[7] = #10000 1'b0; shiftin[7] = #10000 1'b1; shiftin[7] = #10000 1'b0; shiftin[7] = #10000 1'b1; shiftin[7] = #20000 1'b0; shiftin[7] = #10000 1'b1; shiftin[7] = #10000 1'b0; shiftin[7] = #30000 1'b1; shiftin[7] = #20000 1'b0; shiftin[7] = #20000 1'b1; shiftin[7] = #30000 1'b0; shiftin[7] = #10000 1'b1; shiftin[7] = #70000 1'b0; shiftin[7] = #10000 1'b1; shiftin[7] = #10000 1'b0; shiftin[7] = #10000 1'b1; shiftin[7] = #40000 1'b0; shiftin[7] = #10000 1'b1; shiftin[7] = #10000 1'b0; shiftin[7] = #10000 1'b1; shiftin[7] = #20000 1'b0; shiftin[7] = #10000 1'b1; shiftin[7] = #30000 1'b0; shiftin[7] = #20000 1'b1; shiftin[7] = #20000 1'b0; shiftin[7] = #50000 1'b1; shiftin[7] = #30000 1'b0; shiftin[7] = #20000 1'b1; shiftin[7] = #30000 1'b0; shiftin[7] = #10000 1'b1; shiftin[7] = #10000 1'b0; shiftin[7] = #20000 1'b1; shiftin[7] = #20000 1'b0; shiftin[7] = #50000 1'b1; shiftin[7] = #20000 1'b0; shiftin[7] = #20000 1'b1; shiftin[7] = #20000 1'b0; shiftin[7] = #10000 1'b1; shiftin[7] = #10000 1'b0; shiftin[7] = #10000 1'b1; shiftin[7] = #10000 1'b0; end // shiftin[ 6 ] initial begin shiftin[6] = 1'b0; shiftin[6] = #10000 1'b1; shiftin[6] = #10000 1'b0; shiftin[6] = #10000 1'b1; shiftin[6] = #10000 1'b0; shiftin[6] = #20000 1'b1; shiftin[6] = #10000 1'b0; shiftin[6] = #20000 1'b1; shiftin[6] = #20000 1'b0; shiftin[6] = #10000 1'b1; shiftin[6] = #10000 1'b0; shiftin[6] = #30000 1'b1; shiftin[6] = #20000 1'b0; shiftin[6] = #20000 1'b1; shiftin[6] = #10000 1'b0; shiftin[6] = #10000 1'b1; shiftin[6] = #10000 1'b0; shiftin[6] = #20000 1'b1; shiftin[6] = #20000 1'b0; shiftin[6] = #10000 1'b1; shiftin[6] = #20000 1'b0; shiftin[6] = #10000 1'b1; shiftin[6] = #10000 1'b0; shiftin[6] = #20000 1'b1; shiftin[6] = #50000 1'b0; shiftin[6] = #10000 1'b1; shiftin[6] = #10000 1'b0; shiftin[6] = #10000 1'b1; shiftin[6] = #20000 1'b0; shiftin[6] = #10000 1'b1; shiftin[6] = #30000 1'b0; shiftin[6] = #10000 1'b1; shiftin[6] = #10000 1'b0; shiftin[6] = #10000 1'b1; shiftin[6] = #20000 1'b0; shiftin[6] = #30000 1'b1; shiftin[6] = #30000 1'b0; shiftin[6] = #10000 1'b1; shiftin[6] = #10000 1'b0; shiftin[6] = #20000 1'b1; shiftin[6] = #10000 1'b0; shiftin[6] = #30000 1'b1; shiftin[6] = #20000 1'b0; shiftin[6] = #20000 1'b1; shiftin[6] = #10000 1'b0; shiftin[6] = #40000 1'b1; shiftin[6] = #20000 1'b0; shiftin[6] = #10000 1'b1; shiftin[6] = #10000 1'b0; shiftin[6] = #10000 1'b1; shiftin[6] = #10000 1'b0; shiftin[6] = #30000 1'b1; shiftin[6] = #10000 1'b0; shiftin[6] = #20000 1'b1; shiftin[6] = #10000 1'b0; shiftin[6] = #10000 1'b1; shiftin[6] = #90000 1'b0; end // shiftin[ 5 ] initial begin shiftin[5] = 1'b1; shiftin[5] = #30000 1'b0; shiftin[5] = #30000 1'b1; shiftin[5] = #40000 1'b0; shiftin[5] = #60000 1'b1; shiftin[5] = #30000 1'b0; shiftin[5] = #10000 1'b1; shiftin[5] = #10000 1'b0; shiftin[5] = #20000 1'b1; shiftin[5] = #20000 1'b0; shiftin[5] = #20000 1'b1; shiftin[5] = #10000 1'b0; shiftin[5] = #10000 1'b1; shiftin[5] = #10000 1'b0; shiftin[5] = #10000 1'b1; shiftin[5] = #10000 1'b0; shiftin[5] = #10000 1'b1; shiftin[5] = #10000 1'b0; shiftin[5] = #30000 1'b1; shiftin[5] = #10000 1'b0; shiftin[5] = #10000 1'b1; shiftin[5] = #20000 1'b0; shiftin[5] = #10000 1'b1; shiftin[5] = #20000 1'b0; shiftin[5] = #50000 1'b1; shiftin[5] = #20000 1'b0; shiftin[5] = #10000 1'b1; shiftin[5] = #40000 1'b0; shiftin[5] = #20000 1'b1; shiftin[5] = #20000 1'b0; shiftin[5] = #10000 1'b1; shiftin[5] = #20000 1'b0; shiftin[5] = #20000 1'b1; shiftin[5] = #30000 1'b0; shiftin[5] = #10000 1'b1; shiftin[5] = #10000 1'b0; shiftin[5] = #10000 1'b1; shiftin[5] = #40000 1'b0; shiftin[5] = #10000 1'b1; shiftin[5] = #30000 1'b0; shiftin[5] = #20000 1'b1; shiftin[5] = #30000 1'b0; shiftin[5] = #20000 1'b1; shiftin[5] = #10000 1'b0; shiftin[5] = #70000 1'b1; shiftin[5] = #20000 1'b0; shiftin[5] = #10000 1'b1; shiftin[5] = #10000 1'b0; shiftin[5] = #10000 1'b1; end // shiftin[ 4 ] initial begin shiftin[4] = 1'b1; shiftin[4] = #50000 1'b0; shiftin[4] = #20000 1'b1; shiftin[4] = #20000 1'b0; shiftin[4] = #10000 1'b1; shiftin[4] = #10000 1'b0; shiftin[4] = #50000 1'b1; shiftin[4] = #10000 1'b0; shiftin[4] = #40000 1'b1; shiftin[4] = #10000 1'b0; shiftin[4] = #20000 1'b1; shiftin[4] = #20000 1'b0; shiftin[4] = #20000 1'b1; shiftin[4] = #10000 1'b0; shiftin[4] = #10000 1'b1; shiftin[4] = #10000 1'b0; shiftin[4] = #10000 1'b1; shiftin[4] = #10000 1'b0; shiftin[4] = #10000 1'b1; shiftin[4] = #20000 1'b0; shiftin[4] = #10000 1'b1; shiftin[4] = #10000 1'b0; shiftin[4] = #10000 1'b1; shiftin[4] = #20000 1'b0; shiftin[4] = #10000 1'b1; shiftin[4] = #20000 1'b0; shiftin[4] = #40000 1'b1; shiftin[4] = #10000 1'b0; shiftin[4] = #20000 1'b1; shiftin[4] = #10000 1'b0; shiftin[4] = #10000 1'b1; shiftin[4] = #10000 1'b0; shiftin[4] = #40000 1'b1; shiftin[4] = #10000 1'b0; shiftin[4] = #20000 1'b1; shiftin[4] = #10000 1'b0; shiftin[4] = #10000 1'b1; shiftin[4] = #20000 1'b0; shiftin[4] = #10000 1'b1; shiftin[4] = #20000 1'b0; shiftin[4] = #10000 1'b1; shiftin[4] = #20000 1'b0; shiftin[4] = #10000 1'b1; shiftin[4] = #10000 1'b0; shiftin[4] = #10000 1'b1; shiftin[4] = #20000 1'b0; shiftin[4] = #10000 1'b1; shiftin[4] = #10000 1'b0; shiftin[4] = #10000 1'b1; shiftin[4] = #30000 1'b0; shiftin[4] = #10000 1'b1; shiftin[4] = #10000 1'b0; shiftin[4] = #10000 1'b1; shiftin[4] = #10000 1'b0; shiftin[4] = #10000 1'b1; shiftin[4] = #10000 1'b0; shiftin[4] = #10000 1'b1; shiftin[4] = #20000 1'b0; shiftin[4] = #30000 1'b1; shiftin[4] = #10000 1'b0; shiftin[4] = #10000 1'b1; shiftin[4] = #10000 1'b0; end // shiftin[ 3 ] initial begin shiftin[3] = 1'b0; shiftin[3] = #10000 1'b1; shiftin[3] = #20000 1'b0; shiftin[3] = #50000 1'b1; shiftin[3] = #20000 1'b0; shiftin[3] = #10000 1'b1; shiftin[3] = #10000 1'b0; shiftin[3] = #60000 1'b1; shiftin[3] = #30000 1'b0; shiftin[3] = #10000 1'b1; shiftin[3] = #20000 1'b0; shiftin[3] = #30000 1'b1; shiftin[3] = #10000 1'b0; shiftin[3] = #10000 1'b1; shiftin[3] = #10000 1'b0; shiftin[3] = #10000 1'b1; shiftin[3] = #10000 1'b0; shiftin[3] = #10000 1'b1; shiftin[3] = #20000 1'b0; shiftin[3] = #10000 1'b1; shiftin[3] = #10000 1'b0; shiftin[3] = #20000 1'b1; shiftin[3] = #20000 1'b0; shiftin[3] = #10000 1'b1; shiftin[3] = #30000 1'b0; shiftin[3] = #10000 1'b1; shiftin[3] = #30000 1'b0; shiftin[3] = #40000 1'b1; shiftin[3] = #10000 1'b0; shiftin[3] = #20000 1'b1; shiftin[3] = #10000 1'b0; shiftin[3] = #20000 1'b1; shiftin[3] = #30000 1'b0; shiftin[3] = #10000 1'b1; shiftin[3] = #10000 1'b0; shiftin[3] = #20000 1'b1; shiftin[3] = #10000 1'b0; shiftin[3] = #30000 1'b1; shiftin[3] = #10000 1'b0; shiftin[3] = #10000 1'b1; shiftin[3] = #10000 1'b0; shiftin[3] = #40000 1'b1; shiftin[3] = #20000 1'b0; shiftin[3] = #10000 1'b1; shiftin[3] = #10000 1'b0; shiftin[3] = #10000 1'b1; shiftin[3] = #10000 1'b0; shiftin[3] = #10000 1'b1; shiftin[3] = #10000 1'b0; shiftin[3] = #10000 1'b1; shiftin[3] = #10000 1'b0; shiftin[3] = #40000 1'b1; shiftin[3] = #20000 1'b0; shiftin[3] = #20000 1'b1; shiftin[3] = #10000 1'b0; shiftin[3] = #10000 1'b1; shiftin[3] = #10000 1'b0; end // shiftin[ 2 ] initial begin shiftin[2] = 1'b0; shiftin[2] = #50000 1'b1; shiftin[2] = #30000 1'b0; shiftin[2] = #10000 1'b1; shiftin[2] = #40000 1'b0; shiftin[2] = #40000 1'b1; shiftin[2] = #20000 1'b0; shiftin[2] = #20000 1'b1; shiftin[2] = #40000 1'b0; shiftin[2] = #40000 1'b1; shiftin[2] = #40000 1'b0; shiftin[2] = #20000 1'b1; shiftin[2] = #30000 1'b0; shiftin[2] = #20000 1'b1; shiftin[2] = #30000 1'b0; shiftin[2] = #20000 1'b1; shiftin[2] = #10000 1'b0; shiftin[2] = #40000 1'b1; shiftin[2] = #60000 1'b0; shiftin[2] = #10000 1'b1; shiftin[2] = #10000 1'b0; shiftin[2] = #10000 1'b1; shiftin[2] = #20000 1'b0; shiftin[2] = #10000 1'b1; shiftin[2] = #20000 1'b0; shiftin[2] = #10000 1'b1; shiftin[2] = #40000 1'b0; shiftin[2] = #10000 1'b1; shiftin[2] = #30000 1'b0; shiftin[2] = #10000 1'b1; shiftin[2] = #10000 1'b0; shiftin[2] = #10000 1'b1; shiftin[2] = #10000 1'b0; shiftin[2] = #40000 1'b1; shiftin[2] = #20000 1'b0; shiftin[2] = #50000 1'b1; shiftin[2] = #20000 1'b0; shiftin[2] = #10000 1'b1; shiftin[2] = #10000 1'b0; shiftin[2] = #20000 1'b1; shiftin[2] = #30000 1'b0; shiftin[2] = #20000 1'b1; end // shiftin[ 1 ] initial begin shiftin[1] = 1'b1; shiftin[1] = #10000 1'b0; shiftin[1] = #30000 1'b1; shiftin[1] = #10000 1'b0; shiftin[1] = #10000 1'b1; shiftin[1] = #10000 1'b0; shiftin[1] = #10000 1'b1; shiftin[1] = #20000 1'b0; shiftin[1] = #10000 1'b1; shiftin[1] = #10000 1'b0; shiftin[1] = #40000 1'b1; shiftin[1] = #20000 1'b0; shiftin[1] = #10000 1'b1; shiftin[1] = #40000 1'b0; shiftin[1] = #10000 1'b1; shiftin[1] = #10000 1'b0; shiftin[1] = #20000 1'b1; shiftin[1] = #20000 1'b0; shiftin[1] = #10000 1'b1; shiftin[1] = #20000 1'b0; shiftin[1] = #10000 1'b1; shiftin[1] = #10000 1'b0; shiftin[1] = #10000 1'b1; shiftin[1] = #10000 1'b0; shiftin[1] = #10000 1'b1; shiftin[1] = #20000 1'b0; shiftin[1] = #10000 1'b1; shiftin[1] = #10000 1'b0; shiftin[1] = #20000 1'b1; shiftin[1] = #30000 1'b0; shiftin[1] = #10000 1'b1; shiftin[1] = #10000 1'b0; shiftin[1] = #10000 1'b1; shiftin[1] = #30000 1'b0; shiftin[1] = #30000 1'b1; shiftin[1] = #30000 1'b0; shiftin[1] = #10000 1'b1; shiftin[1] = #30000 1'b0; shiftin[1] = #30000 1'b1; shiftin[1] = #10000 1'b0; shiftin[1] = #10000 1'b1; shiftin[1] = #10000 1'b0; shiftin[1] = #20000 1'b1; shiftin[1] = #10000 1'b0; shiftin[1] = #30000 1'b1; shiftin[1] = #10000 1'b0; shiftin[1] = #10000 1'b1; shiftin[1] = #10000 1'b0; shiftin[1] = #30000 1'b1; shiftin[1] = #20000 1'b0; shiftin[1] = #10000 1'b1; shiftin[1] = #10000 1'b0; shiftin[1] = #10000 1'b1; shiftin[1] = #10000 1'b0; shiftin[1] = #10000 1'b1; shiftin[1] = #10000 1'b0; shiftin[1] = #20000 1'b1; shiftin[1] = #10000 1'b0; shiftin[1] = #20000 1'b1; shiftin[1] = #20000 1'b0; shiftin[1] = #20000 1'b1; shiftin[1] = #10000 1'b0; end // shiftin[ 0 ] initial begin shiftin[0] = 1'b1; shiftin[0] = #10000 1'b0; shiftin[0] = #30000 1'b1; shiftin[0] = #10000 1'b0; shiftin[0] = #10000 1'b1; shiftin[0] = #30000 1'b0; shiftin[0] = #100000 1'b1; shiftin[0] = #10000 1'b0; shiftin[0] = #20000 1'b1; shiftin[0] = #10000 1'b0; shiftin[0] = #10000 1'b1; shiftin[0] = #20000 1'b0; shiftin[0] = #10000 1'b1; shiftin[0] = #10000 1'b0; shiftin[0] = #20000 1'b1; shiftin[0] = #10000 1'b0; shiftin[0] = #40000 1'b1; shiftin[0] = #20000 1'b0; shiftin[0] = #10000 1'b1; shiftin[0] = #40000 1'b0; shiftin[0] = #10000 1'b1; shiftin[0] = #10000 1'b0; shiftin[0] = #20000 1'b1; shiftin[0] = #10000 1'b0; shiftin[0] = #30000 1'b1; shiftin[0] = #10000 1'b0; shiftin[0] = #20000 1'b1; shiftin[0] = #10000 1'b0; shiftin[0] = #10000 1'b1; shiftin[0] = #10000 1'b0; shiftin[0] = #20000 1'b1; shiftin[0] = #10000 1'b0; shiftin[0] = #20000 1'b1; shiftin[0] = #40000 1'b0; shiftin[0] = #20000 1'b1; shiftin[0] = #10000 1'b0; shiftin[0] = #10000 1'b1; shiftin[0] = #30000 1'b0; shiftin[0] = #20000 1'b1; shiftin[0] = #20000 1'b0; shiftin[0] = #10000 1'b1; shiftin[0] = #30000 1'b0; shiftin[0] = #10000 1'b1; shiftin[0] = #40000 1'b0; shiftin[0] = #10000 1'b1; shiftin[0] = #10000 1'b0; shiftin[0] = #20000 1'b1; shiftin[0] = #10000 1'b0; shiftin[0] = #10000 1'b1; shiftin[0] = #20000 1'b0; shiftin[0] = #30000 1'b1; shiftin[0] = #10000 1'b0; shiftin[0] = #10000 1'b1; shiftin[0] = #10000 1'b0; end endmodule

综合整个工程,得到结果:

自己按照如上参数表,配置一遍shift Register:

得到:

其实.qip里面也就一个文件:shiftreg.v

里面的信息包含有:

// megafunction wizard: %Shift register (RAM-based)% // GENERATION: STANDARD // VERSION: WM1.0 // MODULE: altshift_taps // ============================================================ // File Name: shiftreg.v // Megafunction Name(s): // altshift_taps // // Simulation Library Files(s): // altera_mf // ============================================================ // ************************************************************ // THIS IS A WIZARD-GENERATED FILE. DO NOT EDIT THIS FILE! // // 8.0 Build 211 05/07/2008 SJ Full Version // ************************************************************ //Copyright (C) 1991-2008 Altera Corporation //Your use of Altera Corporation's design tools, logic functions //and other software and tools, and its AMPP partner logic //functions, and any output files from any of the foregoing //(including device programming or simulation files), and any //associated documentation or information are expressly subject //to the terms and conditions of the Altera Program License //Subscription Agreement, Altera MegaCore Function License //Agreement, or other applicable license agreement, including, //without limitation, that your use is for the sole purpose of //programming logic devices manufactured by Altera and sold by //Altera or its authorized distributors. Please refer to the //applicable agreement for further details. // synopsys translate_off `timescale 1 ps / 1 ps // synopsys translate_on module shiftreg ( aclr, clken, clock, shiftin, shiftout, taps0x, taps1x, taps2x, taps3x); input aclr; input clken; input clock; input [7:0] shiftin; output [7:0] shiftout; output [7:0] taps0x; output [7:0] taps1x; output [7:0] taps2x; output [7:0] taps3x; wire [31:0] sub_wire0; wire [7:0] sub_wire7; wire [15:8] sub_wire5 = sub_wire0[15:8]; wire [7:0] sub_wire6 = sub_wire0[7:0]; wire [23:16] sub_wire4 = sub_wire0[23:16]; wire [23:16] sub_wire3 = sub_wire4[23:16]; wire [31:24] sub_wire2 = sub_wire0[31:24]; wire [31:24] sub_wire1 = sub_wire2[31:24]; wire [7:0] taps3x = sub_wire1[31:24]; wire [7:0] taps2x = sub_wire3[23:16]; wire [7:0] taps1x = sub_wire5[15:8]; wire [7:0] taps0x = sub_wire6[7:0]; wire [7:0] shiftout = sub_wire7[7:0]; altshift_taps altshift_taps_component ( .clken (clken), .aclr (aclr), .clock (clock), .shiftin (shiftin), .taps (sub_wire0), .shiftout (sub_wire7)); defparam altshift_taps_component.lpm_hint = "RAM_BLOCK_TYPE=MLAB", altshift_taps_component.lpm_type = "altshift_taps", altshift_taps_component.number_of_taps = 4, altshift_taps_component.tap_distance = 3, altshift_taps_component.width = 8; endmodule // ============================================================ // CNX file retrieval info // ============================================================ // Retrieval info: PRIVATE: ACLR NUMERIC "1" // Retrieval info: PRIVATE: CLKEN NUMERIC "1" // Retrieval info: PRIVATE: GROUP_TAPS NUMERIC "1" // Retrieval info: PRIVATE: INTENDED_DEVICE_FAMILY STRING "Stratix III" // Retrieval info: PRIVATE: NUMBER_OF_TAPS NUMERIC "4" // Retrieval info: PRIVATE: RAM_BLOCK_TYPE NUMERIC "0" // Retrieval info: PRIVATE: SYNTH_WRAPPER_GEN_POSTFIX STRING "0" // Retrieval info: PRIVATE: TAP_DISTANCE NUMERIC "3" // Retrieval info: PRIVATE: WIDTH NUMERIC "8" // Retrieval info: CONSTANT: LPM_HINT STRING "RAM_BLOCK_TYPE=MLAB" // Retrieval info: CONSTANT: LPM_TYPE STRING "altshift_taps" // Retrieval info: CONSTANT: NUMBER_OF_TAPS NUMERIC "4" // Retrieval info: CONSTANT: TAP_DISTANCE NUMERIC "3" // Retrieval info: CONSTANT: WIDTH NUMERIC "8" // Retrieval info: USED_PORT: aclr 0 0 0 0 INPUT VCC aclr // Retrieval info: USED_PORT: clken 0 0 0 0 INPUT VCC clken // Retrieval info: USED_PORT: clock 0 0 0 0 INPUT NODEFVAL clock // Retrieval info: USED_PORT: shiftin 0 0 8 0 INPUT NODEFVAL shiftin[7..0] // Retrieval info: USED_PORT: shiftout 0 0 8 0 OUTPUT NODEFVAL shiftout[7..0] // Retrieval info: USED_PORT: taps0x 0 0 8 0 OUTPUT NODEFVAL taps0x[7..0] // Retrieval info: USED_PORT: taps1x 0 0 8 0 OUTPUT NODEFVAL taps1x[7..0] // Retrieval info: USED_PORT: taps2x 0 0 8 0 OUTPUT NODEFVAL taps2x[7..0] // Retrieval info: USED_PORT: taps3x 0 0 8 0 OUTPUT NODEFVAL taps3x[7..0] // Retrieval info: CONNECT: @shiftin 0 0 8 0 shiftin 0 0 8 0 // Retrieval info: CONNECT: shiftout 0 0 8 0 @shiftout 0 0 8 0 // Retrieval info: CONNECT: taps0x 0 0 8 0 @taps 0 0 8 0 // Retrieval info: CONNECT: taps1x 0 0 8 0 @taps 0 0 8 8 // Retrieval info: CONNECT: taps2x 0 0 8 0 @taps 0 0 8 16 // Retrieval info: CONNECT: taps3x 0 0 8 0 @taps 0 0 8 24 // Retrieval info: CONNECT: @clock 0 0 0 0 clock 0 0 0 0 // Retrieval info: CONNECT: @clken 0 0 0 0 clken 0 0 0 0 // Retrieval info: CONNECT: @aclr 0 0 0 0 aclr 0 0 0 0 // Retrieval info: LIBRARY: altera_mf altera_mf.altera_mf_components.all // Retrieval info: GEN_FILE: TYPE_NORMAL shiftreg.v TRUE // Retrieval info: GEN_FILE: TYPE_NORMAL shiftreg.inc TRUE // Retrieval info: GEN_FILE: TYPE_NORMAL shiftreg.cmp TRUE // Retrieval info: GEN_FILE: TYPE_NORMAL shiftreg.bsf TRUE // Retrieval info: GEN_FILE: TYPE_NORMAL shiftreg_inst.v TRUE // Retrieval info: GEN_FILE: TYPE_NORMAL shiftreg_bb.v TRUE // Retrieval info: GEN_FILE: TYPE_NORMAL shiftreg_waveforms.html TRUE // Retrieval info: GEN_FILE: TYPE_NORMAL shiftreg_wave*.jpg FALSE // Retrieval info: LIB_FILE: altera_mf

综合工程,得到结果:

分析二者,代码几乎相同,这意味着只需要shiftreg.v文件,就可以实现移位寄存器的功能,基于配置的编辑器,只是用来生成这个文件的工具。

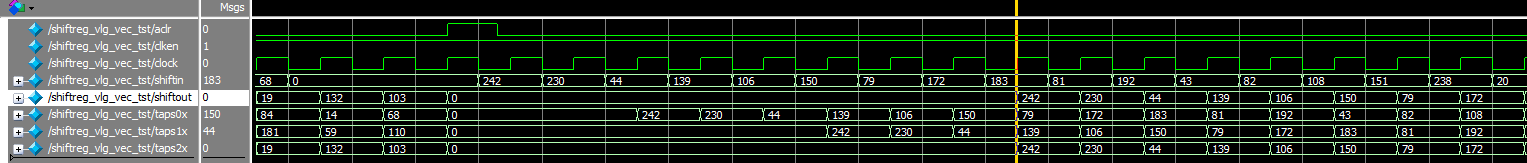

分析例子工程的仿真波形:

数据从shiftin端输入,等待12个数据输入完后,shiftout端口才开始输出数据。但是,最早的taps输出是在shiftin输入数据后的3个时钟。

如今,需要弄清楚的是为什么是12个数据输入完后,才开始输出数据,而不是等待9个,或者15个?

首先,更改distance between taps这一参数,更改为4:

然后将例子工程里面的testbench导入自己建的工程中,进行仿真:

首先,将shift Register里面的参数改为与例子工程里面相同的参数,8,4,3目的是为了验证仿真出来的波形是否与例子工程仿真出来的波形一致,即检验此testbench的有效性。

产生的波形与例子工程一样,可以继续使用。

更改参数后,生成的仿真波形为:

此种情况下,数据从shiftin端输入,等待16(4x4)个数据输入完后,shiftout端口才开始输出数据。但是,最早的taps输出是在shiftin输入数据后的4个时钟。

再次更改shift Register里面的参数:

得到仿真波形:

此种情况下,数据从shiftin端输入,等待24(4x6)个数据输入完后,shiftout端口才开始输出数据。但是,最早的taps输出是在shiftin输入数据后的4个时钟。

更改参数为:

但是modelsim启动不了?

原因:shift Register 的taps number 修改了,生成的.v文件的端口也更改了,相应的testbench文档中端口信号线也要做出相应的更改。

启动modelsim报错:

.v文件端口声明:

.vt文件端口声明:

更改.vt文件端口声明:

启动modelsim,得到波形:

验证了猜想:数据从shiftin端输入,等待9(3x3)个数据输入完后,shiftout端口才开始输出数据。但是,最早的taps输出是在shiftin输入数据后的3个时钟。

(完结)