阅读 ‘External Memory PHY Interface (ALTMEMPHY)’笔记

Posted on 2017-02-23 15:24 沉默改良者 阅读(376) 评论(0) 编辑 收藏 举报阅读 ‘External Memory PHY Interface (ALTMEMPHY)’笔记

1.PLL reference clock frequency

此处控制器输入时钟设置为100MHz,同样在顶层文件的代码中也有体现:

2.Memory clock frequency

此时钟是传给memory device的,根据需要在设备最大频率与最小频率之间的值。

3.关于phy_clk和reset_phy_clk_n这一对信号

3.关于phy_clk和reset_phy_clk_n这一对信号

控制器发送需要写入memory的数据,和接受从memory读取的数据,地址信号等都需要用时钟(phy_clk)。

4.关于memory burst length的设定

当controller data rate:half,local interface是memory data bus的四倍,如下图中:

当controller data rate:half,local interface是memory data bus的四倍,如下图中:

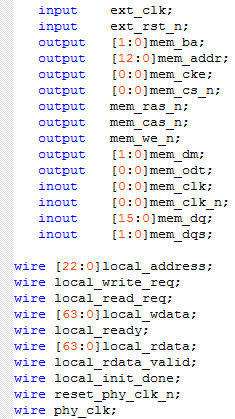

Inout [15:0]mem_dq;

wire [63:0]local_wdata;

wire [63:0]local_rdata;

当controller data rate:Full,local interface是memory data bus的2倍,如下图中:

当controller data rate:Full,local interface是memory data bus的2倍,如下图中:

inout [15:0]mem_dq;

input [31:0]local_wdata;

output [31:0]local_rdata;