第一个NIOS II工程using Qsys-------Let Qsys Say Hello

Posted on 2017-02-09 09:00 沉默改良者 阅读(415) 评论(0) 编辑 收藏 举报1.新建工程

2.添加原理图文件

注:似乎Nios II工程都需要涉及到原理图编程。

3.进入Qsys进行内核设计

注:启动Qsys后,系统已经为内核默认添加了一个组件clk_0。

4.设置时钟名字和频率

注:开发板上的时钟输入为50MHz。

5.添加Nios II核

注:选择Nios II Core 为:Nios II/f,其他选项卡均保持默认设置。

6.进行时钟连接操作

7.添加On-Chip-Memory(RAM)核

注:同时,需要设定片上内存大小,在此,我们设定为40960,即40KB,其他选项卡均保持为默认设置。

8.进行时钟,数据端口,指令端口的连接

注:关于数据和指令端口的连线规则,如果是存储器这类的IP核,需要将其Slave端口同Nios II的data_master和instruction_master相连,而其他非存储器IP核则只需连接到Nios II的data_master即可。

9.添加System ID Peripheral核

注:输入32 bit System ID号。

10.进行时钟,数据端口的连接

注:由于System ID Peripheral不为存储器设备,挂载在Nios II上时,只需要与data_master相连,不需要与instruction_master相连。

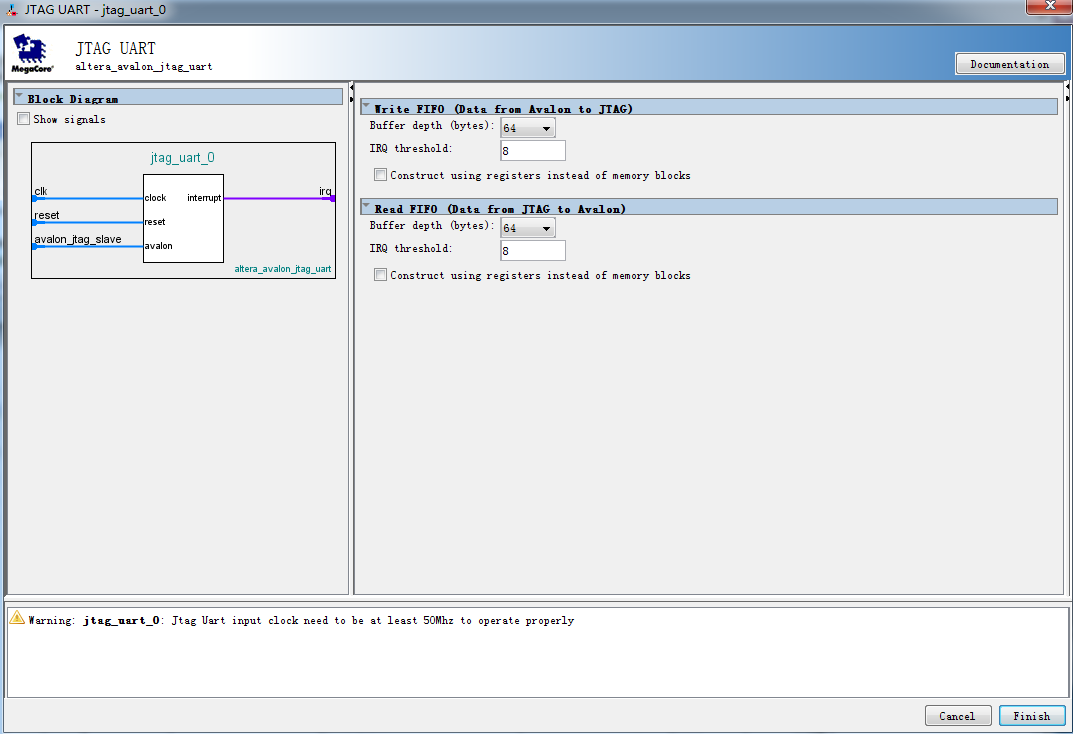

11.添加JTAG UART核

注:保持默认设置即可。

12.进行时钟,数据端口的连接

注:由于JTAG UART不为存储器设备,挂载在Nios II上时,只需要与data_master相连,不需要与instruction_master相连。

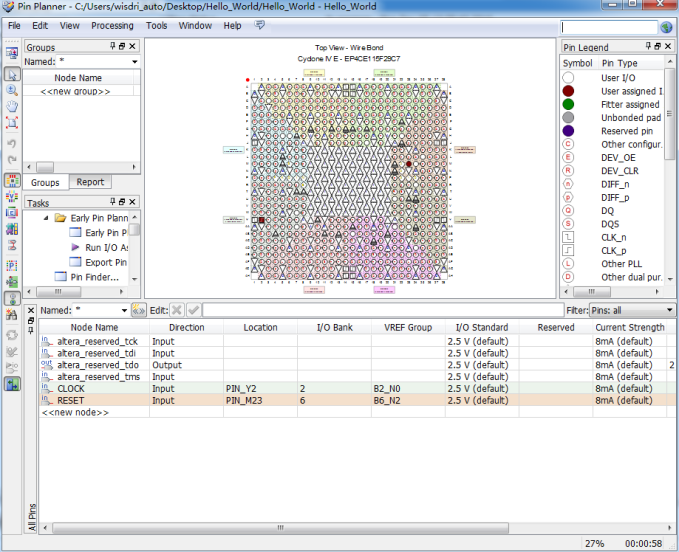

13.指定Nios II的复位和异常地址

配置Nios II Processor的Reset Vetor和Exception Vector为onchip_ram.s1。

14.连接复位信号

点击Qsys主界面菜单栏中的“System”下的“Create Global Reset Network”。

15.进行基地址分配

点击Qsys主界面菜单栏中的“System”下的“Assign Base Addresses”。

16.进行中断号的分配

17.生成Qsys系统

点击Generate HDL。

18.将配置好的kernel添加到原理图文件中

19.将IP文件添加到工程当中

20.添加锁相环

注:需要输入芯片速度等级与输入频率参数。

21.管脚生成

选中单个symbol,点击鼠标反键,单击Generate Pins for symbol ports。

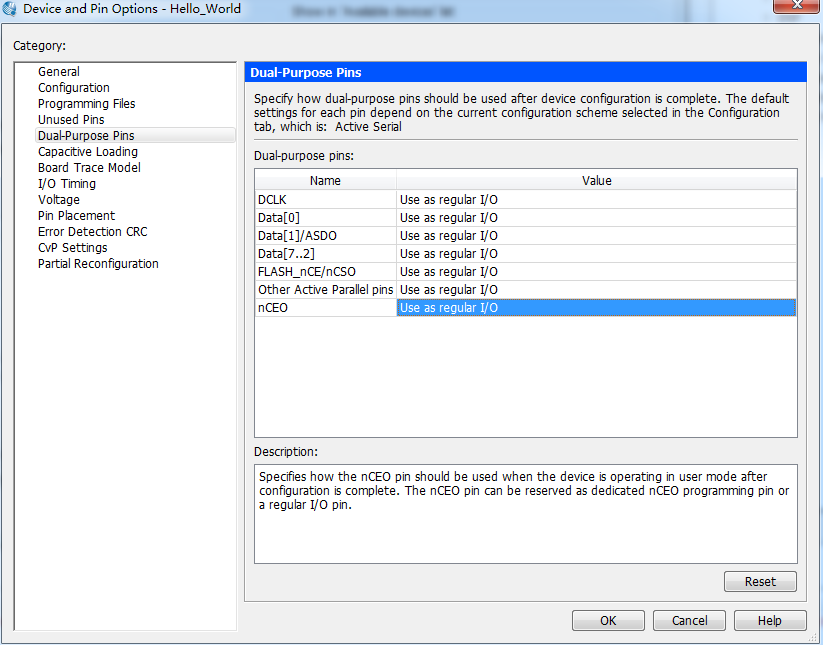

22.配置芯片

23.引脚分配

24.开启Eclipse

25.新建应用

File-New-Nios II Application and BSP from Template.

26.Build Project

27.运行程序

Run as ---- Nios II hardware