本文主要介绍了Lattice CPLD/FPGA集成开发环境的使用方法,并通过点亮开发板(Mach XO2 Breakout Board)上位号为D2的LED这一实例来演示其开发流程。

1.开发工具

Lattice CPLD/FPGA采用Diamond Design Environment,其初始化界面如下图所示,

2.新建工程

(1)在菜单栏中选择“File--New--Project”,弹出一个新建工程向导选项卡,单击“Next”。

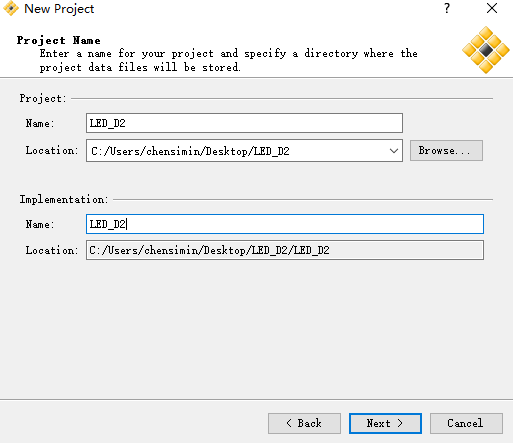

(2)在弹出的对话框中填入相应的信息,并单击“Next”。

Project Name:LED_D2

Location: C:/Users/chensimin/Desktop/LED_D2

Implementation Name: LED_D2

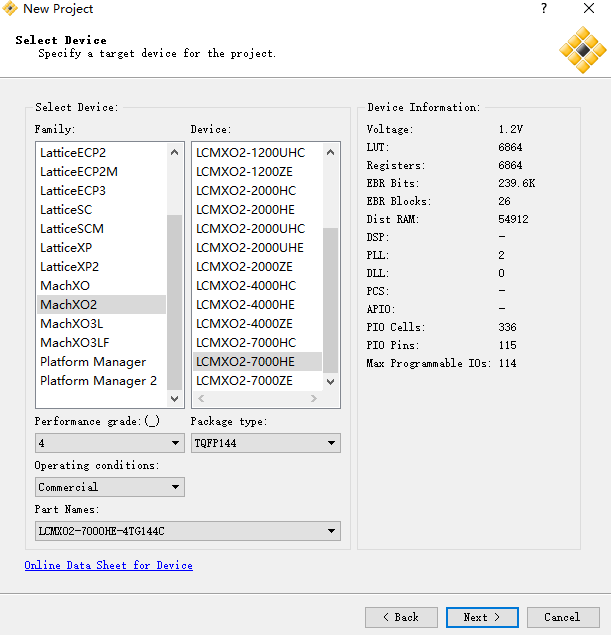

(3)选择相应的设备,本开发板中搭载的是MachXO2 LCMXO2-7000HE,设备选着完成后,单击“Next”。

(4)选择逻辑综合工具。本文选择Synplify Pro(Diamond开发环境已集成)综合工具,然后单击“Next”。

3.运用Verilog建模,实现功能

(1)新建工程文件列表如下图所示,其中只包含有“.lpf”文件,其作用是实现引脚分配功能。

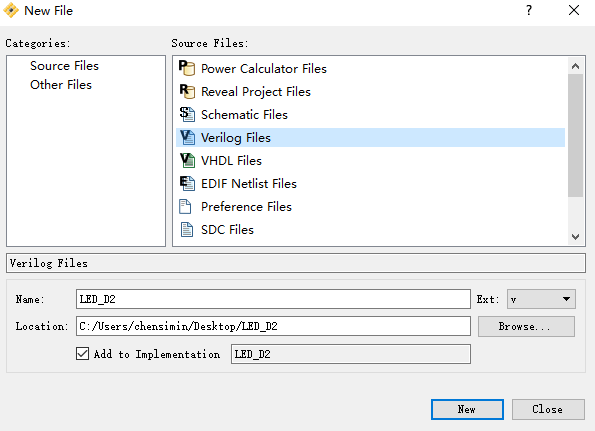

(2)新建,并编辑Verilog文件。单击菜单栏中的“File--New--File”,弹出新建文件选项卡,并完成相应的信息。

Source Files: Verilog Files

Name: LED_D2

LocationL: C:/Users/chensimin/Desktop/LED_D2

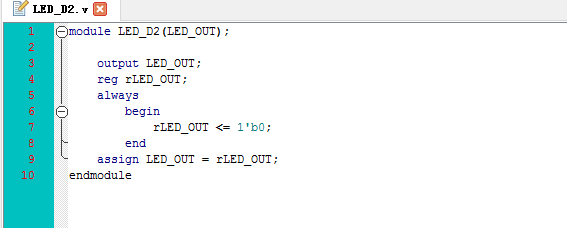

在文本编辑器中,编辑LED_D2.V文件。

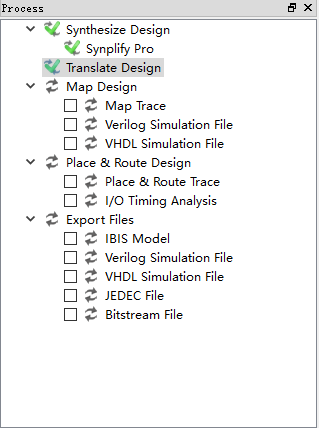

(3)逻辑综合,选择“Process view”,双击“Synthesize Design”,和“Translate Design”当逻辑综合完成后,会在相应的选项中出现绿色的钩。

(4)引脚分配,单击菜单栏中的“Tools --spreadsheet View”,出现如下选项卡。

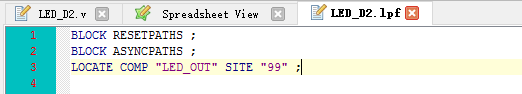

结合实际电路图,LED2与第99号管脚相连,则只需要在输出信号LED_OUT Pin一栏中填入99即可,同时“LED_D2.lpf”文件中,自动更新了引脚分配信息。

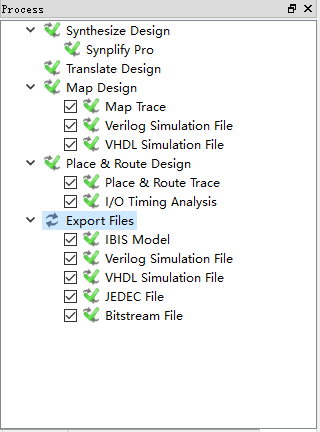

(5)生成烧写文件,依次双击“Map Design”,“Place&Route Design”,“Export Files”完成布线与JEDEC文件的输出。

4.下载程序

4.下载程序

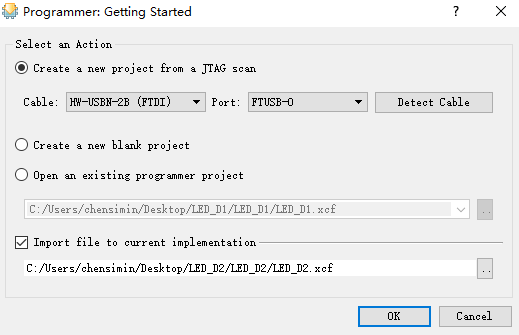

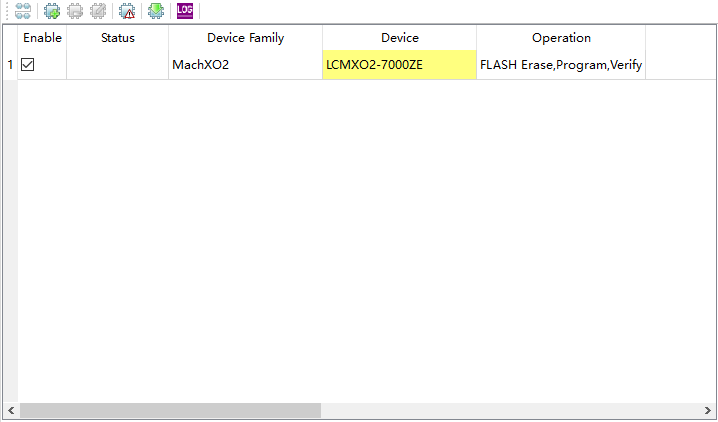

选择菜单栏中的“Tool--Programmer”,弹出如下图所示选项卡,并选择下载方式

Cable:HW-USBN-2B(FTDI)

Port: FTUSB-0

单击“OK”。

单击Program按钮,等待程序下载完成。

5.演示效果展示

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 10年+ .NET Coder 心语,封装的思维:从隐藏、稳定开始理解其本质意义

· .NET Core 中如何实现缓存的预热?

· 从 HTTP 原因短语缺失研究 HTTP/2 和 HTTP/3 的设计差异

· AI与.NET技术实操系列:向量存储与相似性搜索在 .NET 中的实现

· 基于Microsoft.Extensions.AI核心库实现RAG应用

· 10年+ .NET Coder 心语 ── 封装的思维:从隐藏、稳定开始理解其本质意义

· 地球OL攻略 —— 某应届生求职总结

· 提示词工程——AI应用必不可少的技术

· Open-Sora 2.0 重磅开源!

· 周边上新:园子的第一款马克杯温暖上架