PCIE背景知识学习(13)

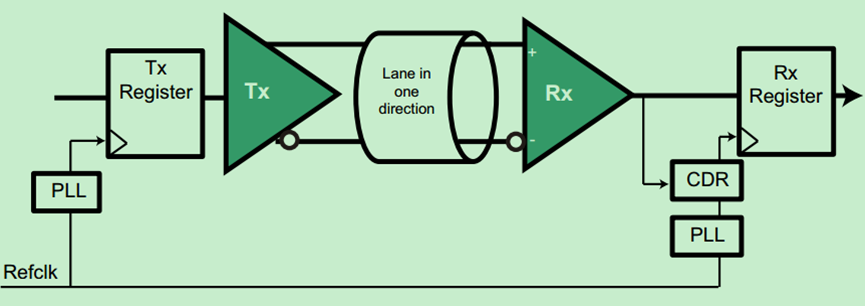

Common Refclk (Shared Refclk) Architecture

Common Refclk (Shared Refclk) Architecture的示意图如下图所示,

这种参考时钟架构是Spec推荐使用的,链路两端的器件均使用同一个参考时钟源。即使系统使用了带有扩频的参考时钟源,时钟抖动也只有-300~+2800ppm,这对于物理层中的RxCDR和TxPLL就比较友好了,可以降低RxCDR和TxPLL的复杂程度,达到节约成本的目的。

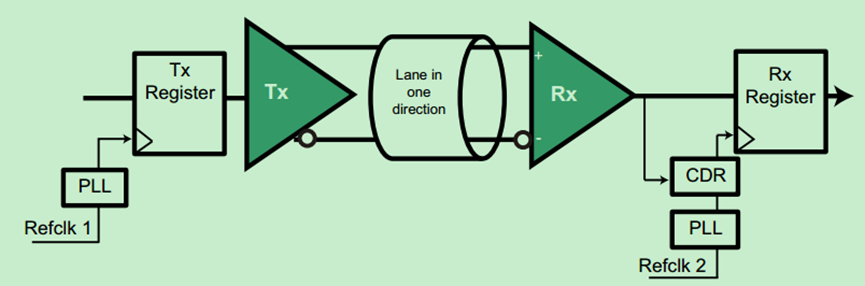

Data Clocked Rx Architecture

Data Clocked Rx Architecture的示意图如下图所示:

从示意图来看,这种参考时钟架构最为简洁,Rx端器件的CDR并不需要参考时钟,而是直接从数据流中恢复出时钟。不过这种结构的RxCDR几乎很少在FPGA的SerDes中使用,因为在没有外部参考时钟的协助下,CDR实现锁定都是一个很大的挑战,还要保证在5600ppm的抖动范围内不失锁(对于带有扩频时钟的PCIe链路来说)。

注:绝大部分的FPGA SerDes都是多协议SerDes,除了支持PCIe外,往往还需要支持其他主流的串行协议,比如SATA、USB、DisplayPort、HDMI、Ethernet (Q)SGMII、CoaXpress、CPRI、FPD-Link II/III、Serial RapidIO、SLVS-EC等等。这种参考时钟架构对于PCIe来说行得通,对于其他的某些串行协议来说可能是无法实现的。

Separate Refclk Architecture

Separate Refclk Architecture的示意图如下图所示:

PCIe Spec强烈不推荐使用这种参考时钟架构,尽管这是其提出的三种参考时钟架构之一。PCIe Spec强调,如果使用这种架构,扩频时钟必须被禁止使用(2.5GT/s & 5GT/s),因为这中情况下使用扩频时钟的话,CDR的带宽需甚至需要大于5600ppm,这对于CDR来说是非常大的挑战。

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 10年+ .NET Coder 心语 ── 封装的思维:从隐藏、稳定开始理解其本质意义

· 地球OL攻略 —— 某应届生求职总结

· 提示词工程——AI应用必不可少的技术

· Open-Sora 2.0 重磅开源!

· 周边上新:园子的第一款马克杯温暖上架

2017-09-29 SDRAM读写操作