PCIE背景知识学习(12)

LTSSM

PCIe总线中的链路初始化与训练(Link Initialization & Training)是一种完全由硬件实现的功能,处于PCIe体系结构中的物理层。整个过程由链路训练状态机(Link Training and Status State Machine,LTSSM)自动完成。

在系统复位后,会自动进行链路训练,以达成以下目标:位锁定(Bit Lock)、字符锁定(Symbol Lock,Gen1 & Gen2 Only)、块锁定(Block Lock,Gen3 Only)、确定链路宽度(Link Width)、通道位置翻转(Lane Reversal)、信号极性翻转(Polarity Inversion)、确定链路的数据率(Data Rate)和通道对齐(Lane-to-Lane De-skew)等功能。

首先是位锁定(Bit Lock):

前面的文章中提到过,PCIe总线采用了一种嵌入式时钟的机制,即发送端只向接收端发送数据信号,并不发送时钟信号(时钟信号隐藏在数据信号中)。接收端可以通过CDR(Clock and Data Recovery)逻辑将时钟从数据流中恢复出来,然后再用恢复出来的时钟对数据信号进行采样。当然,时钟恢复需要一定的时间,才能保证时钟信号与数据信号的相位对应关系符合要求。一旦CDR完成了时钟的恢复,我们就说PCIe总线完成了位锁定。

字符锁定(Symbol Lock):

完成了位锁定之后,只是能够准确地识别出数据流中的0和1,还是不知道发送的内容是个啥。对于Gen1&Gen2来说,采用的8b/10b编码,即传输的数据是以10bit为一个字符。LTSSM可以引导物理层相关逻辑通过识别COM(K28.5)等控制字符来确定每个字符的开始与结束为止,即字符锁定。

链路宽度(Link Width):

由于PCIe允许将x1的PCIe卡插入x4、x8甚至是x16的PCIe插槽中。因此在链路训练与初始化过程中,相邻的两个PCIe设备需要相互通信来确定其支持的最大链路宽度。

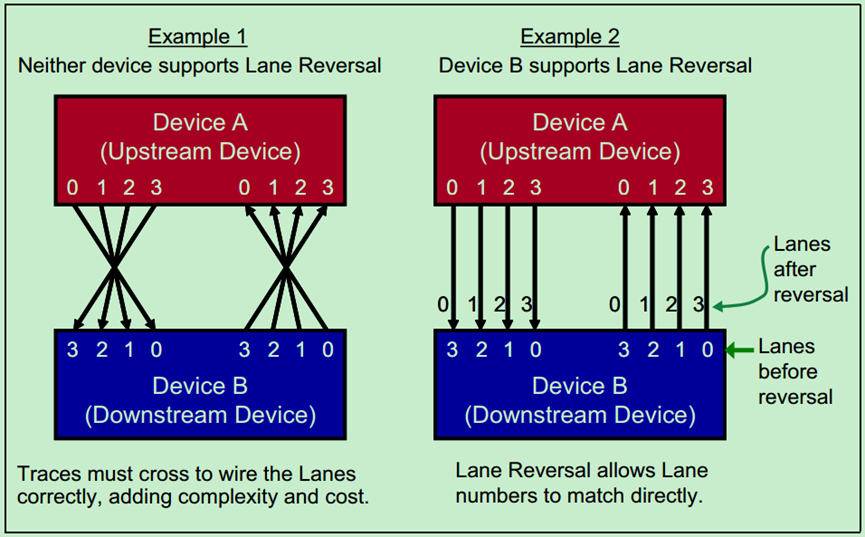

通道位置翻转(Lane Reversal):

有的时候两个PCIe设备的通道排列位置可能不太一致,PCIe Spec允许对默认的通道排列位置重新排列,如下图所示。但是,从大部分的PCIe设备(PCIe卡和插槽等)都是按照统一的标准实现的,一般不会出现这种情况,因此这一功能是可选的。

信号极性翻转(Polarity Inversion):

前面的文章中介绍过,PCIe收发的都是差分信号,有的时候Link两端的设备的对应信号的极性可能是相反的。因此,PCIe Spec允许在链路训练与初始化的时候,对其进行调整,如下图所示。和通道位置翻转(Lane Reversal)不一样的是,信号极性翻转(Polarity Inversion)并不是一个可选项,而是所有标准PCIe设备都应支持的。

链路的数据率(Data Rate):

系统刚复位的时候,链路训练和初始化都是基于2.5G T/s的速率的。如果Link两端的设备都支持更高的速率,则会自动进入Re-training状态,以重新切换速率。

注:PCIe Spec规定,高速率的PCIe设备必须能够向下兼容。即Gen2必须同时支持2.5G T/s和5G T/s。

通道对齐(Lane-to-Lane De-skew):

PCIe链路完成字符锁定后,还需要进行通道对齐。因为有的通道的信号可能先到达,有的可能后到达。PCIe Spec规定PCIe链路应有能力对一定范围了的Lane-to-Lane Skew进行移除,使得各个Lane上的信号是同步的。

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 10年+ .NET Coder 心语 ── 封装的思维:从隐藏、稳定开始理解其本质意义

· 地球OL攻略 —— 某应届生求职总结

· 提示词工程——AI应用必不可少的技术

· Open-Sora 2.0 重磅开源!

· 周边上新:园子的第一款马克杯温暖上架

2017-09-29 SDRAM读写操作