PCIE背景知识学习(9)

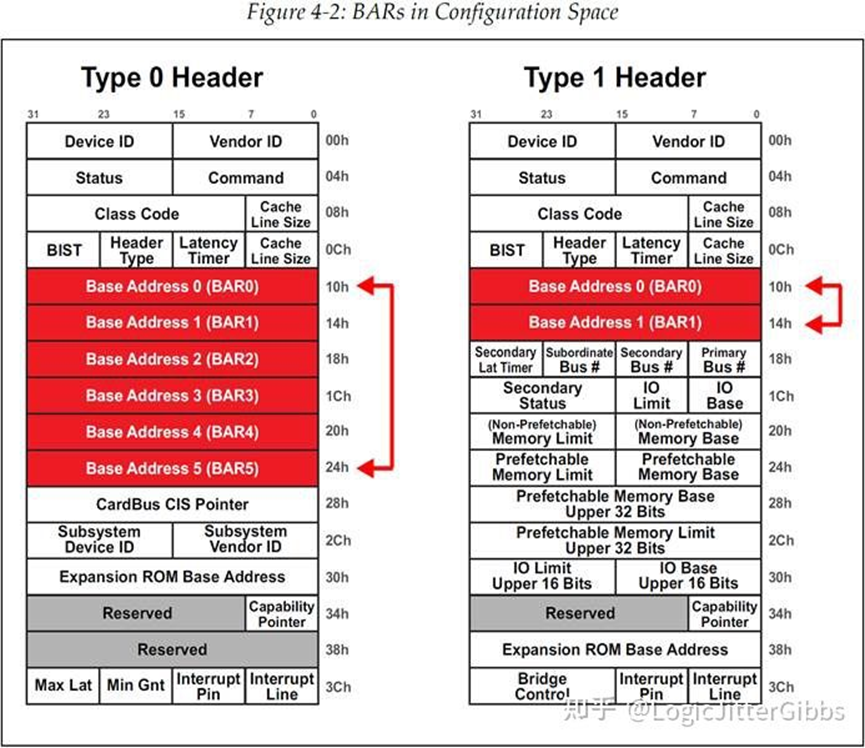

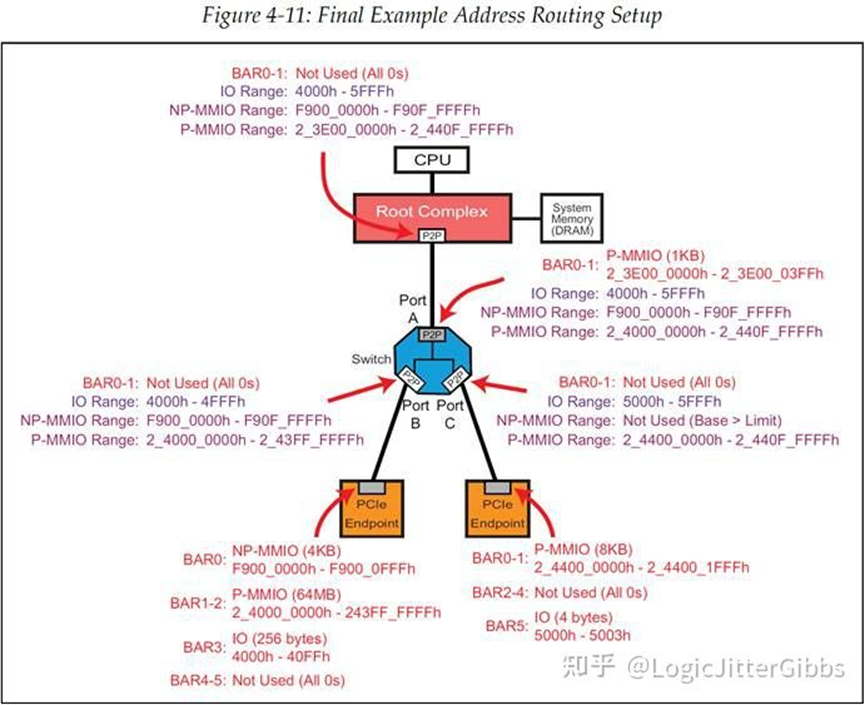

为了确保你已经理解了设置建立BARs和Base/Limit寄存器的规则和方法,请仔细查看图 4‑11,以保证你对它们的正确认知。我们简单的对示例系统进行了扩展,在Switch的Port A下方加入了另一个EP以及它所请求的地址空间。要记得,Type 1 Header中也含有2个BAR,它们也可以请求地址空间。而一个Bridge的Base/Limit寄存器表示的地址空间范围并不包括Bridge自身的BAR所请求的地址空间,也就是说Base/Limit寄存器只表示Bridge下方存在的地址空间。

浙公网安备 33010602011771号

浙公网安备 33010602011771号