PCIE背景知识学习(2)

PCI中断处理(PCI Interrupt Handling)

PCI设备使用4个边带信号(sideband)作为中断信号,分别为INTA#、INTB#、INTC#、INTD#,并从中选取一个来向系统发送中断请求,即使用4个中断信号中的1个来发送中断请求。当其中一个中断引脚被置为有效时,单CPU系统的中断控制器将会对中断作出响应,相应的方式为将INTR(interrupt request)信号置为有效,将中断请求发送给CPU。

后来出现的多CPU系统不再适用这种单信号线输入作为中断的方式,因此进行了改进,将中断改为了APIC(Advanced Programmable Interrupt Controller)模型,在这种模型中中断控制器将会向多CPU发送报文(message)而不是向其中一个CPU发送INTR信号。不过无论中断传输模型是什么,接收到中断的CPU都必须确认中断来源,然后为中断提供服务。

PCI错误处理(PCI Error Handling)

PCI自身并不包含任何的自动的或是基于硬件的错误恢复机制,因此软件将完全负责去进行错误处理。

PCI地址空间映射(PCI Address Map)

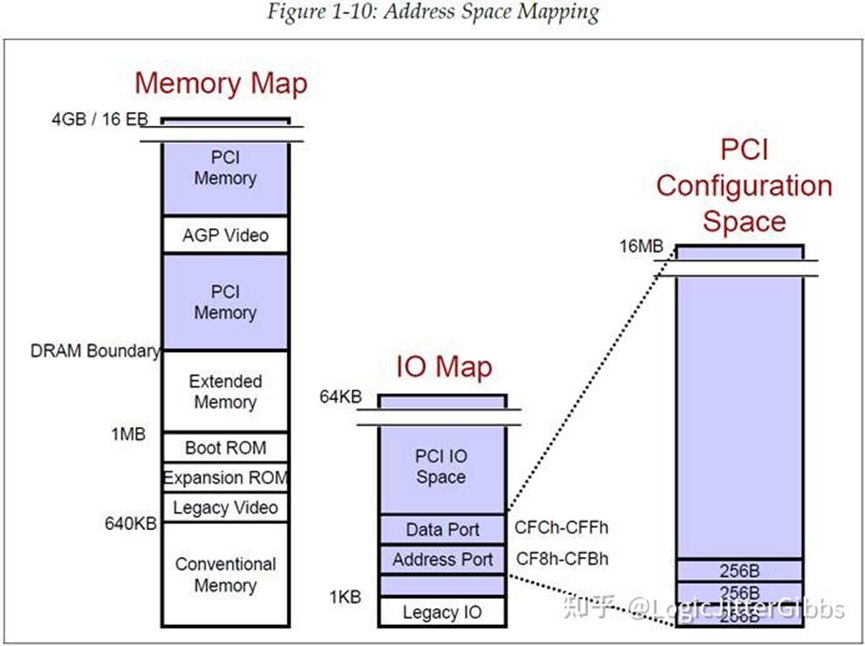

PCI体系结构支持3种地址空间,包含:Memory(内存)、I/O、Configuration Address Space(配置地址空间)。

x86处理器可以直接访问Memory和I/O空间。一个PCI设备映射到处理器内存地址空间,可以支持32或64位寻址。

在I/O地址空间,PCI设备可以支持32位寻址,但是因为x86 CPU仅使用16位的I/O地址空间,所以许多平台都会将I/O空间限制在64KB(对应16bit)。

PCI还引进了第三种地址空间,称为配置空间,CPU只能对它进行间接访问而非直接访问。

PCI设备中的每个Function(功能)都包含专为配置空间所准备的内部寄存器,这些寄存器对于软件来说是可见的,并且软件可以通过一个标准化的方式来控制它们的地址与资源,这为PC提供了一个真正的即插即用(plug and play)的环境。

每个PCI Function最多可以有256 Bytes的配置地址空间。考虑到PCI最多可支持单个设备含有8个Function、每路总线含有32个设备、单个系统包含256路总线,那么可以得到一个系统的配置空间总量为:

256B/Function *8Function/device * 32devices/bus *256buses/system =16MB,

即一个系统的配置空间总大小为16MB。

因为x86 CPU无法直接访问配置空间,所以它必须通过IO寄存器进行索引(然而在PCI Express中引入了一种新方法来访问配置空间,这种新方法是通过将配置空间映射入内存地址空间来完成的)。

使用了一种被称为配置地址端口(Configuration Address Port)的IO端口,它位于地址CF8h-CFBh;还使用了一种被称为配置数据端口(Configuration Data Port)的IO端口,它位于地址CFCh-CFFh。

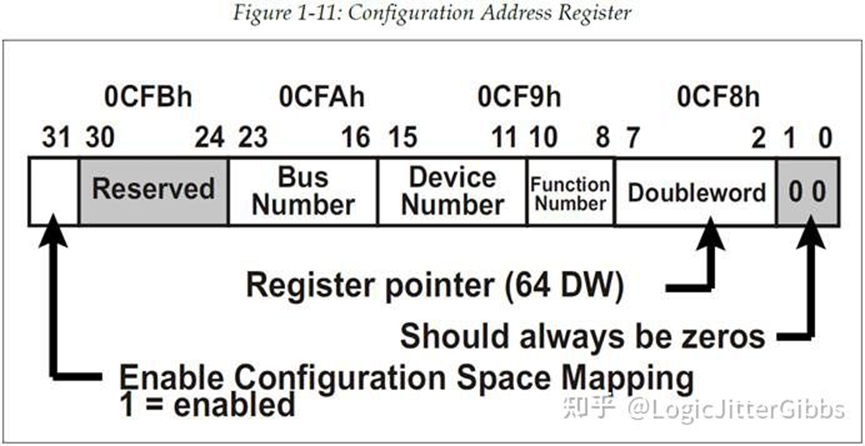

第一步:CPU产生一个IO写,写入的位置为北桥中IO地址为CF8h的地址端口(Address Port),这样就给出了需要被配置的寄存器的地址,即“用一个寄存器来指向一个内部位置”。这个地址主要由三部分组成,通过这三部分就可以定位一个PCI Function在拓扑结构中的位置,它们为:在256条总线中我们想访问哪一条总线、在该总线上的32个设备中访问哪一个、在该设备的8个Function中访问哪一个。除了这些以外,唯一还需要提供的信息是要确认访问这个Function的64dw(256Bytes)中的哪个dw。

第二步:CPU产生一个IO读或者IO写,操作的位置为北桥中的地址为CFCh的数据端口(Data Port),即“用另一个寄存器来进行数据的读取或写入”。在此基础上,北桥向PCI总线发起一个配置读事务(configuration read)或配置写事务(configuration write),事务要操作的地址即为步骤一中地址端口中所指定的地址。

每个PCI Function可以包含最多256Bytes的配置空间。这个配置空间起始的64Bytes包含一个被称为Header(配置空间头)的结构,剩余的192Bytes用来支持一些其他可选功能。系统配置首先由Boot ROM固件来执行,在操作系统被加载完成后,它将重新对系统进行配置,重新进行资源分配。这也就是说系统配置的过程可能会被执行两次。

根据Header的类型,PCI Function被分为两个基本的类别。第一种Header称为Type 1 Header(类型1),它用于标识这个Function是一个Bridge,Bridge将会在拓扑结构上创建另一条总线。

而Type 0 Header(类型0)就是用来指示这个Function不是一个Bridge. 关于Header类型的信息包含在dword3的字节2的同名字段中(Class Code字段),当软件在系统中发现某个Function时,第一件事就是要检查其Header的这个字段(软件发现系统中Function的过程称为枚举enumeration)。

PCI配置Header Type 1(Bridge)

PCI配置Header Type 0(非Bridge)

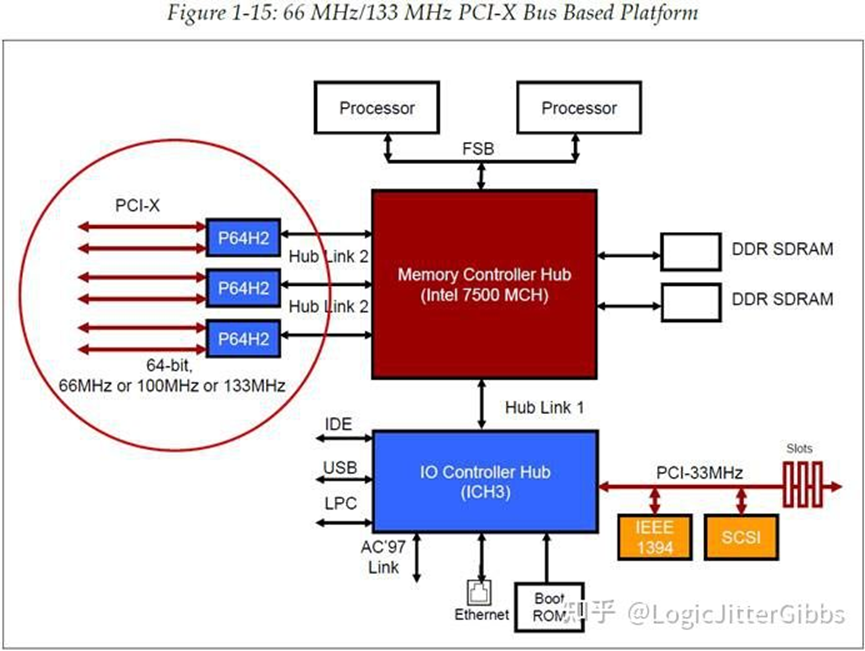

PCI-X系统示例(PCI-X System Example)

一个基于Intel 7500服务器芯片组的系统平台。

需要注意的是,PCI-X并不允许在第一个数据阶段(first data phase)后插入等待态。之所以这样做是因为PCI-X中会在事务的属性阶段(Attribute Phase),将需要传输的数据总量告诉Target设备。因此与PCI不同,Target是知道自己需要传输多少数据的。此外,多数PCI-X总线时序周期是连续的,因为使用的是突发模式,并且数据通常以128Bytes作为一个数据块(block)来进行传输。这些特性使得总线利用率提高,同时也提高了设备buffer管理的效率。

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 10年+ .NET Coder 心语 ── 封装的思维:从隐藏、稳定开始理解其本质意义

· 地球OL攻略 —— 某应届生求职总结

· 提示词工程——AI应用必不可少的技术

· Open-Sora 2.0 重磅开源!

· 周边上新:园子的第一款马克杯温暖上架

2018-09-26 阅读ug949-vivado-design-methodology笔记

2017-09-26 VTC Fsync_out信号分析