Versal NOC 精读

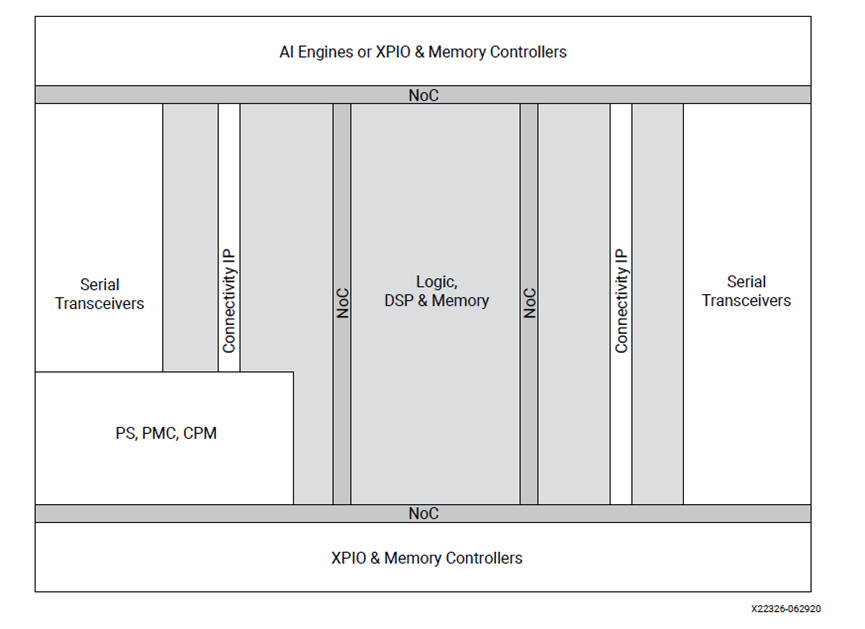

1.The NoC converts these AXI interfaces to a 128-bit wide NoC packet protocol that moves data horizontally and vertically across the device via the horizontal NoC

(HNoC) and vertical NoC (VNoC) respectively

自己会封装包协议。

2.

The XPIO in Versal ACAPs are similar to the high-speed I/O (HPIO) in the UltraScale™

architecture.

The XPHY logic is used for the integrated DDRMC, soft memory controllers, and custom high-performance I/O interfaces.

3.DDRMC

The controller operates at half the DRAM clock frequency and supports DDR4, LPDDR4, and LPDDR4X standards up to 4266 Mb/s.

The controller can be configured as a single DDR memory interface with data widths of 16, 32, and 64 bits, plus an extra 8 check bits when error-correctio code (ECC) is enabled.

The controller can also be configured as 2 independent or interleaved DDR interfaces of 16 or 32 data bits each.

It is shared between the PS and PL via the device-wide, high-performance NoC interface.

The NoC IP core can be configured to include one or more integrated DDRMCs.

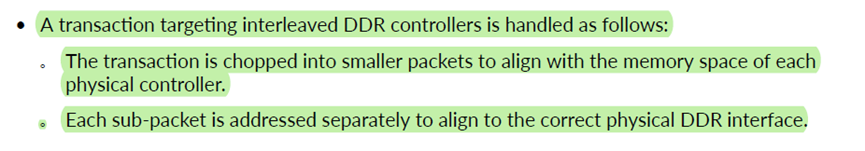

If two or four DDRMCs are selected, the DDRMCs are grouped to form a single interleaved memory.

In interleaved mode, the application views the

participating DDRMCs as a single unified block of memory. The NoC supports interleaving across two or four DDRMCs by automatically dividing AXI requests into interleaved, block-sized subrequests and alternately sending the subrequests to each of the participating DDRMCs.

留下一个问题:

DDRMC 的 interleaved 模式是怎么工作的。

Interleaved 其实是AXI的一种工作模式吗?

需要查阅 DDRMC 的手册,以及AXI协议手册。

Vivado Design Suite: AXI Reference Guide (UG1037).

Versal 开发过程中的仿真:

Vivado Design Suite User Guide: Logic Simulation 关注Xilinx 提供的仿真模型

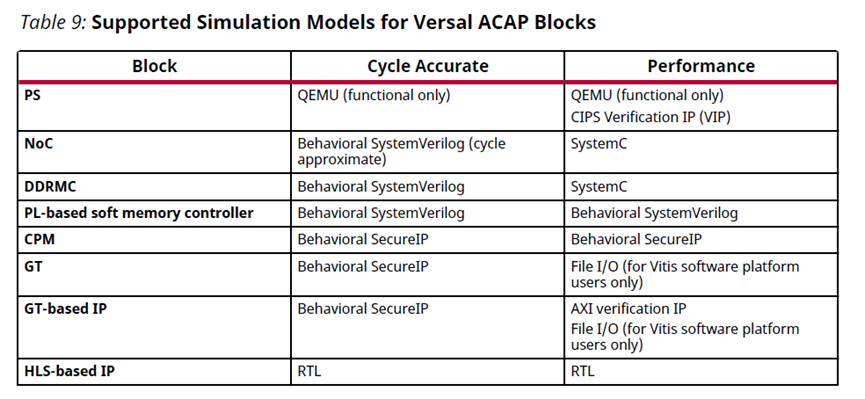

To improve simulation performance, you can replace some Versal ACAP IP blocks with SystemC transaction-level models, which simulate faster but are no longer cycle-accurate. The purpose of this simulation is to verify and debug detailed hardware functionality before implementing the design on the device.

RTL仿真模型精确到每一个时钟周期,数据传输以及时序仿真更加适合使用。

SystemC仿真模型更加适用于分析,与架构设计。

NOC 没有复位信号,需要通过PMC来进行复位。怎么来控制,需要进一步研究。

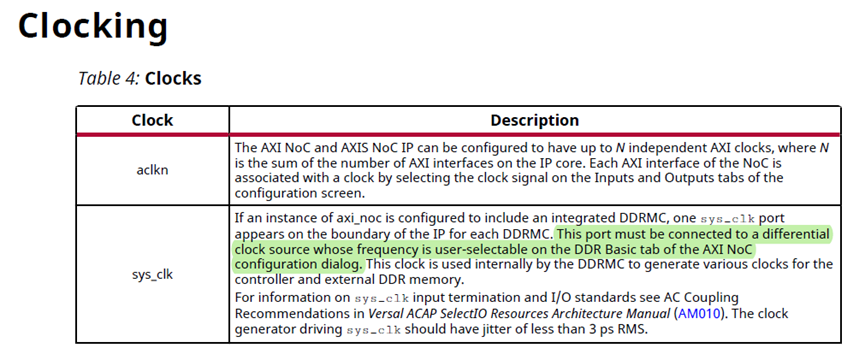

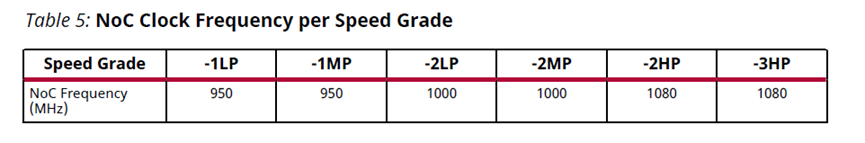

时钟频率:

AXI ID:

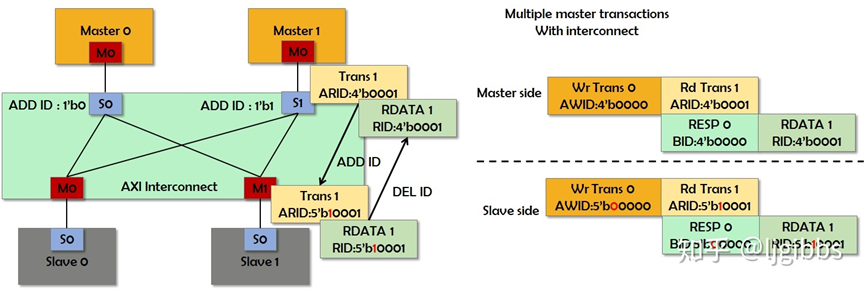

关于基于AXI ID 的传输实现框图:

AXI 协议采用的方法,中间节点指 AXI Interconnect 组件。从场景 B 的拓扑连接可以发现两点:

任何主机的事务前往任何从机必定经过 interconnect

Interconnect 可以从事务的来源端口,判断事务来自哪台主机

具体的实现方式是,Interconnect 接收主机事务后,会在原有的 ID 上附加一个表示来源端口的值,再发送给从机。对于从机返回的数据,Interconnect 再剥去附加值后再返回主机。

这样一来对于属于不同主机的事务,哪怕主机发出时的 ID 一致,从机看到的 ID 总是不同的。

接下来我们基于场景 B 构造一个例子 B1 来说明 Interconnect 的工作。

图中的 AXI Interconnect 连接有 2 个主机,因此可通过 1bit 额外 ID 来区分这两个主机。master1 产生的 trans1 原 ARID 为 4'b0001,自端口 S1 输入,Interconnect 为其增加额外 ID:1'b1 后,从机端看到的 ARID 为 5'b10001。从机读数据 RID 匹配为 5'b10001,Interconnect 去除额外比特后返回 master1。

右图中的传输过程分别包括一个读写事务。其中,写事务经过 Interconnect 的 ID 调整机制与读事务基本相同,不同在于从机返回的是写回复,相应 ID 为 BID。

自然,从机端 ID 位宽需要设置地比主机端 ID 位宽更大。协议建议(而非强制):

主机端位宽不超过 4bit,Interconnect 为主机事务增加的 ID 位宽不超过 4bit

因此从机端的 ID 位宽不超过8bit

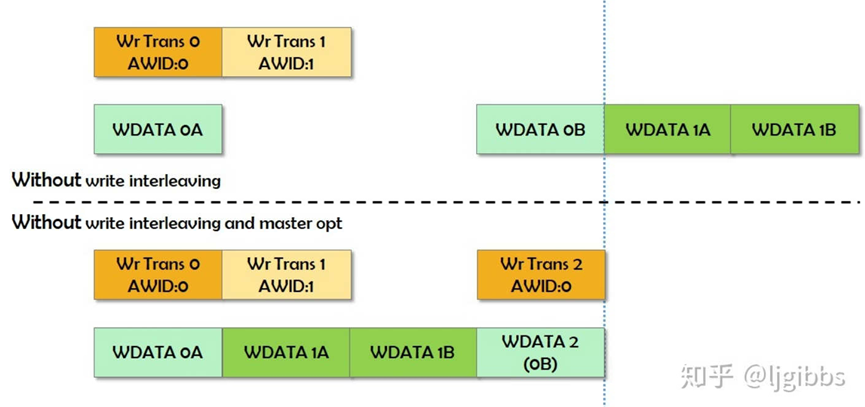

AXI4 不再支持写交织功能

在 AXI3 协议中支持的写数据交织(wirte data interleaving)功能在 AXI4 中不再支持。因此 Interconnect 实现也无需继续支持写交织。

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 10年+ .NET Coder 心语 ── 封装的思维:从隐藏、稳定开始理解其本质意义

· 地球OL攻略 —— 某应届生求职总结

· 提示词工程——AI应用必不可少的技术

· Open-Sora 2.0 重磅开源!

· 周边上新:园子的第一款马克杯温暖上架

2017-09-21 阅读<SMPTE 274M-2005 1920X1080>笔记