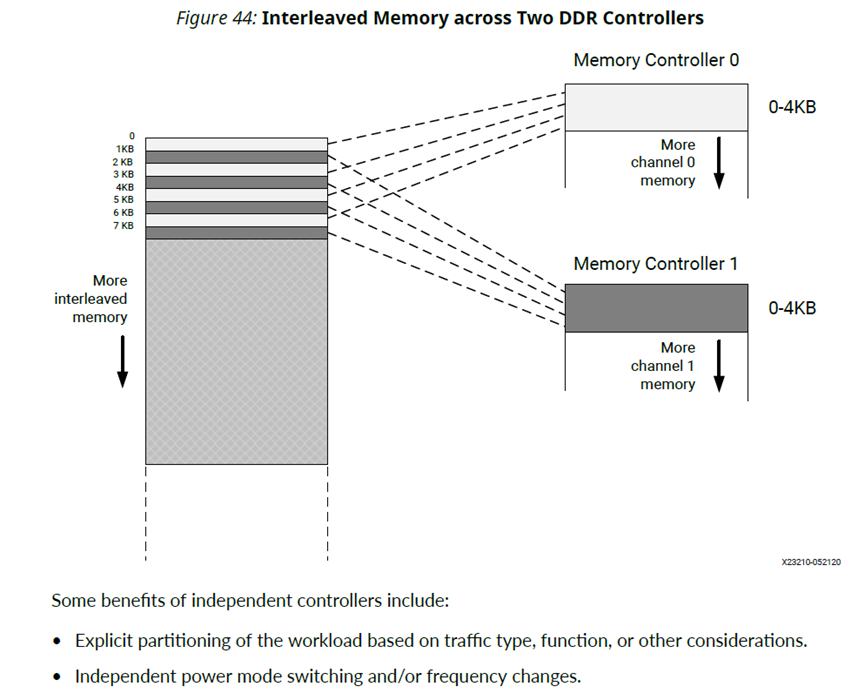

DDR Controller interleaving

AXI(Outstanding、Out-of-Order、Interleaving)

Outstanding:master 不必等待命令执行结束就可以发送下一命令

Out-of-Order:对于相同ID的指令,必须要顺序完成;对于不同ID的指令,可以乱序完成。

Interleaving:乱序传输时不同ID之间的数据可以内插,但是要保证每个ID的数据顺序。

Outstanding是指正在进行中的,未完成的,形象表达就是说“在路上”。相比于正常情况下的主机和从机的读写操作,如果outstanding能力N>1,写操作:主机可以连续发出N组写地址和写数据,

这期间如果没有写响应返回,则等待,如果有写响应返回,则返回了几个就可以接着发几组。也就是说在路上的写响应最多是N。对于读操作是同样的道理。

当一个master向一个或多个slave发出数据块读/写请求时,AXI总线要求在同一个数据块内,每一个数据的读/写的完成必须按照顺序。但数据块之间,或读取与写入之间,

AXI总线并不要求完成读/写的顺序与发出读/写请求的顺序保持一致,也就是允许读/写事务的乱序(Out-of-Order)。AXI总线的每个通道上的每一个读/写请求、数据结果,

以及写入回应都包括一个4bit的读/写事务识别序号ID[3:0]。根据识别序号,主控模块可以辨别接收到的读取数据或是写入回应与发出的读/写请求之间的对应关系。

不同ID的数据可以内插(Interleaving),通过ID号可以对数据进行识别。

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 10年+ .NET Coder 心语 ── 封装的思维:从隐藏、稳定开始理解其本质意义

· 地球OL攻略 —— 某应届生求职总结

· 提示词工程——AI应用必不可少的技术

· Open-Sora 2.0 重磅开源!

· 周边上新:园子的第一款马克杯温暖上架

2017-08-02 手动按键复位程序(包含按键消抖)