我要做CPU_2

1.aou_top.v文件分析

内部有如下三大模块

2.gpio0_sec_top.v文件分析

我们先从一个看似最简单的模块来分析

没想到这个最简单的模块里面就嵌套了这么多的子模块

3.gpio_ctrl.v文件分析

这个模块里面,才开始接触到真正的逻辑,真是埋得太深了。

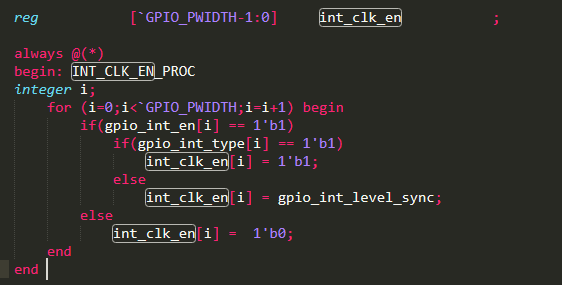

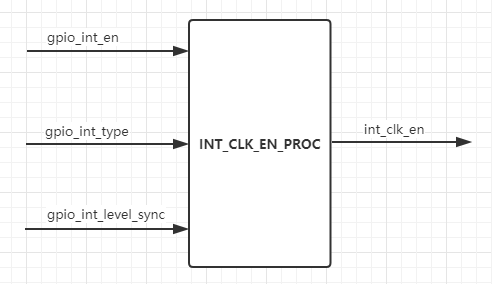

3.1时钟使能信号的生成

这样的时钟使能信号并行的有GPIO_PWIDTH个,此信号的生成受到gpio_int_en信号和gpio_int_type信号的控制。

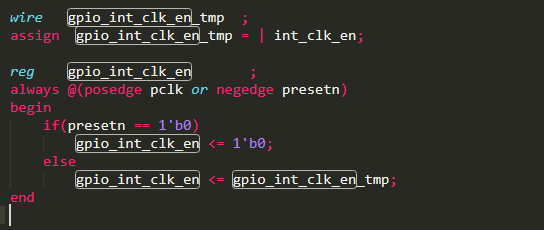

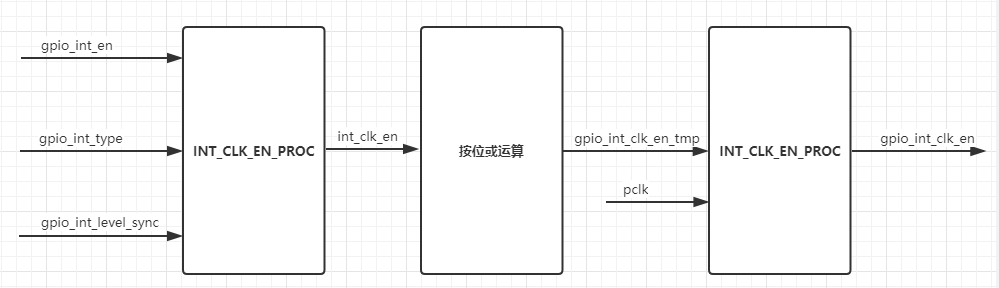

3.2 gpio时钟使能信号

此处首先是检测前端int_clk_en信号中,有没有哪个端口为1或者说是被使能的情况,获得的gpio_int_clk_en_tmp信号需要经过pclk时钟的同步,得到gpio_int_clk_en信号,即gpio时钟使能信号。

gpio的时钟使能信号是由gpio的使能信号和type等信号共同决定的。

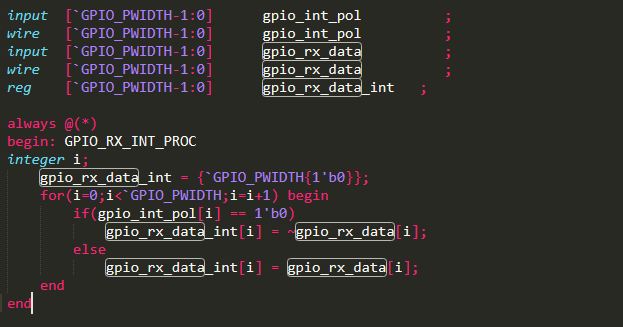

3.3 gpio接收数据

外部输入的数据gpio是直接接收,还是按位取反后接收,需要由gpio_int_pol信号来控制。