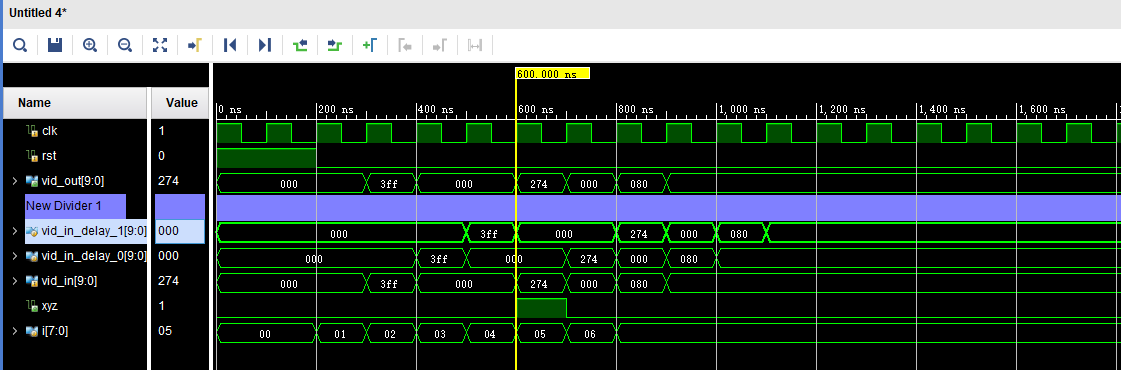

视频信号中xyz的提取

`timescale 1ns / 1ps ////////////////////////////////////////////////////////////////////////////////// // Company: // Engineer: chensimin // // Create Date: 2019/01/15 11:52:24 // Design Name: // Module Name: detect_video // Project Name: // Target Devices: // Tool Versions: // Description: // // Dependencies: // // Revision: // Revision 0.01 - File Created // Additional Comments: // ////////////////////////////////////////////////////////////////////////////////// module detect_video( input wire clk, input wire rst, output reg [9:0] vid_out = 0 , output wire xyz ); //------------------------------------------------------------------ reg [7:0] i = 0; always @(posedge clk or posedge rst) begin if(rst) begin i <= 0; vid_out <= 10'h000; end else begin case(i) 0: begin i <= i + 1'b1; vid_out <= 10'h000; end 1: begin i <= i + 1'b1; vid_out <= 10'h3FF; end 2: begin i <= i + 1'b1; vid_out <= 10'h000; end 3: begin i <= i + 1'b1; vid_out <= 10'h000; end 4: begin i <= i + 1'b1; vid_out <= 10'h274; end 5: begin i <= i + 1'b1; vid_out <= 10'h000; end 6: begin i <= i + 1'b1; vid_out <= 10'h080; end default: begin i <= i; vid_out <= 10'h000; end endcase end end detect_xyz U0 ( .clk(clk), .rst(rst), .vid_in(vid_out), .xyz(xyz) ); endmodule /* add_force {/detect_video/clk} -radix hex {1 0ns} {0 50000ps} -repeat_every 100000ps add_force {/detect_video/rst} -radix hex {1 0ns} {0 200ns} */

`timescale 1ns / 1ps ////////////////////////////////////////////////////////////////////////////////// // Company: // Engineer: chensimin // // Create Date: 2019/01/15 13:30:22 // Design Name: // Module Name: detect_xyz // Project Name: // Target Devices: // Tool Versions: // Description: // // Dependencies: // // Revision: // Revision 0.01 - File Created // Additional Comments: // ////////////////////////////////////////////////////////////////////////////////// module detect_xyz ( input wire clk, input wire rst, input wire [9:0] vid_in, output reg xyz ); //------------------------------------------------------------------ reg [9:0]vid_in_delay_0 = 0; reg [9:0]vid_in_delay_1 = 0; reg xyz = 0; always @(posedge clk or posedge rst) begin if(rst) begin vid_in_delay_0 <= 10'h000; vid_in_delay_1 <= 10'h000; end else begin vid_in_delay_0 <= vid_in; vid_in_delay_1 <= vid_in_delay_0; if( vid_in_delay_1 == 10'h3FF && vid_in_delay_0 == 10'h000 && vid_in == 10'h000) xyz <= 1; else xyz <= 0; end end endmodule

仿真结果: