Artix-7 50T FPGA试用笔记之Create a simple MicroBlaze System

前言:之前笔者的试用博文提到安富利这块板子非常适合MicroBlaze开发,同时网上关于MicroBlaze的资料非常少(或含糊不清),没有一篇能完整介绍VIVADO SDK的设计流程,所以笔者带来这篇博文以供参考。

实验平台:Avnet-Artix-7 50T 开发套件/其它硬件也可以

EDK:Vivado 2015.2

SDK:Xilinx SDK 2015.2

实验内容:创建一个简单的MicroBlaze,实现板上LED流水灯和串口功能。

实验步骤:

(一) EDK部分

1. VIVADO下创建一个空工程。

2. IP Integrater -> Create Block Design

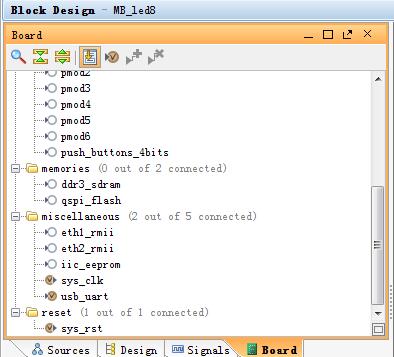

3. 框图内添加IP,such as MicroBlaze IP。使用Avnet-Artix-7 50T 开发套件双击Board

中器件即可。非该套件使用者,需要右击Diagram->ADD IP ->AXI Uartlite |AXI GPIO。需要双击IP设置对应波特率和GPIO_LED的位数。

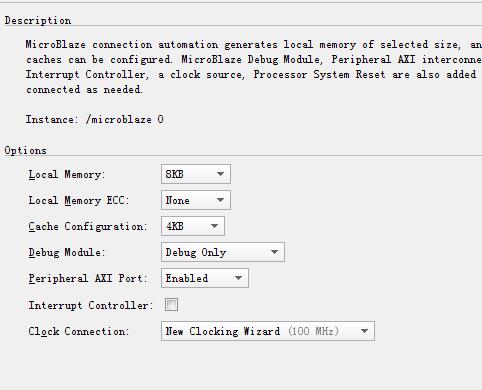

4. 点击 Run Block Automation

5. 点击 Run Connection Automation

——将剩下的线连上,时钟都接100MHz,非开发板用户功能都设置为custom。

注意:rst复位信号,Active High or Low根据自己开发板来定。

最终的Diagram如下图所示:

6. 点击VIVADO工具栏 Validate Design按钮(或按F6),编译设计时候正确。

7. 右击Design Sources栏中 .bd文件,Generate Output Product。

8. Creator HDL wrapper。//Let Vivado auto……

9. Synthesis -> Implementation -> Generate Bitsteam

10. File -> Export Hardware //include bitstream 勾打上,location 随意。

至此,FPGA软核系统包括所需外设电路驱动都搭好了,EDK部分至此结束。

(二) SDK部分

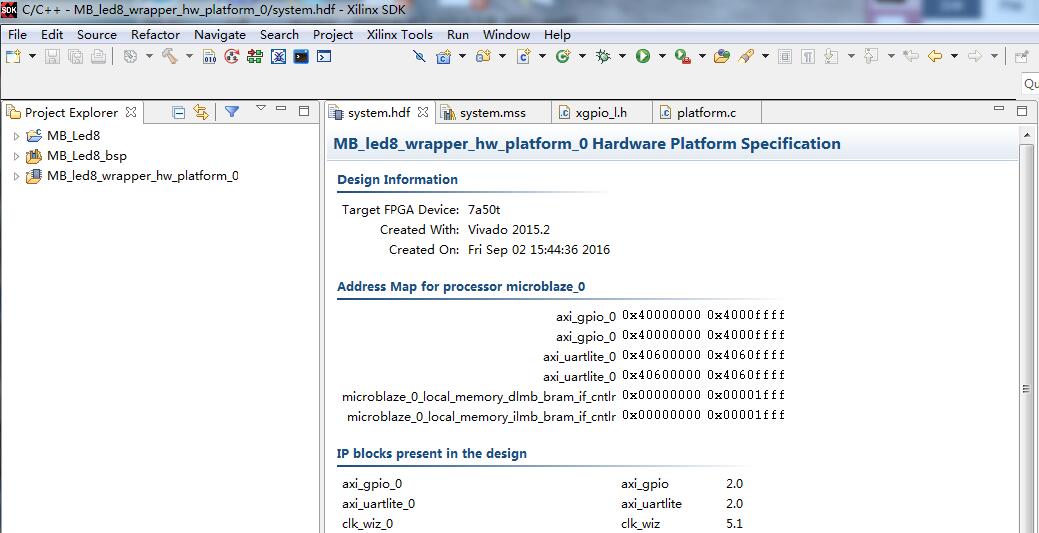

1. File -> Launch SDK。

SDK界面如上图所示,这是笔者SDK Application建立好之后界面,不过也差不多。

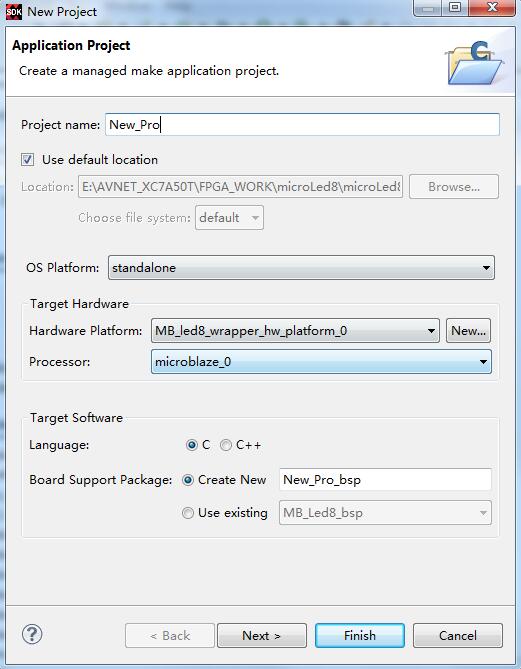

2. File -> New

Project Name 随意起个,点击next,选择Hello World模板,Finish。

这里模板已经写好了串口的初始化和打印部分,我们在添加上流水灯部分就OK了。

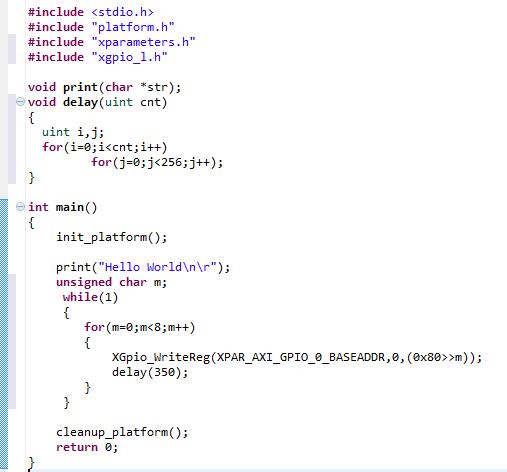

完整程序如上图所示,需要添加两个头文件,分别包含了外设器件的地址和操作GPIO的库函数。有Keil或其他编程经验的都可以看懂。

3. 工具栏 Xilinx Tools –> Program FPGA

4. 右击 左侧New_Pro选择RUN As -> 1….. //笔者这里选择的是第一个

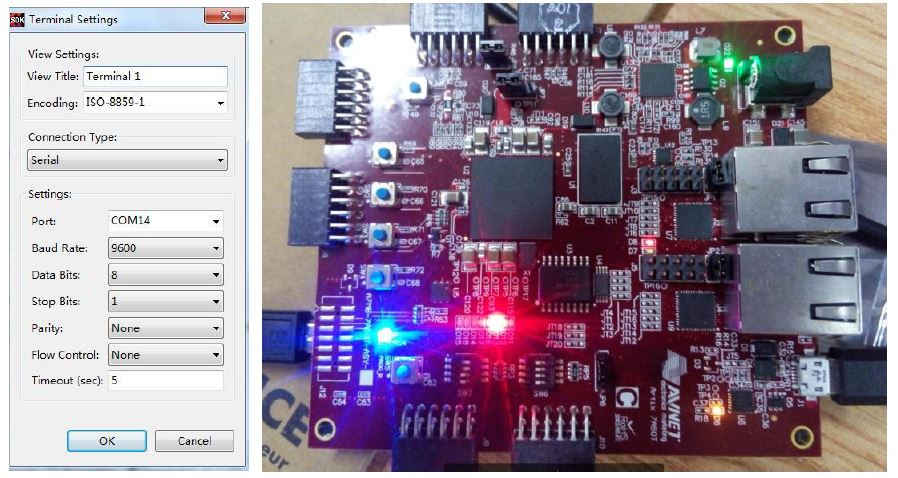

实验结果如下图所示: //注意的是串口的设置不要错

总结:本文实现的功能是很简单的,主要是让大家体会MicroBlaze设计的流程。笔者没有介绍每一步的详细过程,旨在提供一个框架的搭建流程。

转载:http://www.openhw.org/module/forum/thread-644629-1-1.html

浙公网安备 33010602011771号

浙公网安备 33010602011771号