Intel Triple-speed Ethernet IP 使用笔记(三)

寄存器配置方法:

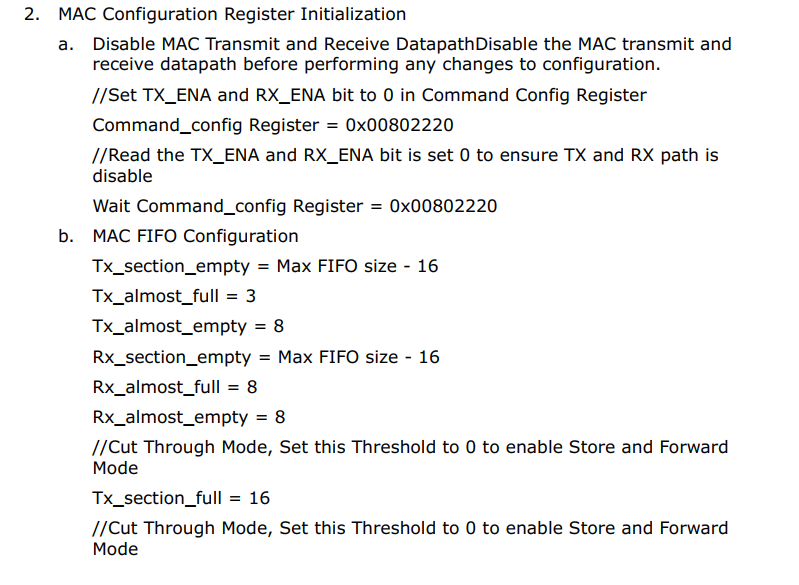

- 根据手册5.3Register Initialization进行寄存器配置(我这里是MII接口)

- 我给工程加了上电复位1us的模块,复位之后,开始进行寄存器设置,确保上电所有的寄存器被正确设置

- 寄存器配置部分代码如下,init_cnt为初始化计数器,上电复位完成之后,开始计数

//MAC端初始化

always @(posedge clk or negedge rst_n) begin

if(!rst_n) begin

eth_ctrl_reg_addr <= 8'h0 ;

eth_ctrl_reg_rden <= 0 ;

eth_ctrl_reg_wren <= 0 ;

eth_ctrl_reg_wrdata <= 0 ;

end

else begin

case(init_cnt)

0: begin//command_register txena/rxena disabled

eth_ctrl_reg_wren <= 1 ;

eth_ctrl_reg_addr <= 8'h02 ;

eth_ctrl_reg_wrdata <= 32'h0080_2220 ;

end

1: begin//tx_section_empty= MAX FIFO size -16

eth_ctrl_reg_wren <= 1 ;

eth_ctrl_reg_addr <= 8'h09 ;

eth_ctrl_reg_wrdata <= MAX_FIFO_SIZE -16 ;

end

2: begin//tx_almost_full

eth_ctrl_reg_wren <= 1 ;

eth_ctrl_reg_addr <= 8'h0E ;

eth_ctrl_reg_wrdata <= 4 ;

end

3: begin//tx_almost_empty

eth_ctrl_reg_wren <= 1 ;

eth_ctrl_reg_addr <= 8'h0D ;

eth_ctrl_reg_wrdata <= 8 ;

end

4: begin//rx_section_empty

eth_ctrl_reg_wren <= 1 ;

eth_ctrl_reg_addr <= 8'h07 ;

eth_ctrl_reg_wrdata <= MAX_FIFO_SIZE -16 ;

end

5: begin//rx_section_almost_full

eth_ctrl_reg_wren <= 1 ;

eth_ctrl_reg_addr <= 8'h0C ;

eth_ctrl_reg_wrdata <= 8 ;

end

6: begin//rx_almost_empty

eth_ctrl_reg_wren <= 1 ;

eth_ctrl_reg_addr <= 8'h0B ;

eth_ctrl_reg_wrdata <= 8 ;

end

7: begin//tx_section_full

eth_ctrl_reg_wren <= 1 ;

eth_ctrl_reg_addr <= 8'h0A ;

eth_ctrl_reg_wrdata <= 16 ;

end

8: begin//rx_section_full

eth_ctrl_reg_wren <= 1 ;

eth_ctrl_reg_addr <= 8'h08 ;

eth_ctrl_reg_wrdata <= 16 ;

end

9: begin//设置MAC0寄存器

eth_ctrl_reg_wren <= 1 ;

eth_ctrl_reg_addr <= 8'h03 ;

eth_ctrl_reg_wrdata <= 32'h17231c00 ;

end

10: begin//设置MAC1寄存器

eth_ctrl_reg_wren <= 1 ;

eth_ctrl_reg_addr <= 8'h04 ;

eth_ctrl_reg_wrdata <= 32'h0000cb4a ;

end

11: begin//max frm_length设置

eth_ctrl_reg_wren <= 1 ;

eth_ctrl_reg_addr <= 8'h05 ;

eth_ctrl_reg_wrdata <= 32'd1518 ;

end

12: begin//tx_ipg_length设置

eth_ctrl_reg_wren <= 1 ;

eth_ctrl_reg_addr <= 8'h17 ;

eth_ctrl_reg_wrdata <= 12 ;

end

13: begin//pause_quant

eth_ctrl_reg_wren <= 1 ;

eth_ctrl_reg_addr <= 8'h06 ;

eth_ctrl_reg_wrdata <= 32'h0000_FFFF ;

end

14: begin

eth_ctrl_reg_wren <= 1 ;

eth_ctrl_reg_addr <= 8'h02 ;

eth_ctrl_reg_wrdata <= 32'h00800220 ;

end

15: begin//commaon,rst,set SW_RESET bit to 1

eth_ctrl_reg_wren <= 1 ;

eth_ctrl_reg_addr <= 8'h02 ;

eth_ctrl_reg_wrdata <= 32'h00802220 ;

end

16: begin//wait

eth_ctrl_reg_wren <= 1 ;

eth_ctrl_reg_addr <= 8'h00 ;

eth_ctrl_reg_wrdata <= 32'h00100000 ;

end

17: begin//wait

eth_ctrl_reg_wren <= 1 ;

eth_ctrl_reg_addr <= 8'h02 ;

eth_ctrl_reg_wrdata <= 32'h00800220 ;

end

18:begin

eth_ctrl_reg_wren <= 1 ;

eth_ctrl_reg_addr <= 8'h02 ;

eth_ctrl_reg_wrdata <= 32'h00800223 ;

end

default: begin

eth_ctrl_reg_wren <= 0 ;

eth_ctrl_reg_addr <= 8'h00 ;

eth_ctrl_reg_wrdata <= 32'h00000000 ;

end

endcase

end

end