基于Arria 10 GX 的 10GBASE-R 设计笔记--PHY

PHY层设计

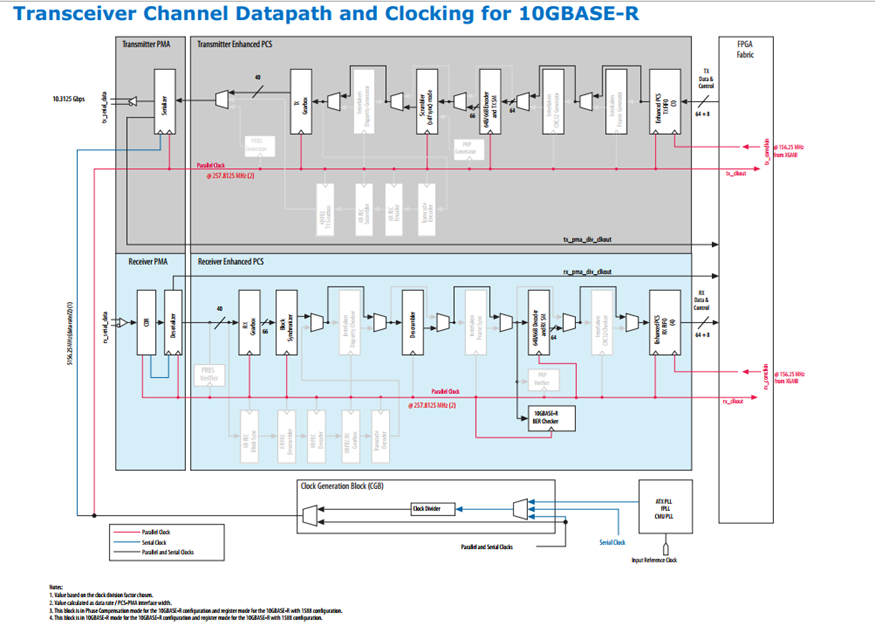

完整PHY层模块框图如下:

PHY层需要三个模块:xcvr_native_10g_phy\atx_reset_controller\atx_pll

- xcvr_native_10g_phy

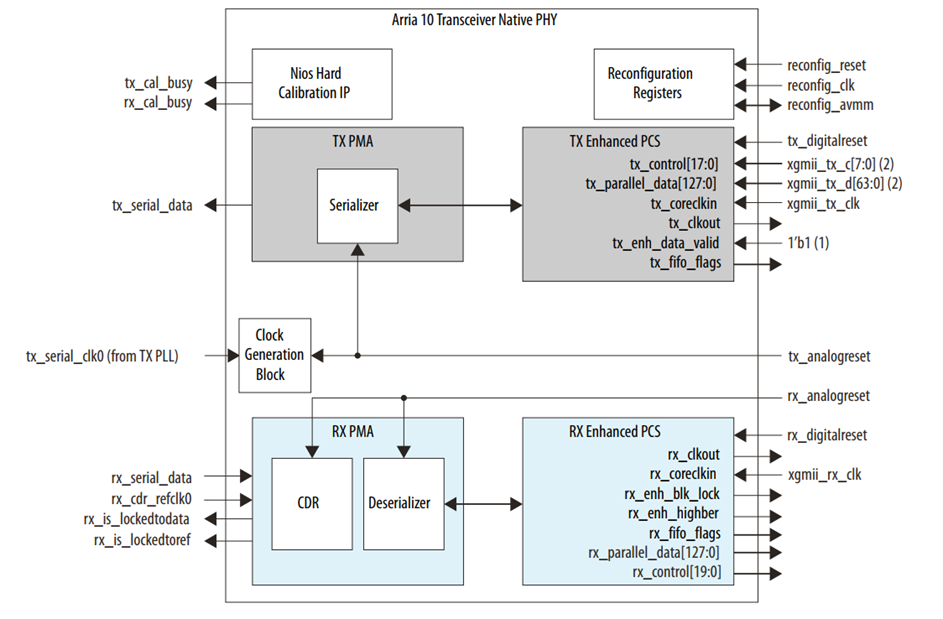

- 框图

![]()

- xcvr_native_10g_phy包括了PMA\Ehanced PCS,需要注意

- Parallel Clock是根据数据位宽来确定,比如数据位宽为40bit,那这里的Parallel Clock频率就需要是10.3125G/40=257.8125Mhz,如果位宽为66bit(64+2),则为10.3125G/66=156.25Mhz

- Serial Clock的频率需要是5156.25 MHz (数据速率/2=10.3125/2=5156.25Mhz)

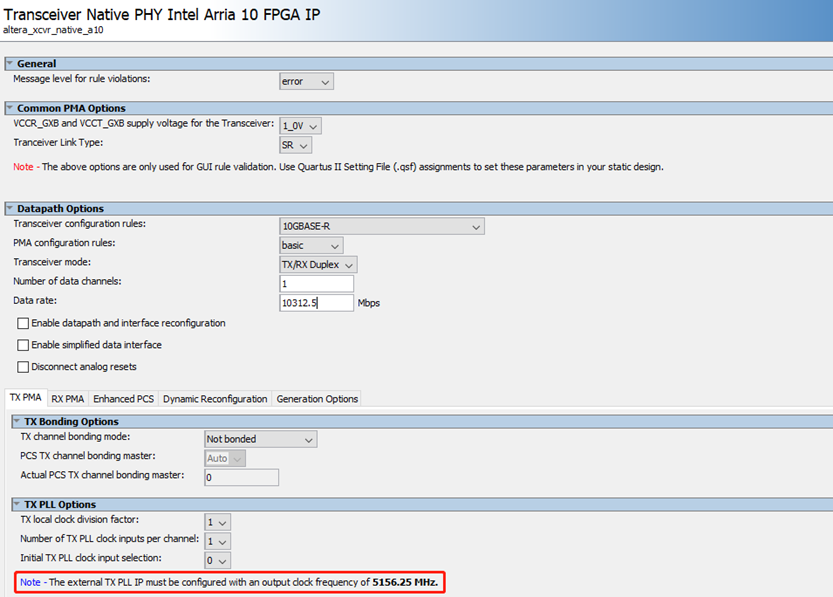

- 参数设置

- 在Platform designer里输入native phy,找到Transeiver Native PHY Intel Arria 10 FPGA IP,双击

- 在弹出窗口设置该IP名称,我这里设置的是xcvr_native_10g_phy

- 在参数设置窗口设置参数,在Transeiver configuration rules里选择协议类型10GBASE-R,PMA configuration rules里选择basic, Transeiver mode选择TX/RX Duplex即:包含收和发;data channels数量设置为1,Arria 10 GX可以用的17.4 Gbps channel总共是96个(看器件手册),这里只需要一个;Data rate(数据速率)设置为10312.5;

![]()

![]()

备注:注意图片红色框里这句话:The external TX PLL IP must be configured with an output clock frequency of 5156.25Mhz;这个很重要对ATX_PLL串行时钟输出频率的一个硬性要求

- 接着设置TX PMA相关参数

- 设置RX PMA参数

- 设置Enhanced PCS参数

- 仿真

- 在platform designer 里点击generate testbench system

![]()

- 仿真不需要自己创建modelsim 工程,只需打开modelsim切换到生成testbench目录下的mentor目录

- 输入指令source .tcl

- 输入指令ld_debug

- 问题解决

- Modelsim fails (vlog-2726) failed to access library..!

该问题需要Quartus重新re-generated IP并编译一下当前工程,即可解决

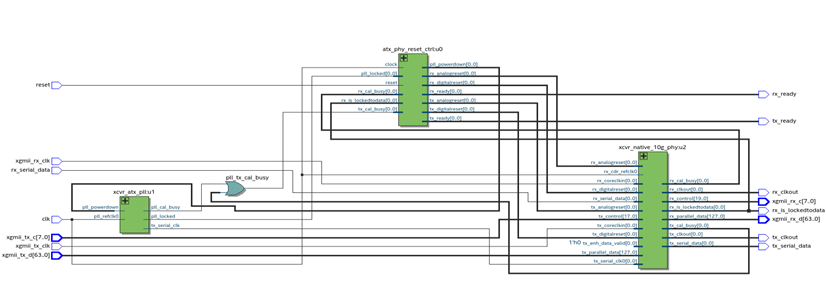

- atx_reset_controller

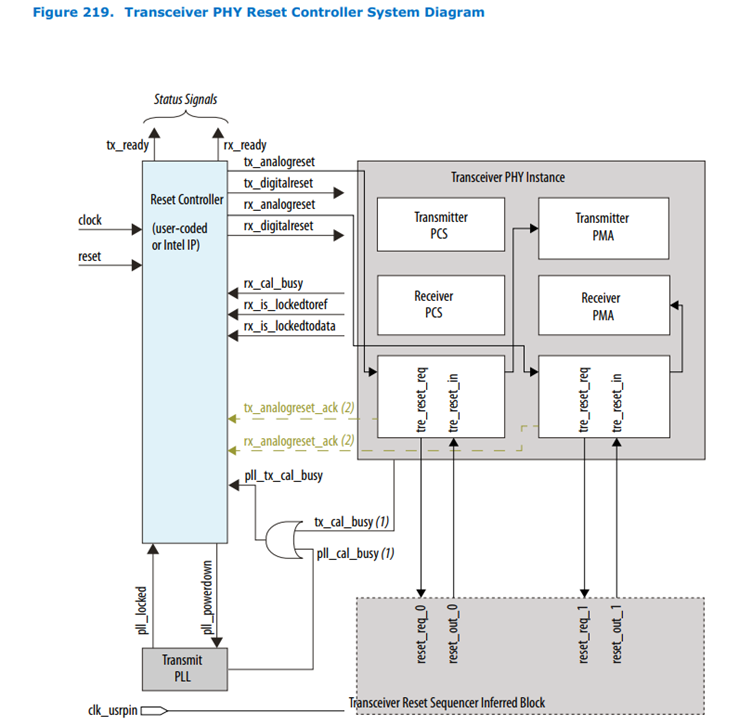

- A10 Transceiver PHY Reset Controller系统与xcvr_native_10g_phy之间链接框图

- 注意

- 这里的pll_tx_cal_busy为 tx_cal_busy | pll_cal_busy

- rx_is_lockedtoref和rx_is_locedtodata这两个信号根据自己的需求可以不要

- 仿真

- 方法同xcvr_native_10g_phy仿真方法

- atx_pll

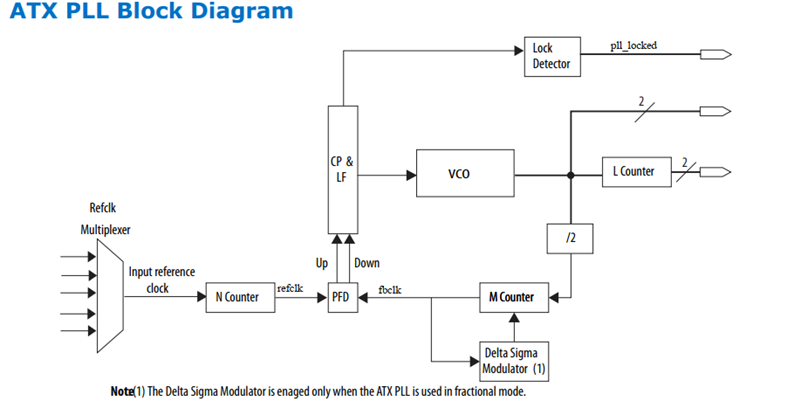

- 框图

- atx_pll模块需要注意

- 主要是用来产生Transceiver TX serial clock,频率根据xcvr_native_10g_phy的要求进行设置

- 这里设置为5156.25Mhz

- 仿真

- 方法同xcvr_native_10g_phy仿真方法

- 整个PHY模块链接框图

![]()

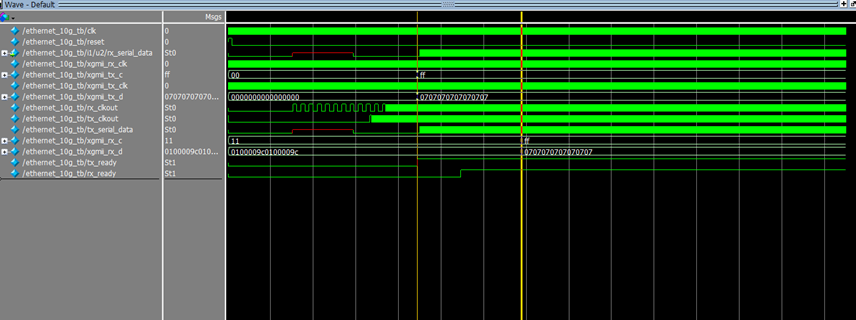

- 仿真

- 仿真结果如下

![]()