Intel OpenVINO for FPGA(2019 R1.1)使用笔记2

官方demo测试:图片分类:

- 首先,我们需要对classification demo进行编译:

- 输入指令:source /opt/init_openvino.sh,设置OpenVINO 2019 R1.1环境变量,init_openvino.sh的内容如下(根据自己的安装包路径进行修改):

#!/bin/bash

################################################

# Intel Quartus Prime

################################################

export ACDS_DEST_ROOT=/opt/inteldevstack/intelFPGA_pro

export QUARTUS_ROOTDIR=/opt/inteldevstack/intelFPGA_pro/quartus

export QUARTUS_DIR=/opt/inteldevstack/intelFPGA_pro/quartus

export QSYS_ROOTDIR=/opt/inteldevstack/intelFPGA_pro/qsys/bin

export QUARTUS_HOME=$QUARTUS_ROOTDIR

export PATH=$QUARTUS_ROOTDIR/bin:$PATH

export QUARTUS_64BIT=1

export QUARTUS_EDITION_OVERRIDE=pro

export QUARTUS_ROOTDIR_OVERRIDE="$QUARTUS_ROOTDIR"

################################################

#OPAE

###############################################

export DCP_LOC=/opt/inteldevstack/a10_gx_pac_ias_1_2_pv

export OPAE_PLATFORM_ROOT=/opt/inteldevstack/a10_gx_pac_ias_1_2_pv

export OPAE_LOC=$DCP_LOC/sw/opae-1.1.2-1

################################################

# Added to support QPI_FPGA

################################################

# SDK root

export CL_CONTEXT_COMPILER_MODE_ALTERA=3

export CL_CONTEXT_COMPILER_MODE_INTELFPGA=3

export ALTERAOCLSDKROOT=/opt/intelFPGA_pro/18.1/hld

export INTELFPGAOCLSDKROOT=/opt/intelFPGA_pro/18.1/hld

# BSP root

export AOCL_BOARD_PACKAGE_ROOT=/opt/inteldevstack/a10_gx_pac_ias_1_2_pv/opencl/opencl_bsp

export IOCL_BOARD_PACKAGE_ROOT=/opt/inteldevstack/a10_gx_pac_ias_1_2_pv/opencl/opencl_bsp

export PATH=$ALTERAOCLSDKROOT/bin:$PATH

export LD_LIBRARY_PATH=$ALTERAOCLSDKROOT/host/linux64/lib

export LD_LIBRARY_PATH=$AOCL_BOARD_PACKAGE_ROOT/linux64/driver:$AOCL_BOARD_PACKAGE_ROOT/linux64/lib:$LD_LIBRARY_PATH

source /opt/intel/openvino_fpga_2019.1.144/bin/setupvars.sh

-

-

输入指令cd /opt/intel/openvino_2019.1.144/deployment_tools/inference_samples/

-

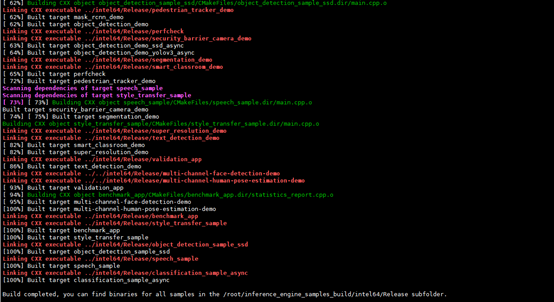

输入指令sudo ./build_samples.sh,进行build demo,build完成后如下:

-

-

-

编译完成后,输入指令:cd /root/inference_engine_samples_build/intel64/Release/,如下:

-

-

- 输入指令:aocl program acl0 /opt/intel/openvino_2019.1.144/bitstreams/a10_dcp_bitstreams/2019R1_RC_FP11_ResNet_SqueezeNet_VGG.aocx ;配置FPGA PAC卡的bitstream,这里配置2019R1_RC_FP11_ResNet_SqueezeNet_VGG.aocx

-

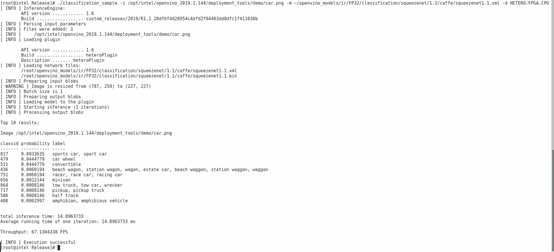

- 在/root/inference_engine_samples_build/intel64/Release/目录下,输入指令./classification_sample -i /opt/intel/openvino_2019.1.144/deployment_tools/demo/car.png -m ~/openvino_models/ir/FP32/classification/squeezenet/1.1/caffe/squeezenet1.1.xml -d HETERO:FPGA,CPU,运行demo,结果如下

-

-

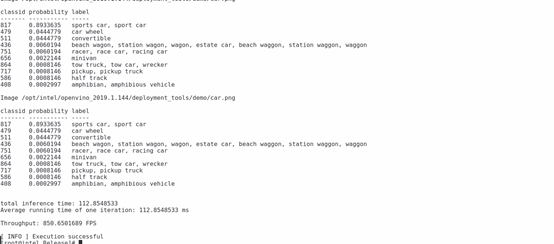

上一步的Through put性能为67fps,如果需要更好的性能,输入指令./classification_sample `for i in {1..96};do echo -i "/opt/intel/openvino_2019.1.144/deployment_tools/demo/car.png";done` -m ~/openvino_models/ir/FP32/classification/squeezenet/1.1/caffe/squeezenet1.1.xml -d HETERO:FPGA,CPU,调整batchsize 为96,输出结果Throughput为850fps,如下:

-