[FPGA与ASIC] 优化方法

reg表示综合出触发器(该说法错误).因为always块(变量必须为reg)既能是时序电路,也能是组合电路。- 组合电路一般是电平敏感的always块,或

assign语句; - 时序电路一般是时钟沿敏感的always块。

优选设计原则

优选同步设计

- 尽可能使用时钟驱动的触发器(Flip-Flop)作为时序器件。因为综合器在时钟信号的基准下能优化触发器之间的组合电路。

优选触发器输出

- 模块的输出推荐使用触发器输出,这使得模块与模块间的连线在时序上有充裕的延迟时间,便于后端工具满足时序要求。

也可以消除毛刺(组合逻辑输出信号容易有毛刺出现)。

区分控制模块和运算模块

- 使设计更加简捷。

写完整的信号敏感列表

- 如果有信号没有列在信号敏感列表上,综合器会综合出Latch。

复位所有触发器

- 避免在测试向量仿真时产生Unknown。

- 异步输入端只有复位信号,不要混合其他同步信号。

时钟在顶层模块分频

- 时钟信号不会再综合阶段综合,而是在自动布局布线阶段做CTS。

内存(MEM,存储器)放在顶层模块

- 内存合并之后可能会得到架构上的简化,或者更易布局。

使用有意义的命名

- 如使用rst_n表示复位信号低电平有效。

避免/禁用设计原则

禁用异步触发器或锁存器(Latch)

- JK触发器和锁存器不能算作同步时序器件。

禁用含反馈的纯组合逻辑电路

- 组合逻辑的反馈形成异步电路,应予以避免。

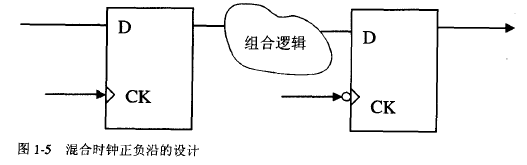

禁用混合上升沿和下降沿的设计

混合使用会压缩组合逻辑的传递时间,而且在Scan Chain时,下降沿触发器无法被串接。

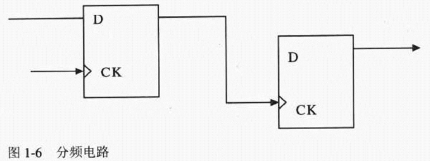

避免使用触发器驱动其他触发器

对于综合器而言,这违反了"时钟信号的综合应由CTS(Clock Tree Synthesis)处理"的原则。但很难避免,例如时钟分频电路。

禁用模块内部的Inout

- 设计更加简捷。

其他设计

有限状态机的状态编码方案

- 二进制编码:

parameter [1:0] S0=2'b00,S1=2'b01,S2=2'b10,S3=2'b11; - 格雷码:

parameter [1:0] S0=2'b00,S1=2'b01,S2=2'b11,S3=2'b10; - 独热码:

parameter [3:0] S0=4'b0001,S1=4'b0010,S2=4'b0100,S3=4'b1000;

二进制和格雷码: 占用触发器资源少(位宽少),但转移条件和跳转时(判断2位)组合逻辑多;

独热码: 占用触发器资源多(位宽多),但转移条件和跳转时(只判断1位)组合逻辑少;

- FPGA编程(Flip-Flop多)一般使用独热码;

- CPLD编程(组合逻辑多)一般使用格雷码或二进制码;

- IC设计中,状态较少时,使用独热码,状态较多时,使用格雷码.

算术模块

- 避免使用L=A×C+B×C,使用L=(A+B)×C;(前者用两个乘法器)

- 避免使用A={B,1'b0}+1,使用A={B,1'b1};(前者用了加法器)

- 避免使用Y=A+B+C+D,使用Y=(A+B)+(C+D);(前者串接了3个加法器,形成3级延时,后者2级加法器,形成2级延时)

结论: 优选使用 逻辑运算(位运算) > 算术运算; 加法运算 > 乘法运算; 逻辑表达式合并为每2项1级。

如果还不行,那就切流水咯。

浙公网安备 33010602011771号

浙公网安备 33010602011771号