Verilog里面的状态机,常用的是有限状态机(Finite State Machine,简称FSM),在有限的窗状态下按一定规律转换的时序电路,这个其实和C里面写软件状态机差不多。状态机在FPGA里面广泛使用,可以解决很多实际问题。

例如:

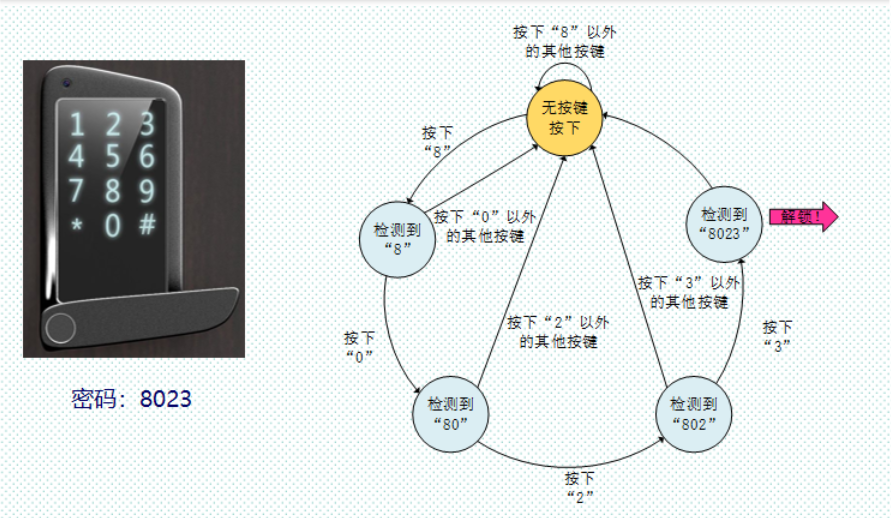

以下是一个门锁的状态机实现示意图:

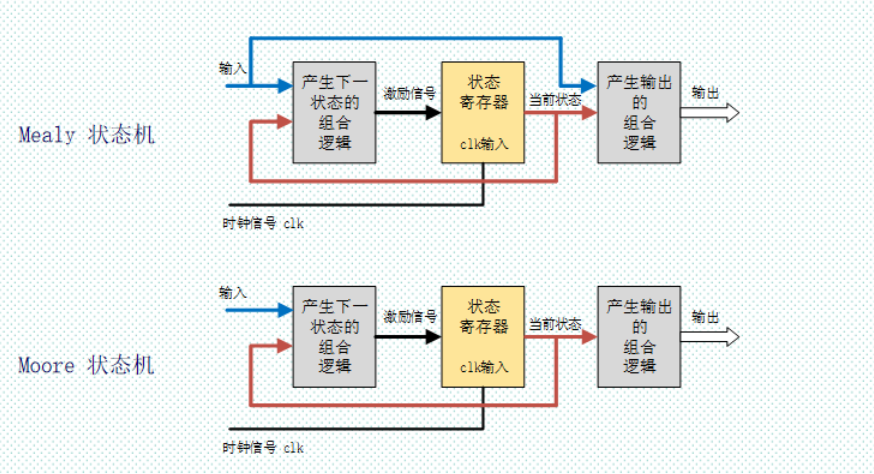

一般地,状态机分了两种:

可以看出这两种状态机的区别是,输入信号是否参与到输出逻辑模块。状态寄存器由一组触发器组成,用来记忆状态机当前所处的状态,状态的改变只发生在时钟的跳变沿。状态是否改变、如何改变,取决于组合逻辑F的输出,F是当前状态和输入信号的函数。状态机的输出是由输出组合逻辑G提供的,G也是当前状态和输入信号的函数。

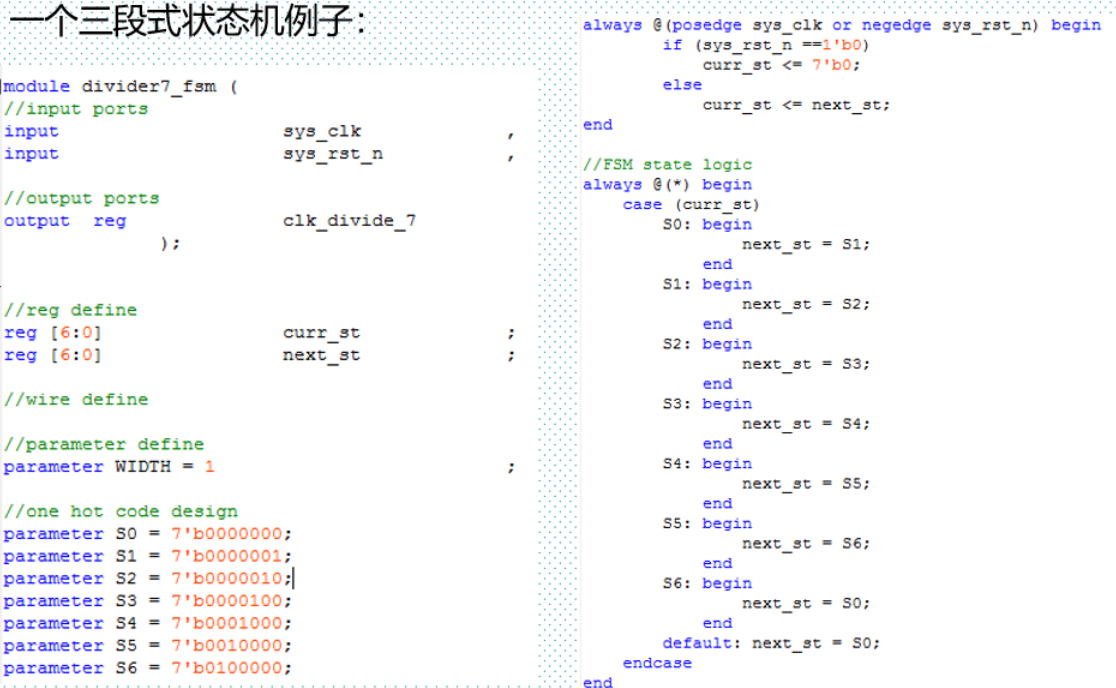

代码案例:

一般,状态机设计有如下几步:

1)定义不同状态以及定义不同状态下的动作

2)状态跳转

3)当前和下一个状态判断

一般地,在输出逻辑后面再增加一个寄存器输出,可以最大限度减少时序带来的输出毛刺,对输出进行时序约束,减少数据偏移,减少错误率。

Verilog状态机描述

Verilog状态机描述