CPU组成

CPU是中央处理器的缩写(Central Processing Unit),是计算机的核心部分(就是说一个CPU不能组成一个完整的计算机,需要搭配不同的外设。),是一块集成度极高的电路。CPU和不同的片外外设组成了不同的控制器(CPU和不同的外设组合在一起变成不同的芯片)。

8位简易CPU结构

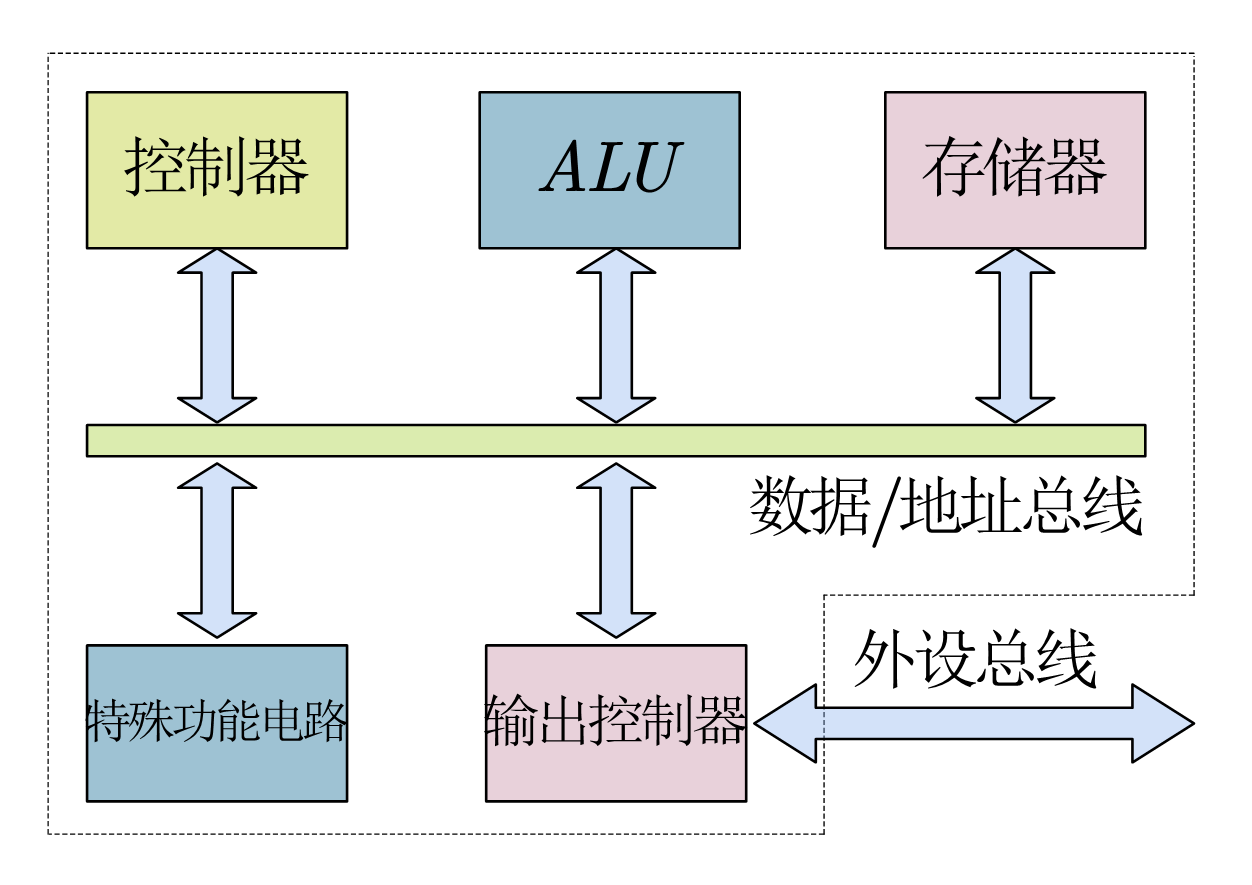

一般地,CPU里面有一个控制器、一个存储器、一个算术逻辑单元(ALU)以及不同具有特殊功能的外设,通过总线连接在一起。结构图如下:

控制器通过读取存储器里面的指令,对其进行译码,和执行。控制器控制数据进入ALU进行逻辑运算,计算完成后数据送到存储器或者特殊功能的电路,又或者送到外设上。

那么,具有CPU功能的电路,只需要三个必备条件:

1)有控制器

2)有ALU

3)有存储器

冯诺依曼结构

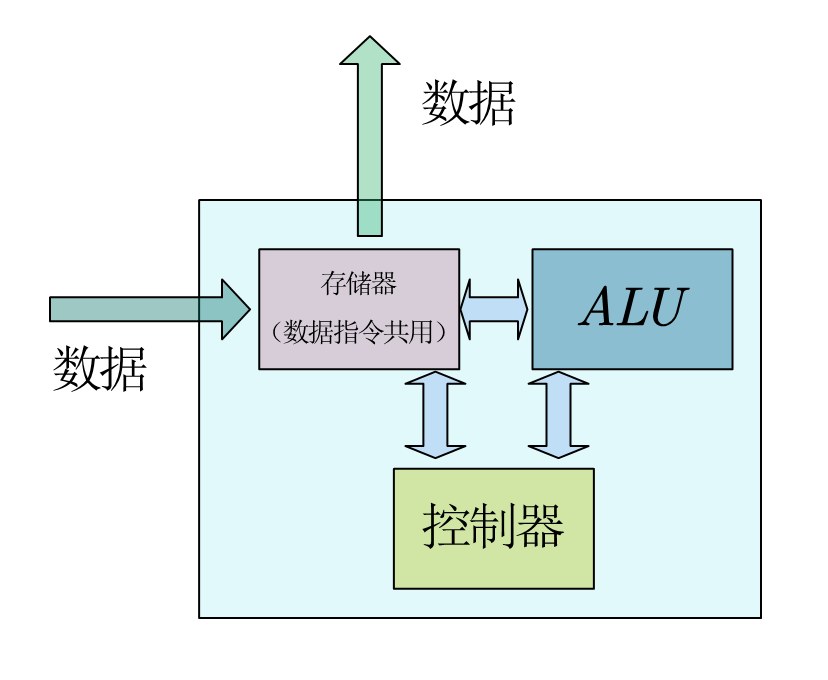

一个叫冯·诺依曼(一个数学家)的人提出的计算机结构,其结构主要如下:

早期计算机很多都是这种结构的,特别在70~90年代这段时间。它的最主要特点是:把指令和数据放在同一个存储器里面,这样读取数据可以减少总线数量。但是速度比较慢,成本低。

哈佛结构

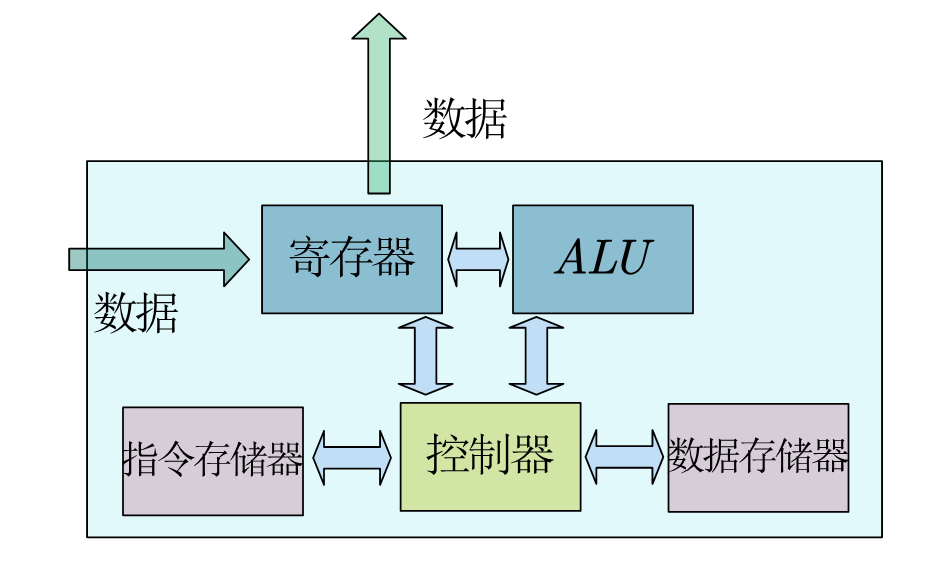

名字来历不太清楚,其结构主要如下:

因为数据存储器和指令那个存储器分开的,所以可以一边读指令一边读写数据,吞吐量比冯诺依曼大很多。可以说专门位告诉电路而生的,但是成本较高。典型的就是ARM的单片机内核——三级流水线哈佛结构。

MIPS指令集

机器运行时,需要根据指令进行工作,这里以MIPS展开。这种指令都是32位的,指的是由32个“0”和“1”组成的指令,也就是32bit(4个字节,对应占用4个地址,这个很好解释为什么指令执行地址的都是+4地跳着读)。

在MIPS里面,约定了32个寄存器(这些寄存器都有特定的功能)。着一些寄存器用于存放运算过程中产生的数据。不同指令集中,这些要求的寄存器就不一样。

FPGA上实现8位CPU

在FPGA上构建一个拥有CPU功能的电路,这里不打算将全部指令都纳入其中,寄存器也是。这里基于某智的陈年低配FPGA板卡:EP4CE6E22C8N进行试验。需要对这些指令进行裁剪,采用冯诺依曼结构进行设计。基于复位线和时钟线,把上述所有模块集成起来,实现一个简单的CPU电路。

CPU结构组成学习。

CPU结构组成学习。