最基本逻辑电路

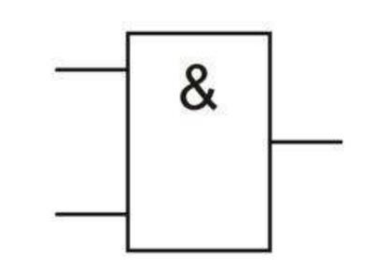

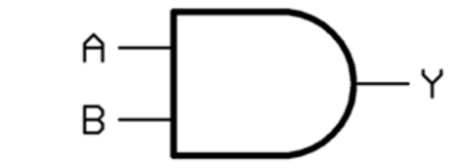

与门

数字电路中常见的一种门电路,即输入端全部为高电平,输出端即为高电平,否则为低电平。符号如下图所示:

或者

用Verilog实现:

module and_gate(

input A,

input B,

output C

);

assign C <= A&B;

endmodule

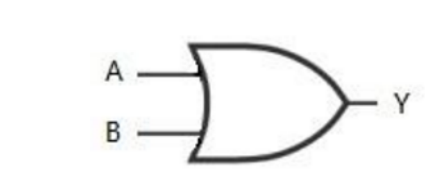

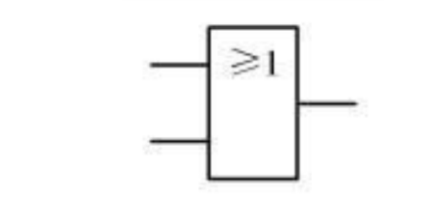

或门

数字电路中常见的一种门电路,即输入端只要有一路为高电平,输出即可为高电平,否则为低电平。符号如下图所示:

或者

用Verilog实现:

module or_gate(

input A,

input B,

output C

);

assign C <= A|B;

endmodule

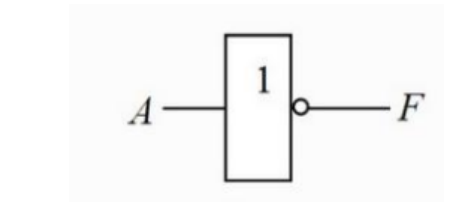

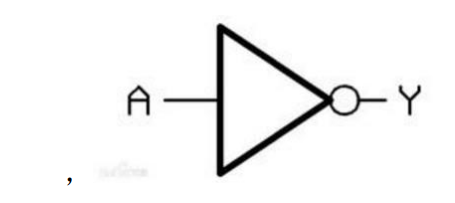

非门

数字电路中常见的一种门电路,即输入端电平和输出端电平是相反的。若输入为高电平,输出为低电平,反之为高电平。符号如下图所示:

或者

用Verilog实现:

module not_gate(

input A,

output B

);

assign B <= ~A;

endmodule

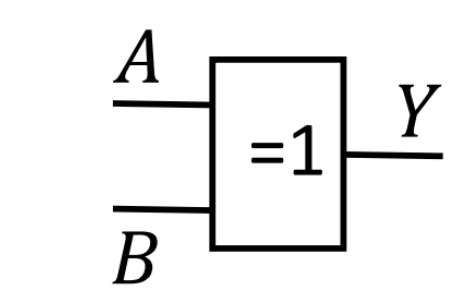

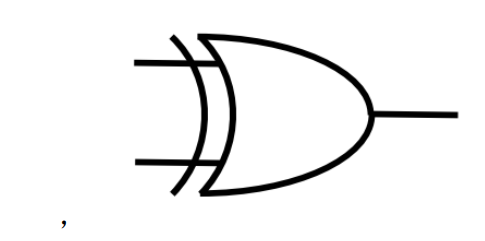

异或门

数字电路中常见的一种门电路。当输入端的电平信号相等,则输出低电平。当输入端电平信号不相同,则输出高电平。简图如下:

或者

用Verilog实现:

module not_gate(

input A,

input B,

output C

);

assign C <= A^B;

endmodule

组合应用实例

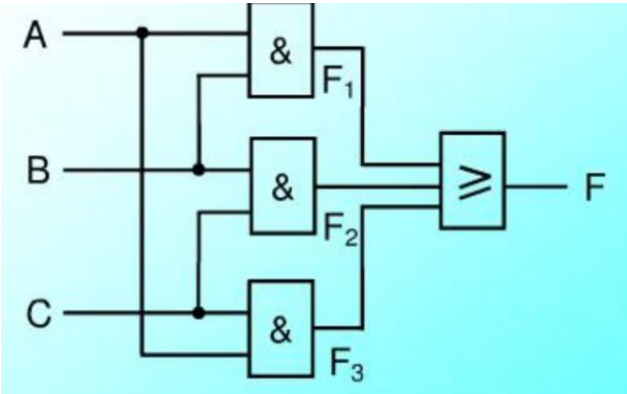

假设,参考下图设计出电路:

可以列出以下关系式:

F=F1+F2+F3

对其进行展开:

F=A&B+B&C+A&C

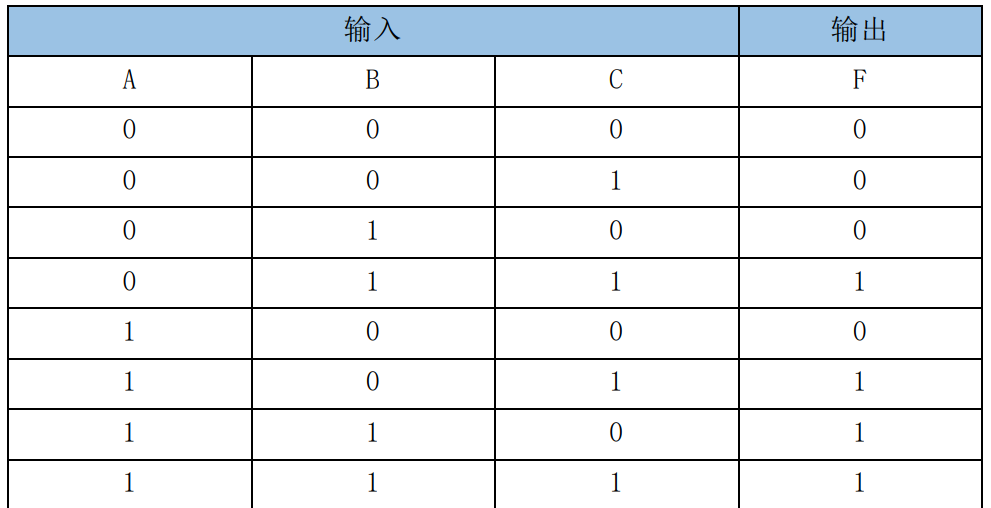

则真值表如下:

用verilog实现可以用以下代码:

module assembly_gate(

input A,

input B,

input C,

output F

);

//作为逻辑运算的中间值可以用wire类型定义

wire F1;

wire F2;

wire F3;

assign begin

F1 <= A&B;

F2 <= B&C;

F3 <= A&C;

end

assign F=F1|F2|F3;

endmodule

当然,可以在化简一点。

Verilog常见逻辑电路设计

Verilog常见逻辑电路设计