SDRAM在FPGA中操作实现

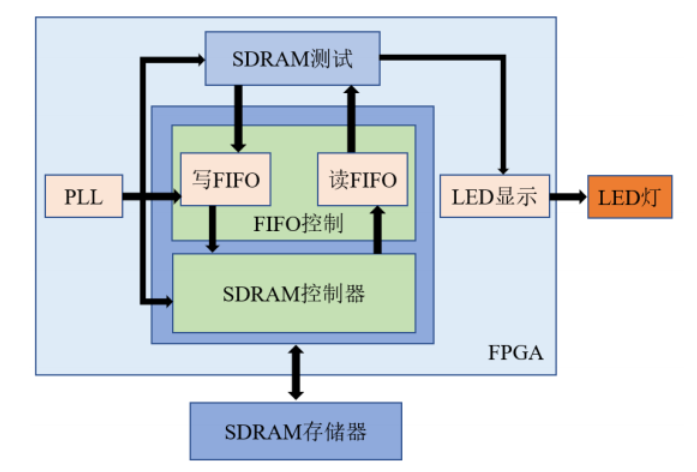

在操作中,整个系统可以通过把数据传入fifo,然后fifo把数据一个个送入SDRAM。当需要读取数据时候,则fifo把数据从SDRAM里面读入,顶层可以通过读取fifo获得数据。结构简图如下:

各模块描述

PLL

PLL模块需要有三路时钟输出:fifo端、SDRAM端、SDRAM测试以及LED显示端(假设fifo使用的的时同步fifo)。

FIFO

在接收到SDRAM测试端发送来的数据,直到满fifo信号拉出。然后将存储的数据读出写入SDRAM。

在这里,fifo需要分为读入模块和写入模块。

SDRAM控制器

负责控制SDRAM的读出和写入。这里分为读入模块和写入模块。

SDRAM测试模块

负责对fifo进行操作,以及把数据对比结果送入LED显示模块。

LED显示模块

根据数据对比结果,实现LED的亮灭控制。

工作流程

1、PLL上电对时钟进行倍频和分频,直到稳定,输出时钟线0~2以及locked。

2、SDRAM控制模块收到locked信号拉高,初始化后开始工作。

3、SDRAM控制模块写入fifo。

4、fifo写满后,数据写入SDRAM。

5、等待刷新时间和fifo读空信号。

6、fifo读取SDRAM,知直到写满信号。

7、SDRAM测试模块读取fifo。

8、数据送入LED显示模块对比,LED显示。

9、循环第一步。

在FPGA中实现SDRAM操作。

在FPGA中实现SDRAM操作。

浙公网安备 33010602011771号

浙公网安备 33010602011771号