Zynq UltraScale + MPSoC xilinx vivado 使用 PS 1.输出Hello World 2. PS 控制 MIO 点亮LED

1.介绍

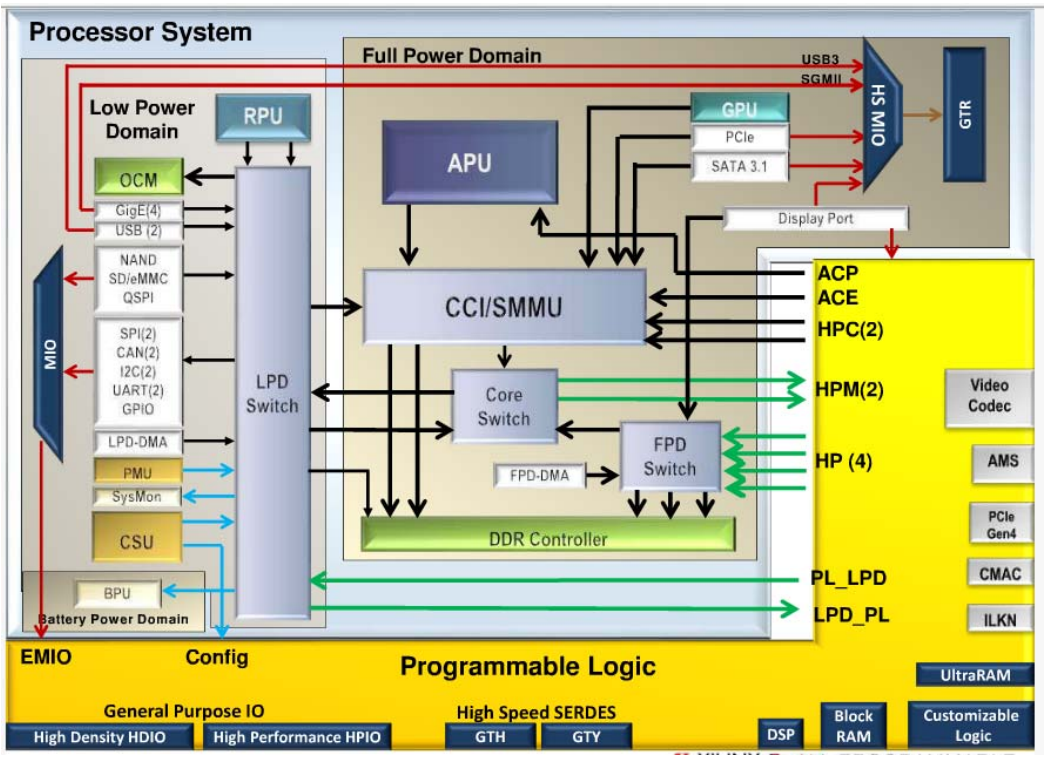

Zynq UltraScale + MPSoC带有通用处理系统(PS),该系统集成了高度灵活的高性能可编程逻辑(PL)部分,全部都在单个片上系统(SoC)上。Zynq UltraScale + MPSoC PS模块包括以下引擎:

-

基于四核Arm®Cortex™-A53的应用处理单元(APU)

-

基于双核Arm Cortex-R5F的实时处理单元(RPU)

-

基于Arm Mali™-400 MP2的图形处理单元(GPU)

-

专用平台管理单元(PMU)和配置安全单元(CSU)

-

高速外围设备列表,包括显示端口和SATA

除可编程逻辑单元外,可编程逻辑部分还集成了一些高性能外围设备,其中包括:

-

PCIExpress®的集成块

-

Interlaken的集成块

-

100G以太网集成块

-

系统监控器

-

视频编解码器单元

功能框图

Zynq UltraScale + MPSoC器件由两个主要的基础处理系统(PS)可编程逻辑(PL)模块组成,在两个隔离电源域中。

PS充当一台独立的MPSoC器件,能够启动并支持所有功能。

如图1-1,第8页所示,而未打开PL的电源。

Zynq UltraScale + MPSoC器件具有四个不同的电源域:

- 低功耗域(LPD)

- 全功率域(FPD)

- PL电源域(PLPD)

- 电池电源域(BPD)

每个电源域可以单独隔离。 平台管理单元(PMU)LPD有助于隔离每个电源域。 每个电源域可以单独隔离,功能隔离。

术语缩写:

Application processing unit (APU) 应用程序处理单元

Real-time processing unit (RPU) 实时处理单元

Global Interrupt Controller (GIC) 全局中断控制器

模块选择:

| 功能模块 | 优化选择 | 理想选择 |

| APU |

|

|

| RPU |

|

|

| PL |

|

|

| GPU |

|

|

另一个方面是处理块的最高时钟速度:

•APU –高达1.5 GHz

•RPU –最高600 MHz

•GPU –最高667 MHz

开发流程:

开发人员在创建软件解决方案时不仅限于一种环境。 相反,多个环境用于创建单个镜像。

例如,可以通过多种工具创建Zynq UltraScale + MPSoC的可执行闪存映像:

- Vivado IP集成和处理器配置向导(PCW)配置PS子系统和.bit文件组件。

- SDK用于创建BSP,PMU固件,FSBL和应用程序镜像,并包括用于创建组合镜像的bootgen实用程序。

- PetaLinux用于创建开源软件镜像,例如U-Boot,ATF,Linux,设备树blob等。

Yocto 设计环境

Yocto功能包括:

- 提供最新的Linux内核以及一组适用于嵌入式环境的系统命令和库。

- 提供可用的系统组件,例如X11,GTK +,Qt,Clutter和SDL(以及其他)。

- 创建一个与OpenEmbedded项目兼容的集中且稳定的内核,可靠地构建和开发Linux软件。

- 通过快速仿真器(QEMU)支持广泛的硬件和设备仿真。

Vitis集成设计环境

Vitis统一软件平台是一个集成开发环境(IDE),用于开发针对Xilinx嵌入式处理器的嵌入式软件应用程序。Vitis软件平台可与通过Vivado Design Suite创建的硬件设计一起使用。

Vitis软件平台基于Eclipse开源标准。包括以下功能:

-

功能丰富的C / C ++代码编辑器和编译环境

-

项目管理

-

应用程序构建配置和自动生成Makefile

-

错误导航

-

用于嵌入式目标的无缝调试和性能分析的集成环境。

-

源代码版本控制

-

系统级性能分析

-

配置FPGA的专用工具

-

可启动映像创建

-

闪存编程

-

基于脚本的命令行工具(XSCT)

其他组件包括:

-

嵌入式软件开发的驱动程序和库

-

用于C / C ++软件开发的Linaro GCC工具链,针对Zynq UltraScale +处理系统中的Arm Cortex-A53和Arm Cortex-R5F MPCore处理器

Vivado设计套件

Vivado设计套件为FPGA实现提供了广泛的开发系统工具。不需要软件编程时,可以将其作为独立工具安装。它也是Vitis IDE安装的一部分。各种Vivado Design Suite版本可用于嵌入式系统开发。在本指南中,使用了随Vitis IDE一起安装的System Edition

PetaLinux工具

PetaLinux工具集是嵌入式Linux系统开发套件。它提供了一个多方面的Linux工具流程,可为Xilinx Zynq设备(包括Zynq UltraScale +设备)的Linux OS提供完整的配置,构建和部署环境。

Xilinx设计工具如何加快设计速度

使用Vivado Design Suite工具将设计源添加到硬件。其中包括IP集成器,该集成器简化了将IP添加到现有项目并创建端口连接(例如时钟和重置)的过程。

使用Vivado工具和IP集成器来完成所有硬件系统开发。这包括指定Zynq UltraScale +处理系统,外围设备以及这些组件的互连以及它们各自的详细配置。

Vitis IDE可用于软件开发,硬件加速和平台开发。它也可以用来调试软件应用程序。

Zynq UltraScale + PS可以在不对PL进行编程的情况下启动和运行。

但是,要在结构中使用任何软IP或使用EMIO绑定PS外设,必须使用Vitis IDE或Vivado硬件管理器对PL进行编程。

PetaLinux工具

安装PetaLinux工具。PetaLinux工具在运行以下其中一项的Linux主机系统下运行:

-

RHEL 工作站/服务器7.4、7.5、7.6、7.7、7.8(64位)

-

CentOS工作站/服务器7.4、7.5、7.6、7.7、7.8(64位)

-

Ubuntu Linux工作站/服务器16.04.5、16.04.6、18.04.1、18.04.2、18.04.3、18.04.4(64位)

它可以使用专用的Linux主机系统,也可以使用在Windows开发平台上运行这些Linux操作系统之一的虚拟机。

在所选系统上安装PetaLinux工具时,必须执行以下操作:

-

从Xilinx网站下载PetaLinux 2020.2软件。

-

从2020.2下载页面下载ZCU102 PetaLinux BSP(ZCU102 BSP(prod-silicon))。

先决条件

-

8 GB RAM(对于Xilinx工具,建议最低)

-

2 GHz CPU时钟或等效时钟(最少八个内核)

-

100 GB可用硬盘空间

Zynq UltraScale +系统配置

创建Zynq UltraScale +系统设计涉及配置PS以选择适当的引导设备和外围设备。

首先,只要PS外设和可用的MIO连接满足设计要求,就不需要比特流。本节将说明完成一个不需要位流的基于PS的简单设计。

此示例设计不需要输入文件。我们将从头开始创建Vivado设计。该设计包括MPSoC的处理系统模块。在此示例设计中,不会添加任何PL IP,因此该设计无需贯穿实现和位流生成。

此示例设计的输出是硬件配置XSA。它将用于进一步的软件开发。

-

输入:N / A

-

输出:

example_PS_wrapper.xsa (vitis平台为xsa 旧版为example_PS_wrapper.hdf)

开始设计

-

启动Vivado设计套件。

-

在“ Vivado快速入门”页面中,单击“创建项目”以打开“新建项目”向导。

-

使用下表中的信息在每个向导屏幕中进行选择。

- 点击完成。将关闭“新建项目”向导,并在Vivado设计工具中打开刚刚创建的项目。

| 屏幕 | 系统属性 | 设置或使用命令 |

|---|---|---|

| 项目名 | 项目名 | example_PS |

| 项目地点 | D:/Users/changry/xilinx | |

| 创建项目子目录 | 保持选中状态 | |

| 项目类型 | 指定要创建的项目的类型 | RTL项目 |

| 暂时不指定来源复选框 | 保持选中状态。 | |

| 项目是可扩展的Vitis平台 | 取消选中 | |

| 默认 | 选择 | 选择Boards 选项卡 |

| 显示名称 | 选择Zynq UltraScale + ZCU102评估板 | |

| 新项目摘要 | 项目总结 | 查看项目摘要 |

创建一个块设计项目

现在,使用IP集成器来创建模块设计项目。

1.在Flow Navigator窗格中,展开IP集成器,然后单击Create Block Design。

将打开“创建模块设计”向导。

2.使用以下信息在“创建块设计”向导中进行选择。

| 屏幕 | 系统属性 | 设置或使用命令 |

|---|---|---|

| 创建模块设计 | 设计名称 | example_PS |

| 目录 | ||

| 指定源集 | 设计来源 |

3.单击确定。

将打开“Diagram”视图,并显示一条消息,指出该设计为空。下一步是从目录中添加一些IP。

4.点击添加IP  。

。

5.在搜索框中,键入zynq以找到Zynq设备IP。

6.双击Zynq UltraScale + MPSoC IP将其添加到模块设计中。

Zynq UltraScale + MPSoC处理系统IP块出现在Diagram视图中。

在Vivado中管理Zynq UltraScale +处理系统

现在,已将Zynq MPSoC的处理系统添加到设计中,开始管理可用选项。

1.在“框图”窗口中双击“ Zynq UltraScale +处理系统”模块。

随即打开“重新自定义IP”视图,如下图所示。请注意,默认情况下,处理器系统未连接任何外围设备。

2.单击“取消”退出视图,而不更改设计。

提示: 在“框图”窗口中,指出可以使用设计器帮助,如下图所示。如果提供了帮助,则可以单击链接以使Vivado在设计中执行该步骤。

3.现在,使用为ZCU102板创建的预设模板。单击运行块自动化链接。

将打开“运行块自动化”视图。

4.单击“确定”接受默认的处理器系统选项并进行默认的引脚连接。

此配置向导可根据ZCU102板的板布局,为处理系统中的许多外围设备分配一些多路I / O(MIO)引脚。例如,使能UART0和UART1。UART信号通过UART连接到USB-UART连接器,并连接到ZCU102板上的USB转换器芯片。

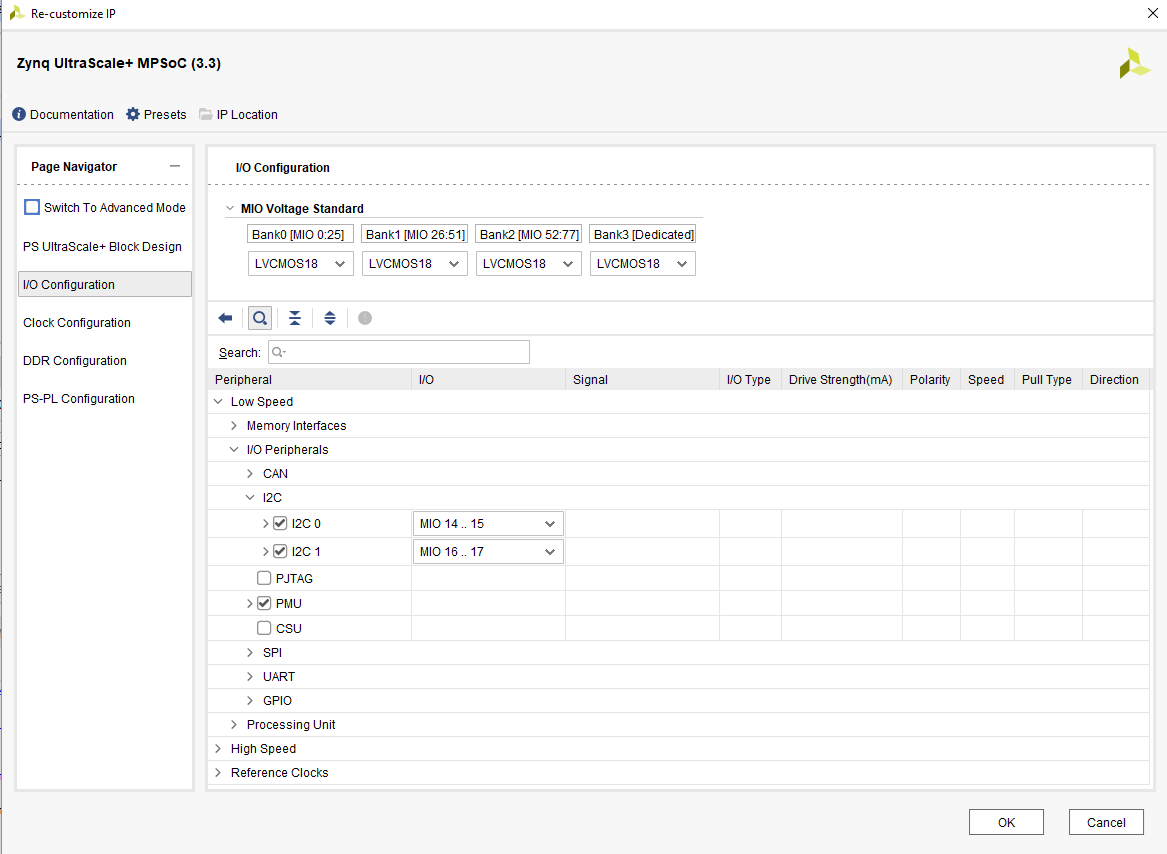

5.要进行验证,请在程序框图窗口中双击Zynq UltraScale + MPSOC模块。(不是demo板,按照自己板子的物理连接原理图,分别配置GPIO,DDR3(QSPI),NAND flash,UART0)

请注意Zynq UltraScale +设备框图中每个外围设备名称旁边的复选标记,表示活动的I / O外围设备。

6.在框图中,单击绿色的I / O外设之一,如上图所示。将为所选外围设备打开“ I / O配置”视图。

此页面使可以配置低速和高速外围设备。对于此示例,将继续使用针对ZCU102的主板预设启用的基本连接。

7.在页面导航器中,选择PS-PL配置。

8.在PS-PL配置中,展开PS-PL接口,然后展开 主接口。

对于此示例,由于PL中没有设计,因此可以禁用PS-PL接口。在这种情况下,可以禁用AXI HPM0 FPD和AXI HPM1 FPD主接口。

10.单击“确定”关闭“重新自定义IP”向导。

验证设计和连接端口

使用以下步骤来验证设计:

-

右键单击“框图”视图的空白区域,然后选择“ 验证设计”。或者,按F6键。

出现一个消息对话框,指出“验证成功。此设计中没有错误或严重警告。

-

单击确定以关闭消息。

-

在“块设计”视图中,单击“源”页面。

-

单击层次结构。

- 在“设计源”下,右键单击example_PS,然后选择“创建HDL包装器”。

将打开“创建HDL包装器”对话框。使用此对话框为处理器子系统创建HDL包装文件wrapper。

提示: HDL包装器是设计工具所需的顶级实体。

-

选择“让Vivado管理包装器并自动更新”,然后单击“确定”。

-

在“程序框图”的“源代码”窗口中的“设计源代码”下,您可以看到example_PS_wrapper是由Vivado创建的。展开层次结构,可以看到example_PS.bd已实例化(_i instantiated)。

-

选择从Flow Navigator-> IP INTEGRATOR -> Generate block design 。

如下图所示,将打开“生成输出产品”对话框。

-

选择综合选项为全局,然后单击生成。

此步骤将为选定的源构建所有必需的输出产品。例如,不需要为IP处理器系统手动创建约束。选择“生成输出产品”时,Vivado工具会自动为处理器子系统生成XDC文件。

-

生成输出产品的过程完成后,单击确定。

-

在“框图源”窗口中,单击“ IP源”页面。在这里,您可以看到刚刚生成的输出产品,如下图所示。

导出硬件

要使用GUI编写硬件平台,请按照下列步骤操作:

-

在Vivado Design Suite中选择文件→导出→导出硬件。将打开“导出硬件平台”窗口。

-

单击下一步。

-

在输出窗口中,选择“预合成”,然后单击“下一步”。

-

提供文件名和导出路径,然后单击“下一步”。

- 单击完成以在指定路径中生成硬件平台文件。这将是下一个示例的输入文件。(vitis平台xsa文件就是SDK hdf文件的延续)

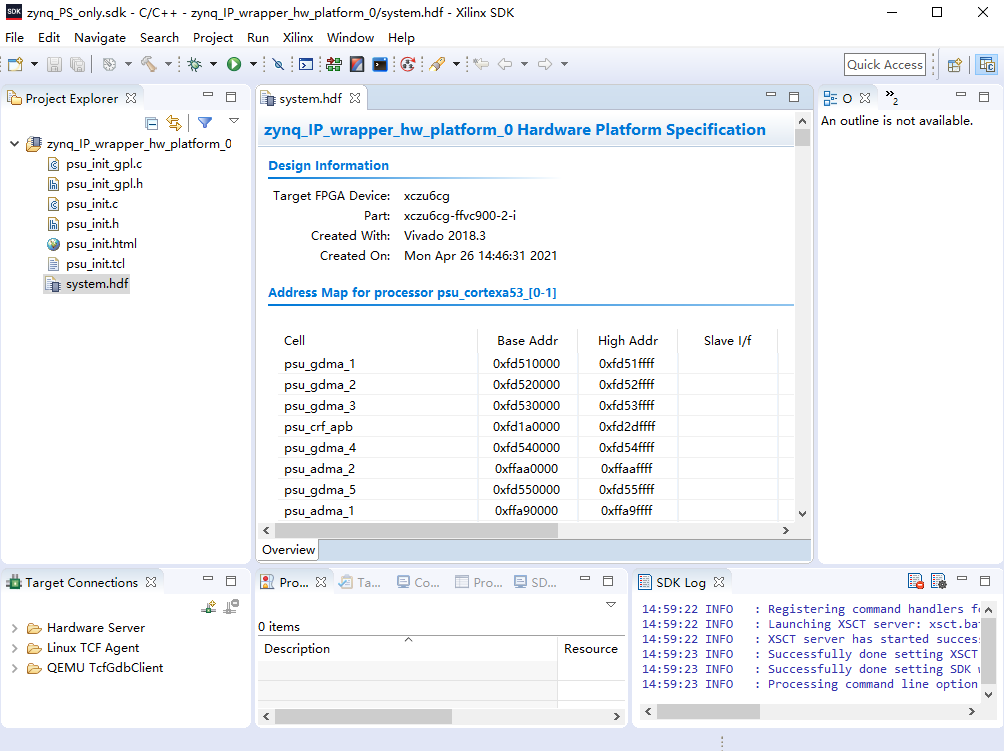

为PS子系统构建独立软件

导出的XSA文件包含硬件接力(handoff),处理系统初始化(psu_init)和PL位流(如果硬件是作为 post-implementation后实现导出的)。

使用IDE执行以下任务:

-

为硬件XSA创建平台项目。在此平台项目中,将创建用于PMU(平台管理单元)的第一阶段引导加载程序(FSBL)和PMU固件作为引导组件。

-

为应用程序处理单元(APU)创建裸机应用程序。

-

为APU和实时处理单元(RPU)创建一个系统项目。

Zynq UltraScale +MPsoc 中的主要处理单元如下:

-

应用处理单元:四核Arm®Cortex™-A53 MPCore处理器

-

实时处理单元:双核Arm Cortex™-R5F MPCore处理器

-

图形处理单元: Arm Mali™400 MP2 GPU

-

平台管理单元(PMU):基于Xilinx MicroBlaze™的平台管理单元

平台项目从XSA文件中读取硬件信息,并包含上述处理单元的运行时环境。应用程序软件可以链接到平台项目中生成的库.

输入和输出文件示例

-

输入:硬件切换XSA文件(

example_PS_wrapper.xsa) 旧版为(example_PS_wrapper.hdf) -

输出:

-

适用于Arm Cortex-A53的独立BSP库

-

启动组件(FSBL:

zynqmp.elf和helloword: helloword.elf)

-

了解SDx GUI

在SDx IDE中打开项目时,工作空间将以一系列不同的视图和编辑器(在IDE中也称为透视图)进行排列 。该工具将打开,并带有下图所示的SDx(默认)透视图。

默认透视图中的一些关键视图/编辑器是:

- 项目浏览器

- 显示项目文件夹及其关联的源文件,构建文件和工具生成的报告的面向文件的树形视图。

- 助手

- 提供一个集中位置来查看/编辑设置,构建和运行 SDSoC应用程序,启动性能分析和调试会话以及打开报告。

- 编辑区

- 显示项目设置,构建配置,并提供对用于处理项目的许多命令的访问。

- 控制台区

- 显示多个视图,包括命令控制台,设计指南,项目属性,日志和终端视图。

- 大纲

- 显示在“编辑器”区域中打开的当前源文件的轮廓。

- 目标连接

- 提供连接到SDx工具的不同目标的状态,例如Vivado 硬件服务器,目标通信框架(TCF)和快速仿真器(QEMU)联网。

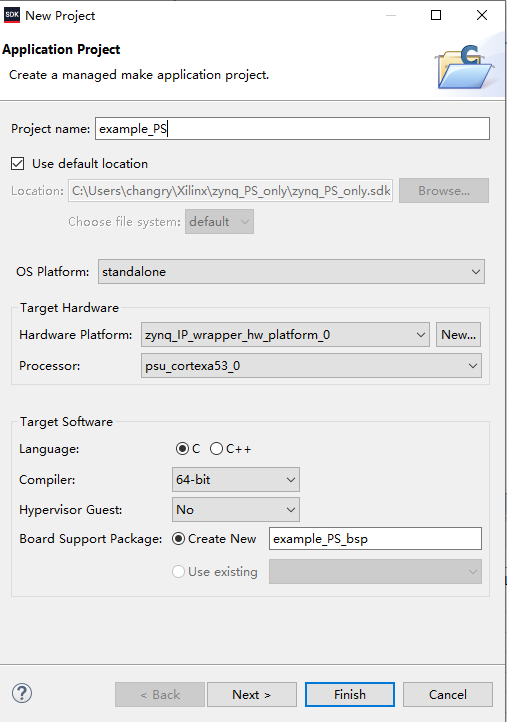

启动SDx™ IDE:

- 启动SDx IDE之后,您可以创建一个新项目。选择“

- 将打开“创建新的SDx应用程序项目”向导。

- 在“创建新的SDx应用程序项目”页面中,您可以指定项目名称,如下所示。在“项目名称”字段中指定项目的名称。

图:创建一个新的SDx 应用程序项目

-

默认情况下,选择“使用默认位置”以在SDx工作区的文件夹中找到您的项目。您可以取消选中此复选框以指定在您选择的位置创建项目。

-

如果指定位置,那么可以使用“选择文件系统”来选择默认文件系统JSch,或启用Eclipse远程文件系统资源管理器(RSE)。

重要说明:项目位置不能是SDx工作区的父文件夹。

一个平台由一个外壳组成,该外壳描述了基本硬件设计,将加速器附加到已声明的接口时使用的元数据以及软件环境,其中可以包括操作系统映像(例如Linux)以及引导程序。启动和运行时文件。

新建fsbl(第一级boot程序)应用并build All:

然后创建boot image

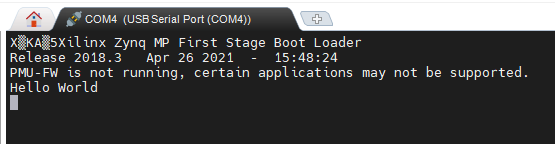

点击programm flash下载程序到板子中。重启板电源,串口输出 Hello World

示例2 使用PS 控制 MIO_26 MIO_27 点亮两颗 LED

#include <stdio.h> #include "platform.h" #include "xil_printf.h" #include "xparameters.h" #include "xgpiops.h" static XGpioPs mio_gpio; #define LED_DELAY 20000000 #define MIO_26 26 #define MIO_27 27 #define BANK2 2 int main() { int Delay; XGpioPs_Config *ConfigPtrPS; xil_printf("Hello Zynq MIO \n\r"); //XGpio_Initialize(&axi_pmod1, 0); ConfigPtrPS = XGpioPs_LookupConfig(0); XGpioPs_CfgInitialize(&mio_gpio, ConfigPtrPS, ConfigPtrPS->BaseAddr); XGpioPs_SetDirectionPin(&mio_gpio, MIO_26, 1); XGpioPs_SetOutputEnablePin(&mio_gpio, MIO_26, 1); XGpioPs_SetDirectionPin(&mio_gpio, MIO_27, 1); XGpioPs_SetOutputEnablePin(&mio_gpio, MIO_27, 1); init_platform(); int count; count = 0; print("Hello World\n\r"); while (1) { printf("LED spark %d \n\r", count++); // MIO8 MIO10 DS12 DS23 XGpioPs_WritePin(&mio_gpio, MIO_26, 0x0); XGpioPs_WritePin(&mio_gpio, MIO_27, 0x1); for (Delay = 0; Delay < LED_DELAY; Delay++); XGpioPs_WritePin(&mio_gpio, MIO_26, 0x1); XGpioPs_WritePin(&mio_gpio, MIO_27, 0x0); for (Delay = 0; Delay < LED_DELAY; Delay++); } cleanup_platform(); return 0; }

两颗LED灯闪烁,串口输出闪烁次数

浙公网安备 33010602011771号

浙公网安备 33010602011771号