AD7274 spi接口设计

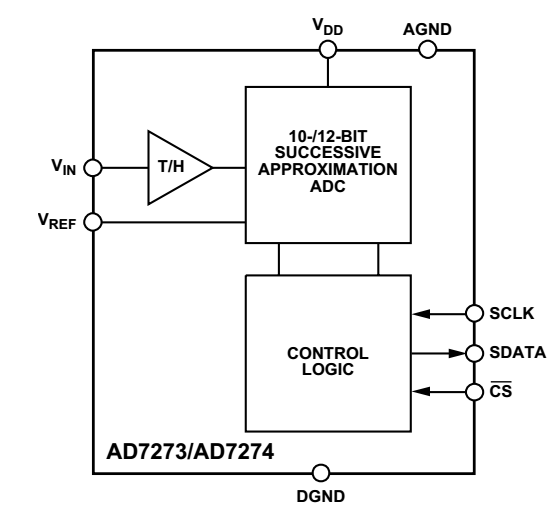

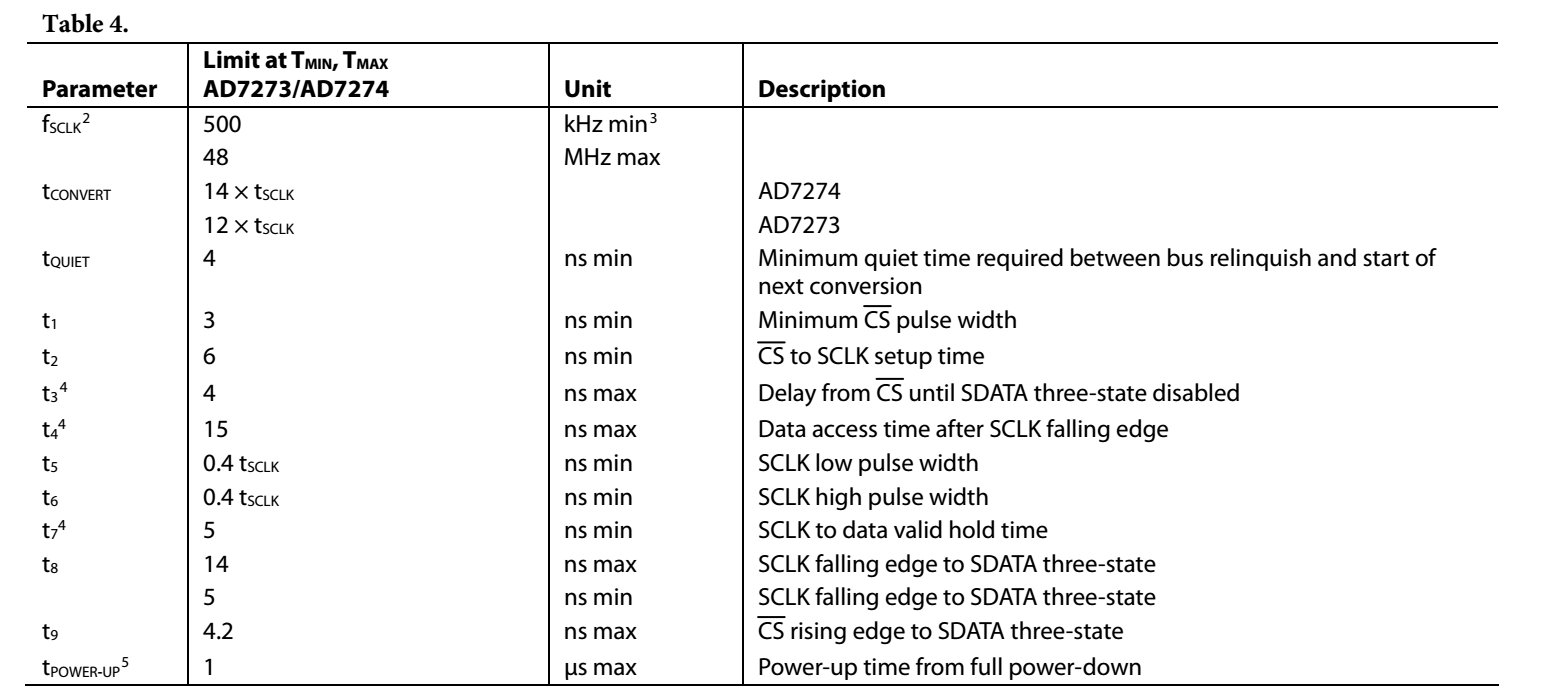

AD7274是一款SPI接口的ADC,最高时钟fsclk为48MHz,最高采样速率为3MSPS。其架构较为简单,逻辑端接口只有SCLK、SDATA、CS三个:

The input signal is sampled on the falling edge of CS, and the conversion is also initiated at this point.

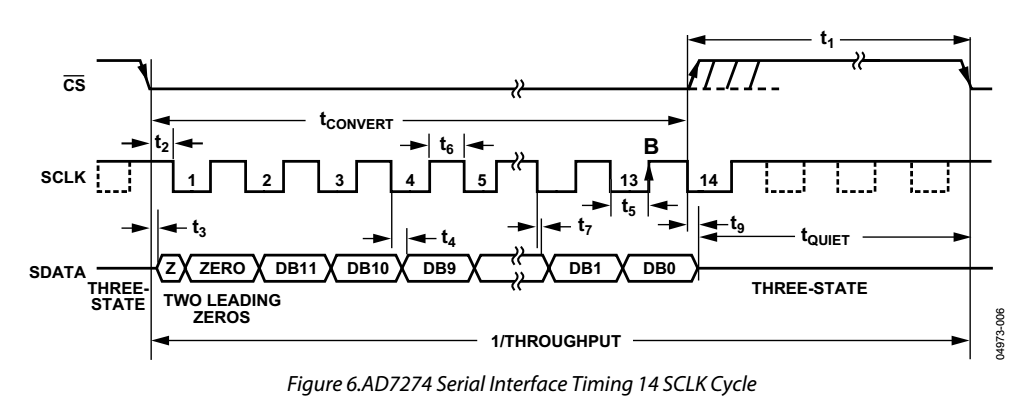

AD7274在CS的下降沿采样,数据输出有14th SCLK和16th SCLK两种,其中14th SCLK可以达到最大的3MSPS采样率,此次设计采用14th SCLK模式。下图为时序图:

可以看出:

1、时钟在空闲的时候应为1,CS拉低后,需要14个时钟的下降沿。

2、CS的下降沿和第一个SCLK的下降沿为t2,t2=6ns min

3、第3个时钟下降沿出采样数据

一、时钟设计:

fsclk=48MHz,tsclk = 20.833ns,通过mmcm产生两个48MHz的信号,clk_48m1, clk_48m2,其中clk_48m1的相位为0,clk_48m2的相位为320

二、时序设计:

1、利用clk_48m1与clk_48m2的相位差,生成t2=6ns min

2、assign clk_48m2n = clk_48m2,clk_48m2n 作为sclk,clk_48m2上升沿采sdata。

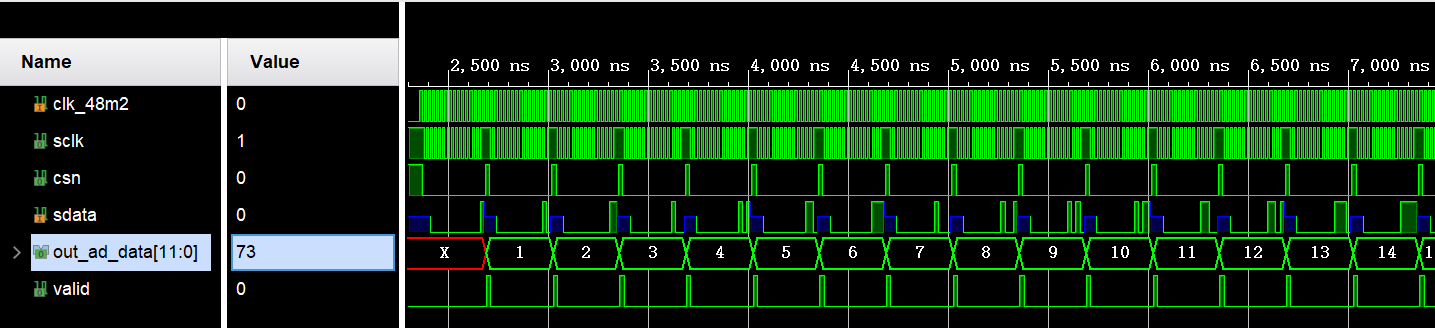

三、仿真:

设计一个文件用来模拟ad7274的接口,数据为计数器的值,转换成串行数据之后发送到adc解串模块,最后转换成12位并行adc的值out_ad_data,仿真结果如下:

可以看出,adc的值被正确转换了出来。

调试中遇到的问题:

硬件设计上,时钟被接入到了GTX专用管脚,导致不能直接进mmcm,因此需要做一下转换

// 时钟管脚为GTX专用管脚,需要用IBUFDS_GTE2转换

IBUFDS_GTE2 #(

.CLKCM_CFG("TRUE"), // Refer to Transceiver User Guide

.CLKRCV_TRST("TRUE"), // Refer to Transceiver User Guide

.CLKSWING_CFG(2'b11) // Refer to Transceiver User Guide

)

IBUFDS_GTE2_inst (

.O(clk_i_100), // 1-bit output: Refer to Transceiver User Guide

.ODIV2(), // 1-bit output: Refer to Transceiver User Guide

.CEB(1'b0), // 1-bit input: Refer to Transceiver User Guide

.I(clk_i_100_p), // 1-bit input: Refer to Transceiver User Guide

.IB(clk_i_100_n) // 1-bit input: Refer to Transceiver User Guide

);

//转换为全局时钟,以方便作Clocking Wizard mmcm输入

BUFG BUFG_inst (

.O(clk_i_100_glb), // 1-bit output: Clock output

.I(clk_i_100) // 1-bit input: Clock input

);

浙公网安备 33010602011771号

浙公网安备 33010602011771号