MMU 以及 TLB

MMU 以及 TLB

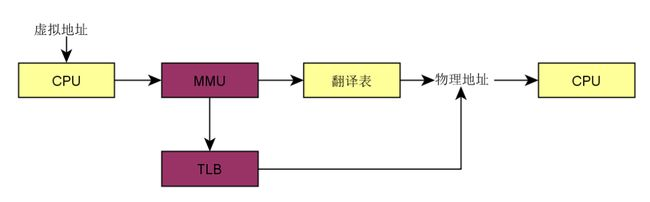

MMU(Memory Management Unit)内存管理单元:

-

一种硬件电路单元负责将虚拟内存地址转换为物理内存地址

-

所有的内存访问都将通过 MMU 进行转换,除非没有使能 MMU。

TLB(Translation Lookaside Buffer)转译后备缓冲器: 本质上是 MMU 用于虚拟地址到物理地址转换表的缓存

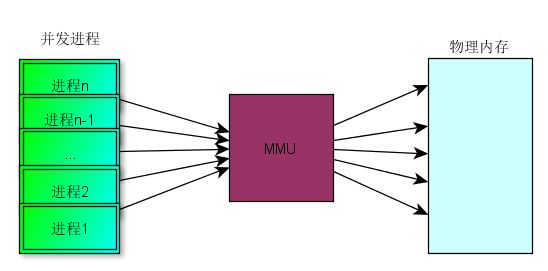

这样一种架构,其最终运行时目的,是为主要满足下面这样运行需求:

多进程并发同时并发运行在实际物理内存空间中,而 MMU 充当了一个至关重要的虚拟内存到物理内存的桥梁作用。

那么,这种框架具体从高层级的概念上是怎么做到的呢?事实上,是将物理内存采用分片管理的策略来实现的,那么,从实现的角度将有两种可选的策略:

固定大小分区机制

可变大小分区机制

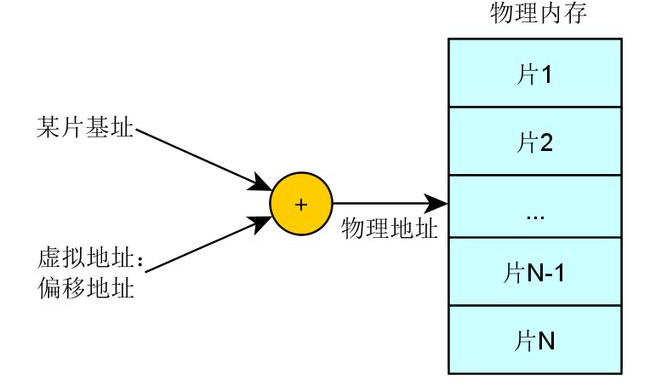

固定大小区片机制

通过这样一种概念上的策略,将物理内存分成固定等大小的片:

-

每一个片提供一个基地址

-

实际寻址,物理地址=某片基址+虚拟地址

-

片基址由操作系统在进程动态运行时动态加载

这种策略实现,其优势在于简易,切换快速。但是该策略也带来明显的劣势:

-

内部碎片:一个进程不使用的分区中的内存对其他进程而言无法使用

-

一种分区大小并不能满足所有应用进程所需。

可变大小分区机制

内存被划分为可变大小的区块进行映射交换管理:

-

需要提供基址以及可变大小边界,可变大小边界用于越界保护。

-

实际寻址,物理地址=某片基址+虚拟地址

那么这种策略其优势在于没有内部内存碎片,分配刚好够进程所需的大小。但是劣势在于,在加载和卸载的动态过程中会产生碎片。

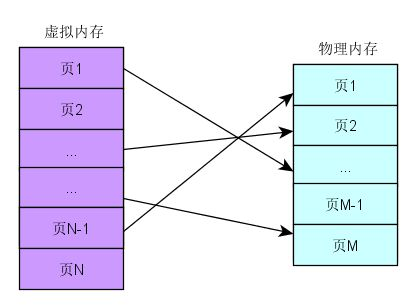

分页机制

分页机制采用在虚拟内存空间以及物理内存空间都使用固定大小的分区进行映射管理。

-

从应用程序(进程)角度看内存是连续的 0-N 的分页的虚拟地址空间。

-

物理内存角度看,内存页是分散在整个物理存储中

-

这种映射关系对应用程序不可见,隐藏了实现细节。

分页机制是如何寻址的呢?这里介绍的设计理念,具体的处理器实现各有细微差异:

-

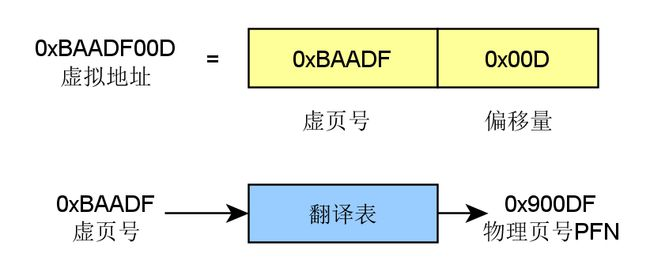

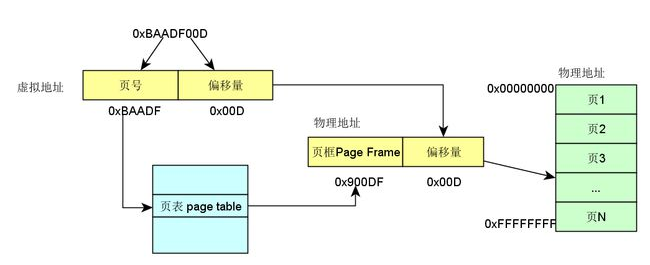

虚拟地址包含了两个部分:虚拟页序号 VPN(virtual paging number)以及偏移量

-

虚拟页序号 VPN是页表(Page Table)的索引

-

页表(Page Table)维护了页框号(Page frame number PFN)

-

物理地址由PFN::Offset进行解析。

举个栗子,如下图所示:

还没有查到具体的物理地址,憋急,再看一下完整解析示例:

如何管理页表

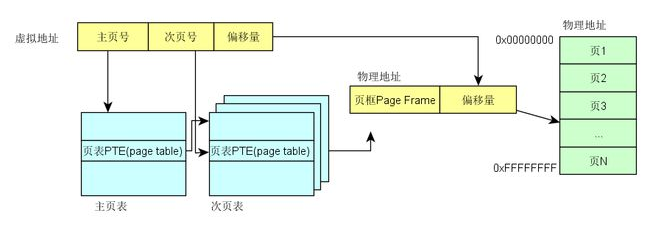

对于 32 位地址空间而言,假定 4K 为分页大小,则页表的大小为 100MB,这对于页表的查询而言是一个很大的开销。那么如何减小这种开销呢?实际运行过程中发现,事实上只需要映射实际使用的很小一部分地址空间。那么在一级页机制基础上,延伸出多级页表机制。

以二级分页机制为例:

单级页表已然有不小的开销,查询页表以及取数,而二级分页机制,因为需要查询两次页表,则将这种开销再加一倍。那么如何提高效率呢?其实前面提到一个概念一直还没有深入描述 TLB,将翻译工作由硬件缓存 cache,这就是 TLB 存在的意义。

-

TLB 将虚拟页翻译成 PTE,这个工作可在单周期指令完成。

-

TLB 由硬件实现

-

-

完全关联缓存(并行查找所有条目)

-

缓存索引是虚拟页码

-

缓存内容是 PTE

-

则由 PTE+offset,可直接计算出物理地址

-

TLB 加载

谁负责加载 TLB 呢?这里可供选择的有两种策略:

-

由操作系统加载,操作系统找到对应的 PTE,而后加载到 TLB。格式比较灵活。

-

MMU 硬件负责,由操作系统维护页表,MMU 直接访问页表,页表格式严格依赖硬件设计格式。

总结一下

从计算机大致发展历程来了解内存管理的大致发展策略,如何衍生出 MMU,以及固定分片管理、可变分片管理等不同机制的差异,最后衍生出单级分页管理机制、多级分页管理机制、TLB 的作用。从概念上相对比较易懂的角度描述了 MMU 的诞生、机制,而忽略了处理器的具体实现细节。作为从概念上更深入的理解 MMU 的工作机理的角度,还是不失为一篇浅显易懂的文章。

浙公网安备 33010602011771号

浙公网安备 33010602011771号