【电工基础知识】时序逻辑电路

时序逻辑电路

视频地址: 第11章 时序逻辑电路 https://www.icourse163.org/learn/HIT-1001998009?tid=1002098003#/learn/content?type=detail&id=1002858360&sm=1

定义

时序逻辑电路主要由触发器构成 。在数字电路理论中,时序逻辑电路是指电路任何时刻的稳态输出不仅取决于当前的输入,还与前一时刻输入形成的状态有关。这跟组合逻辑电路相反,组合逻辑的输出只会跟目前的输入成一种函数关系。换句话说,时序逻辑拥有储存器件(内存)来存储信息,而组合逻辑则没有。

从时序逻辑电路中,可以建出两种形式的有限状态机:

时序逻辑因此被用来建构某些形式的电脑的内存,延迟跟储存单元,以及有限状态自动机。大部分现实的电脑电路都是混用组合逻辑跟时序逻辑。

按“功能、用途”分为:

-

寄存器;

-

计数(分频)器;

-

顺序(序列)脉冲发生器;

-

顺序脉冲检测器;

-

码组变换器;

寄存器

定义

寄存器:能够暂时存放数码、指令、运算结果的数字逻辑部件,称为寄存器。

知识点概述:

1、寄存器,就是能够记忆或存储0和1数码的基本部件。通常都是由各种触发器和门电路来构成的。

2、寄存器分为仅能存储0和1数码的数码寄存器,和既能存储数码同时也能实现数码的左移或右移的寄位移寄存器。

3、在实际中,通常使用集成寄存器。本节讲解了寄存器的电路构成、工作原理、对74LS194双向移位寄存器的使用进行了介绍。

4、有点寄存器具有 左移 右移的功能

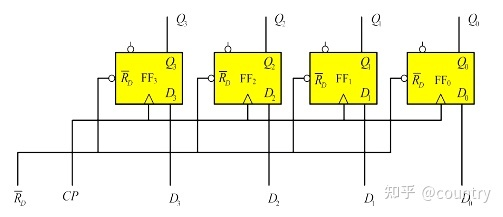

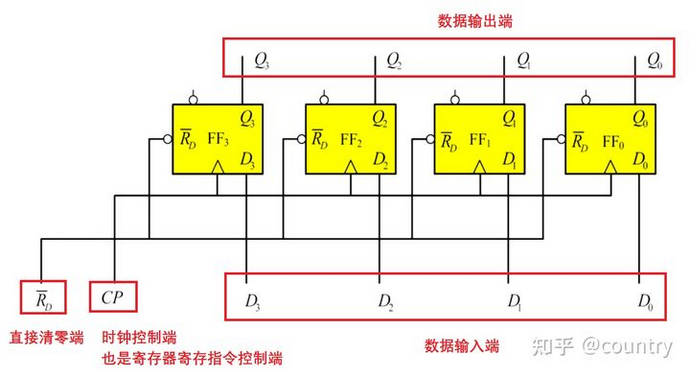

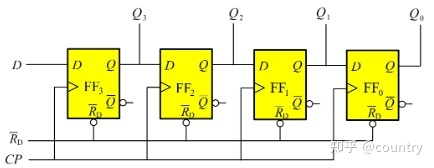

寄存器电路如下:

(1)由四个D触发器构成,因为每一个D触发器可以存放1位二进制信息,所以上述电路的寄存器可存放一个4位二进制数码,一般也把这种寄存器称为数码寄存器。

3、寄存器存放功能实现的过程:

(1)电路中的CP是时钟控制端,也是寄存器的寄存指令控制端。 是直接清零端,通过

给各个触发器清零,在电路正常工作时,

置为高电位。

~

是数据输入端。

~

是数据输出端,

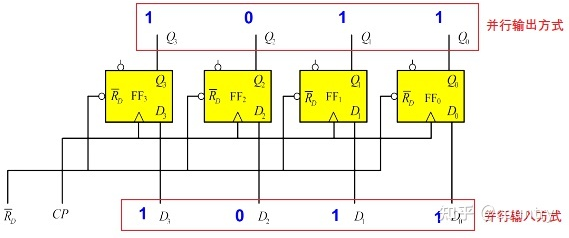

(2)假设要存储的二进制数码为1011,当 =1时,在控制寄存指令CP脉冲上升沿的作用下,根据D触发器的特性,输入端

~

的数码就一起送入了4各D触发器,输出端

、

、

此时置为1011,即完成了1011数码的寄存过程。

数码的寄存过程

总结:从这个寄存过程可以看出,寄存器在接受和输出数码信号时,各位数码都是同时打入到寄存器中的,输出端也即刻输出这组数码,这种输入输出的方式,称为并行输入、并行输出方式。

1.2左移寄存器

1、移位:在移位脉冲的作用下,每来一个时钟脉冲,寄存器数码便向右或向左移动一位,这种寄存器称为移位寄存器。

2、根据移位方式的不同,可分为单向移位寄存器、双向移位寄存器。

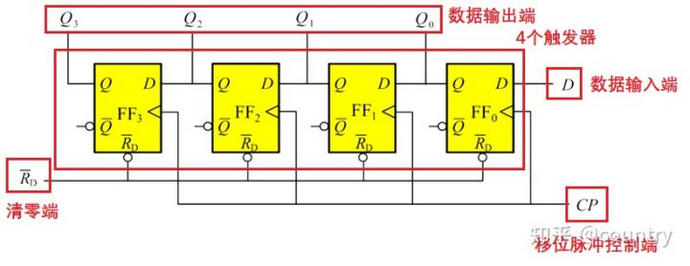

3、左移移位寄存器(单向)

左移移位寄存器

(1)D为数据输入端, ~

为4个触发器,每个触发器的输入、输出依次相连,

~

为数据输出端,CP为移位脉冲控制端,

为清零端。

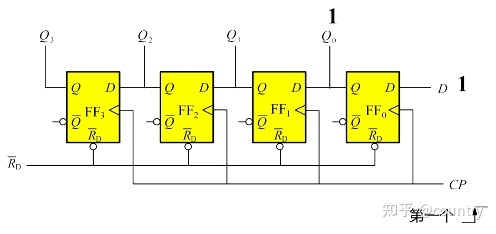

(2)为简便分析,假设通过 端清零信号将4个触发器全部清零,而我们准备存储的数码为1011,首先,D=1,第一个移位脉冲上升沿到来时,触发器

置1,则

=1,其他触发器仍然保持0态。

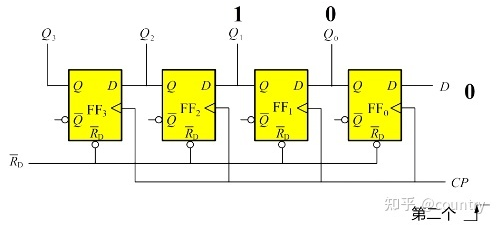

(3)接着,D=0,第二个移位脉冲上升沿到来时,触发器 置1,

置0,则

=1,

=0。

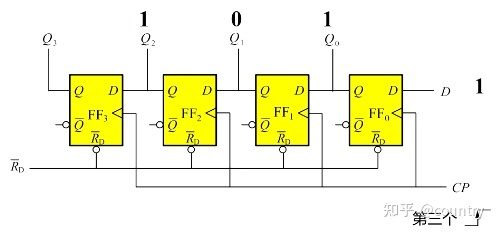

(4)再接着为D=1,第三个移位脉冲上升沿到来时,触发器 置1,

置0,

置1,则

=1,

=0,

=1。

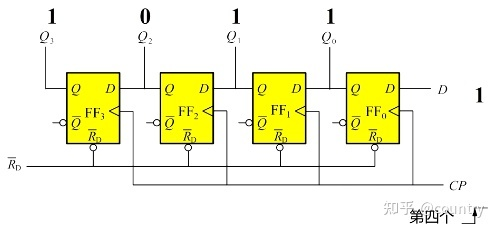

(5)最后一个数据,D=1,第四个移位脉冲上升沿到来时,触发器 置1,

置0,

置1,

置1,则

=1,

=0,

=1,

=1。

(6)在第四个移位脉冲过后,完成了存数过程,这时,从4个触发器的Q端,可以得到并行输出的信号。即经过4个脉冲后,1011这4位数码可以从 依次经历一边,此为串行输出。

1.2右移寄存器

1、右移寄存器:寄存器仍然由4个D触发器构成,与上面左移情况不同的是,串行数据是从 输入D端送入,触发器

的输出端接到

的输入端,依次类推。

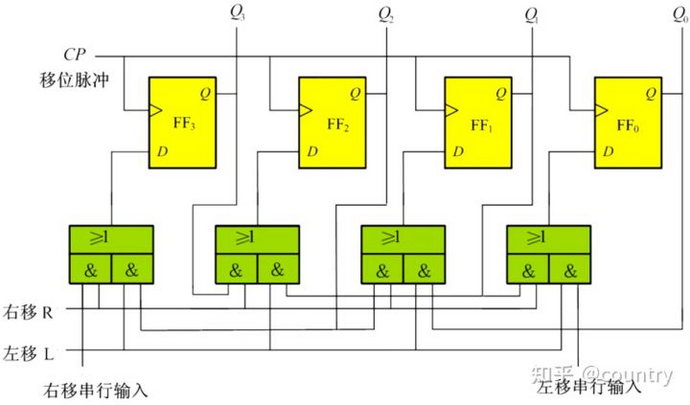

1.3双向移位寄存器

1、双向移位寄存器电路:既能实现左移,又能实现右移的寄存器。

(1)电路主要由4个D触发器构成,另外用与门和或门的组合来控制寄存器,来实现左移和右移的功能。

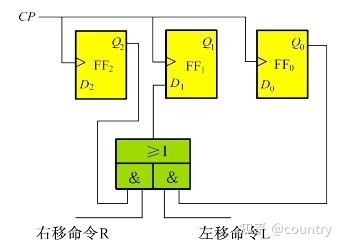

2、为了理解双向移位寄存器的工作过程,先分析移位触发器的情况:

(1)要想实现数码的右移, =

;要想实现数码的左移,

=

;

触发器的输入

=

+

,

从这个逻辑式可以看出,当R=1,L=0时, =

,此时实现的是右移;当R=0,L=1时,

=

,此时实现的是左移;

(2)将此分析过程应用到双向移位寄存器上,就可分析其左移和右移的过程了。

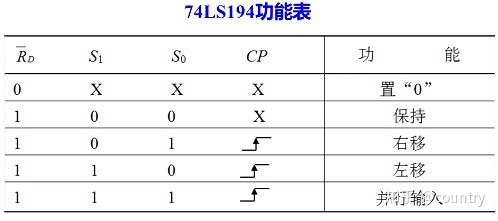

3、集成移位寄存器---74LS194四位双向移位寄存器

74LS194四位双向移位寄存器

(1) (1脚)数据清零端(低电平有效),

~

(3脚~6脚)并行数据输入端,

~

(12脚~15脚)并行数据输出端,

(2脚)右移串行数据输入端,

(7脚)左移串行数据输入端,

、

(9脚、10脚)为工作方式控制端,

(11脚)时钟脉冲输入端,

(2)74LS194功能表

- 当

=0时,输出端清零;

- 当

=1,

=

=0时,输出端处于保持状态;

- 当

=1,

=1,

=0时,当时钟脉冲上升沿到来时,数据

~

依次进行右移,实现右移的功能;

- 当

=1,

=0,

=1时,当时钟脉冲上升沿到来时,数据

~

依次进行左移,实现左移的功能;

- 当

=1,

=

=1时,当时钟脉冲上升沿到来时,数据

~

并行接收数据端

~

的数据,实现并行输入的功能;

计数器

定义

计数器是一种能够累计输入脉冲个数的时序逻辑电路。它主要由具有记忆功能的触发器构成。它不仅可用于对时钟脉冲计数,还可用于分频、定时、产生节拍脉冲和脉冲序列,还可进行数字运算等。

计数器分类

按计数脉冲引入方式,分为:

同步和异步计数器;

按进位制,分为:

二进制\十进制\N进制计数器

按逻辑功能:

分为加法:

减法和可逆计数器

按集成度,分为小规模与中规模集成计数器。

触发器

定义

在实际的数字系统中往往包含大量的存储单元,而且经常要求他们在同一时刻同步动作,为达到这个目的,在每个存储单元电路上引入一个时钟脉冲(CLK)作为控制信号,只有当CLK到来时电路才被“触发”而动作,并根据输入信号改变输出状态。把这种在时钟信号触发时才能动作的存储单元电路称为触发器,以区别没有时钟信号控制的锁存器。

浙公网安备 33010602011771号

浙公网安备 33010602011771号