PCB布局布线

在系统设计布局规划上,电源电路应该尽可能靠近负载电路;

散热回路应该尽可能靠近电源电路以减少热阻;

选择正确的板层数量和铜厚;

在有散热对流的板上,主义大尺寸的被动元件布局,不要阻碍芯片和MOSFET的空气对流;

板层堆叠问题:

4层:

#1power component;#2GND;#3small signal;#small signal/controller

放置一个地平面紧邻电源层以获取最小的环路阻抗,然后在考虑其他小信号层;

6层:

#1power component;#2GND plane;#3small signal;#4small signal;#5DC voltage or GND plane;#6power component/controller

相邻两层十字走线;

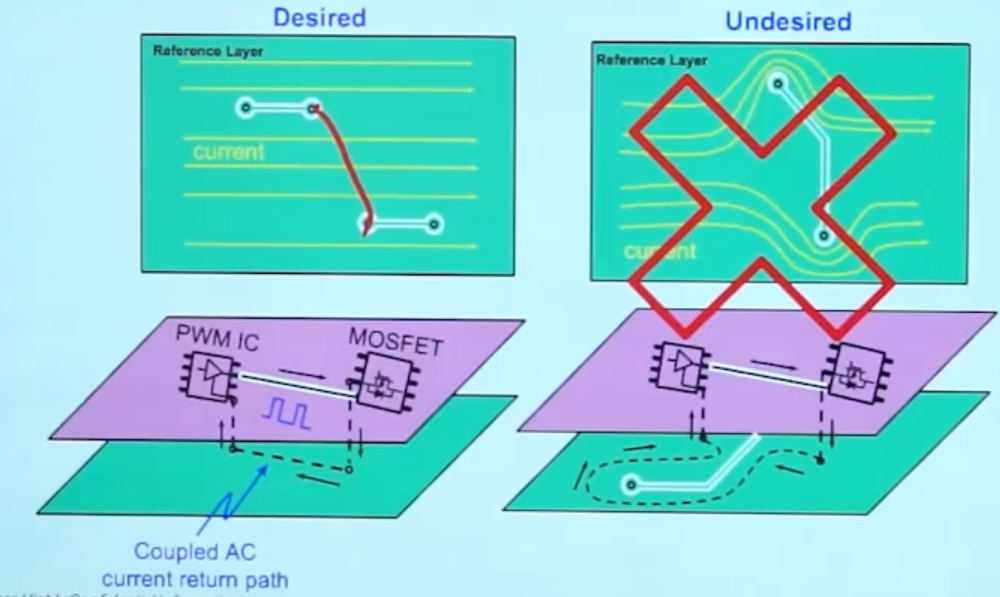

一般情况下,不要分割多层PCB设计的参考平面;

如果小信号走线不得不在参考层走线时,请选择对阻抗影响最小的走线而非横跨走线,以降低电源参考层的阻抗;

铜厚和宽度:

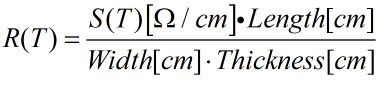

copper resistivity(欧姆/cm):S(T)=1.724*10^-6*(1+0.0039*(T-20));T,环境温度,℃

铜电阻:

thickness:

0.5 0z铜厚=0.7mil=17.78uM

1.0 0z铜厚=1.4mil=35.56uM

2.0 0z铜厚=2.8mil=71.12uM

4.0 0z铜厚=5.6mil=142.24uM

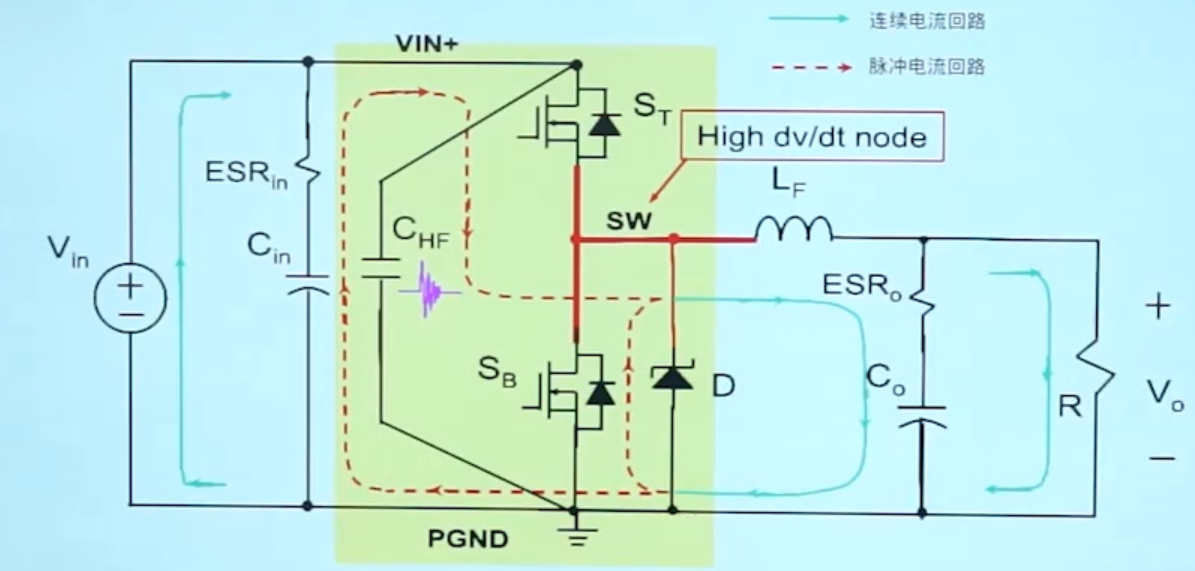

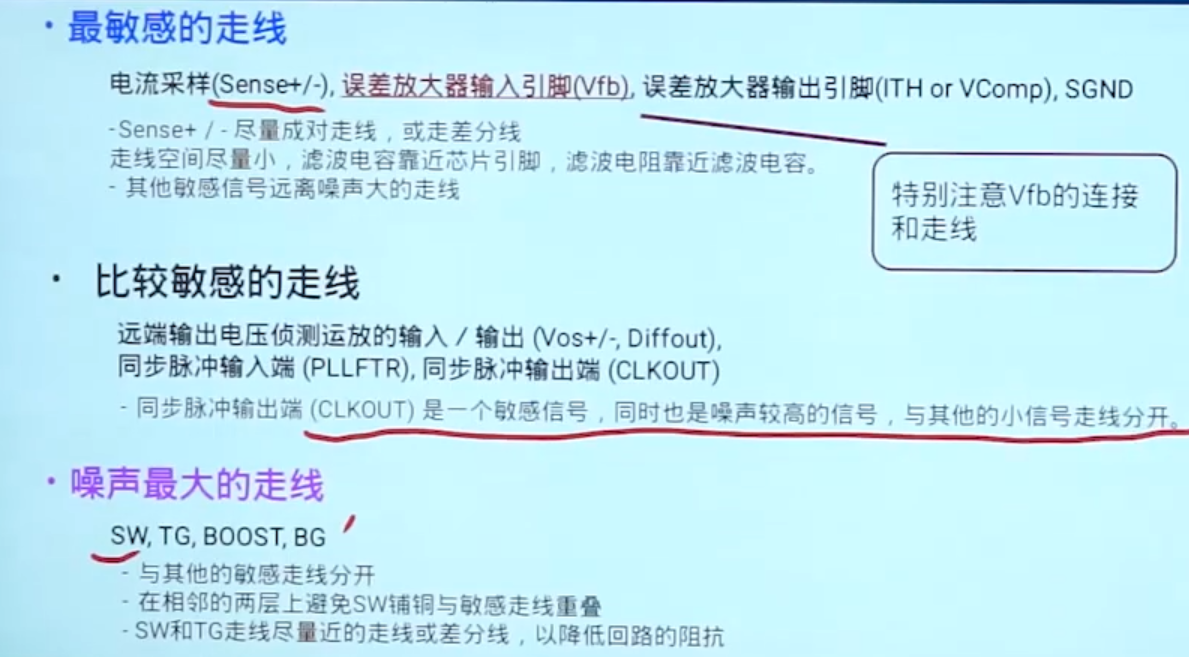

找到连续电流和断续电流的回路;

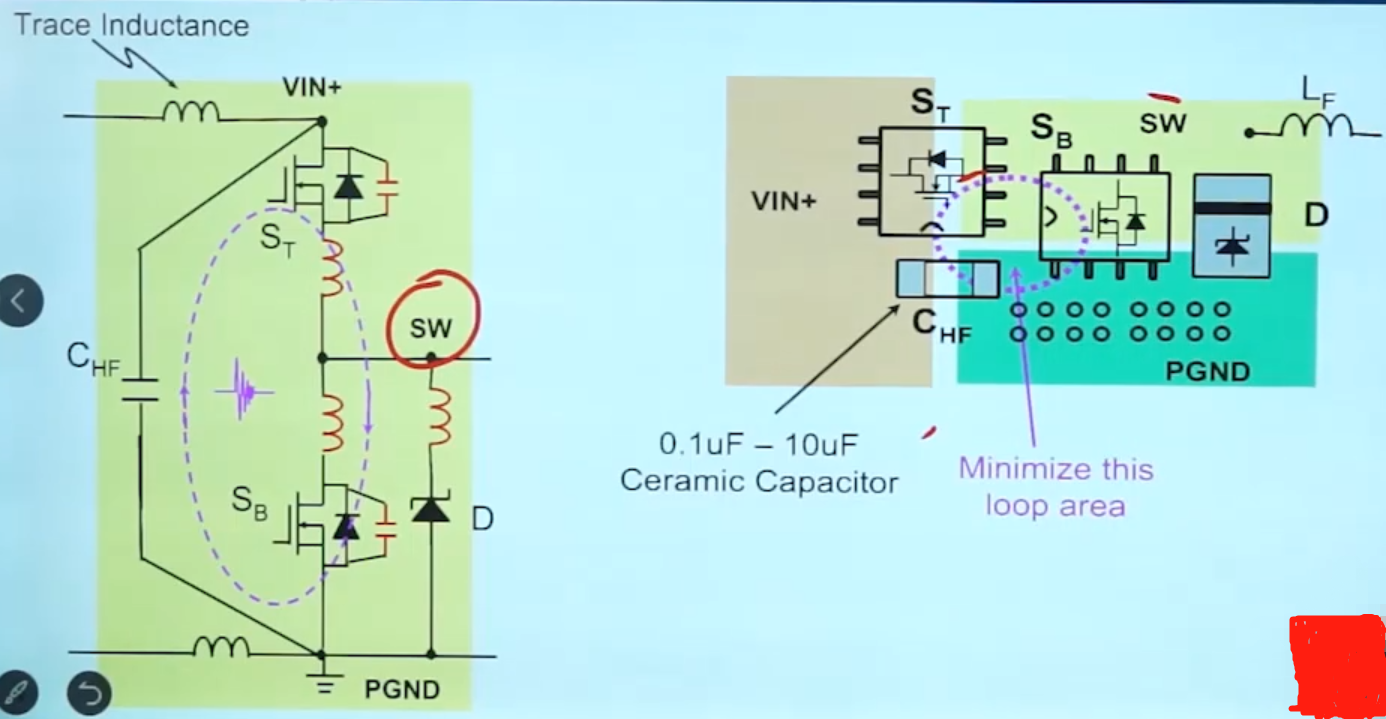

特别注意使得流过脉冲电流的回路面积最小,dv/dt的开关点与其他线路隔开;

高频滤波电容与MOSFET尽可能靠近放置;

尽可能使高频滤波电容,MOSFET的上官,下管在同一层面;

放置多个过孔降低功率回路的阻抗;

过孔电阻计算:孔壁面积来计算,计算公式同上;

功率器件铺铜尽可能宽,短;

层间连接用多个过孔降低阻抗;

功率元件焊盘与铜箔的连接禁止用很细的走线或则十字连接;

尽可能降低走线的阻抗;

去耦电容与分割地平面:

走线注意事项:

浙公网安备 33010602011771号

浙公网安备 33010602011771号