verilog,vhdl,bdf文件一起综合

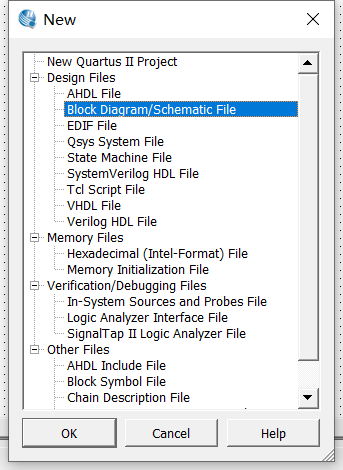

bdf文件创建:

对于FPGA来说,这三种文件都是对硬件电路描述,都是可以综合的,而且可以混合使用,一般想直观一点的话,可以用verilog 或则vhdl写模块,然后将代码文件实例化为元件,然后放入到bdf文件里面,将bdf文件设置为顶层文件,在bdf里面画好原理图即可综合了。

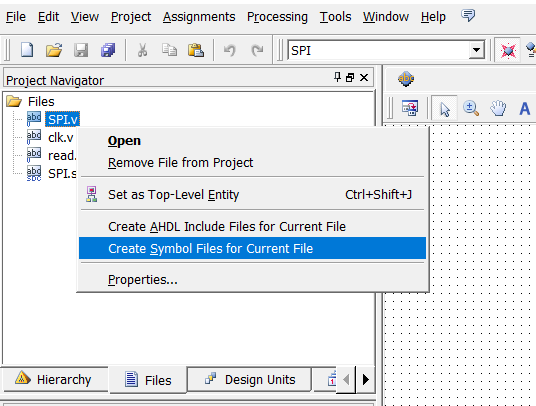

verilog 或则vhdl文件实例化为元件:选中文件,右键:

之后该模块就会实例化一个元件到当前工作目录,文件后缀是bsf文件。如果想去除这个实例化元件,就在当前目录下找到该元件文件,直接删掉就好。

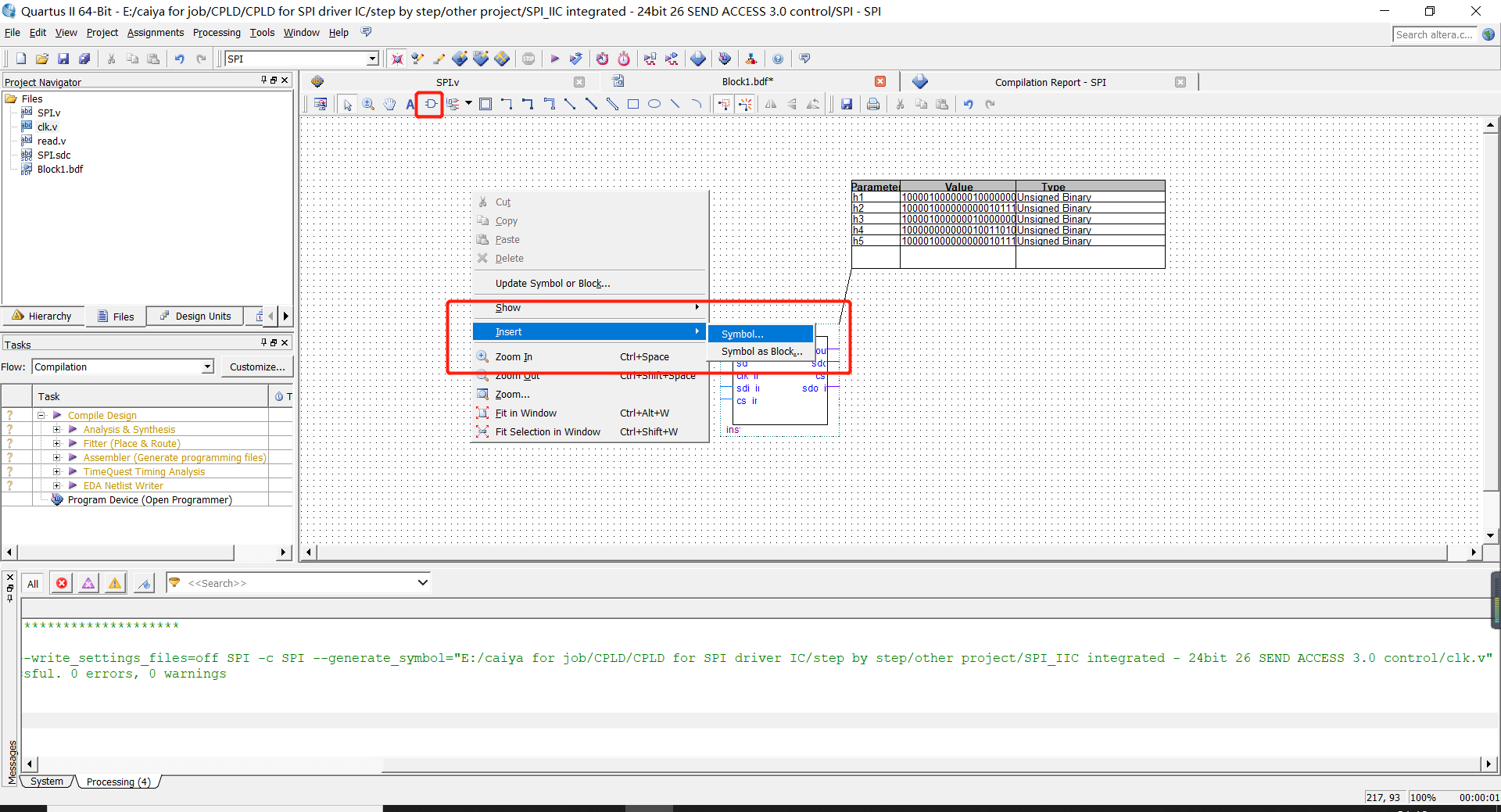

导入元件有两种方法,如图红色方框所示:

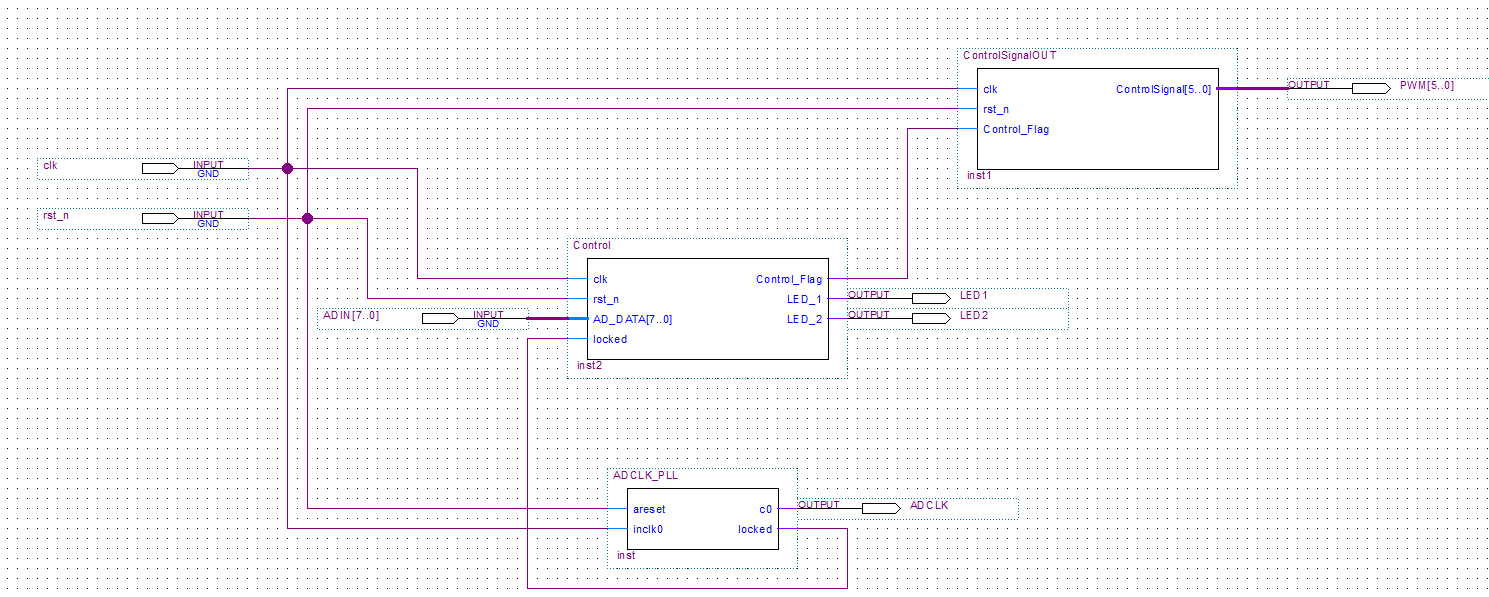

在原理图右键元件,还可以编辑元件显示的样式。

在原理图连接好各个元件的线,设置好输入输出端口,将原理图文件设置为顶层文件,集合编译综合了。

总结:verilog,vhdl,原理图三种方式都是对硬件电路进行描述的,是平行关系,可以混合使用综合。

浙公网安备 33010602011771号

浙公网安备 33010602011771号