FPGA--quartus 工程模板搭建

一,建立工程:

1,启动 Quartus12.1 开发环境, 选择菜单 File->New Project Wizerd。

2,在弹出的对话框中输入工程名和工程存放的目录, 点击 Next

,top-level design entity name跟工程名字一样。

3,add files 可以添加项目的设计文件,没有,就先不添加,点击 Next。

4,在接下来的对话框选择所用的 FPGA 器件型号 。

5,Simulation 这一项我们选择已经安装的 ModelSim,格式选择 Verilog HDL。

二,代码编写:

1,新建 LED 的 verilog 代码文件(点击菜单 File->New....)

2,在弹出的窗口中选择 Verilog HDL File 项, 点击 OK。 (这里 Altera 的设计文件种类有很多,但对于用户来说学好其中最常用的一两种就已经足够了)

3,编写代码如下:代码介绍见:https://www.cnblogs.com/caiya/p/9865463.html

`timescale 1ns / 1ps module LED( clk, // 开发板上输入时钟: 50Mhz rst_n, // 开发板上输入复位按键 led // 输出 LED 灯,用于控制开发板上四个 LED(LED0~LED3) ); input clk; input rst_n; output [3:0] led; //寄存器型数据对象的定义 reg [31:0] timer; reg [3:0] led; always @(posedge clk or negedge rst_n) begin if(~rst_n) timer <=0; else if(timer==32'd199_999_999) timer<=0; else timer<=timer+1'b1; end always @(posedge clk or negedge rst_n) begin if(~rst_n) led<=4'b0000; else if(timer==32'd49_999_999) led<=4'b0001; else if(timer==32'd99_999_999) led<=4'b0010; else if(timer==32'149_999_999) led<=4'b0100; else if(timer==32'd199_999_999) led<=4'b1000; end endmodule

4,编写好代码后点击保存按钮, 另存为LED.v ,在 Files 界面,我们可以看到 LED.v 文件已经自动添加到项目中的 files 下 ;

三,管脚约束和编译 :

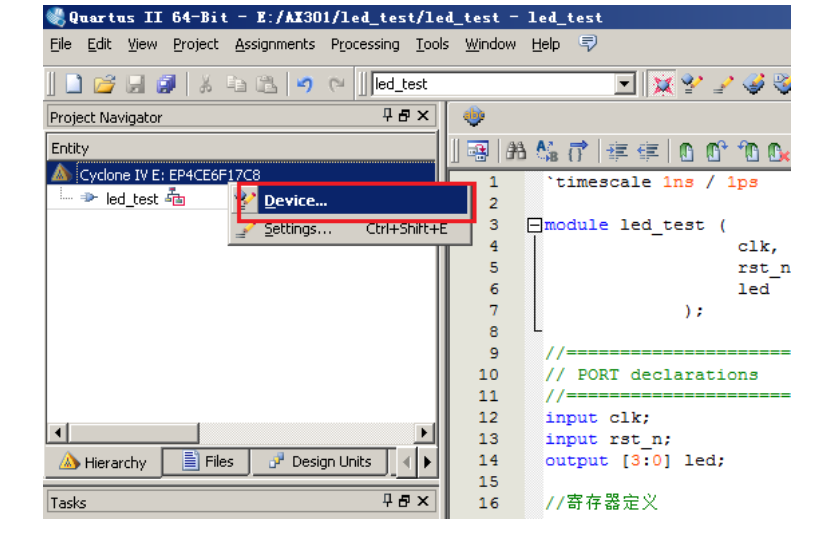

1,编译前先配置一下 IO 的电压和双功能管脚的功能,右键选中 Cyclone IV E FPGA 芯片,选择 Device。

2,点击 Device and Pin Options 按钮。

3,设置 DCLK, Data[0]....等这些双功能的 Pin 为普通的 IO,设置 I/O 的 Default 电压为 3.3-V LVTTL, 设置完成后点击 OK。

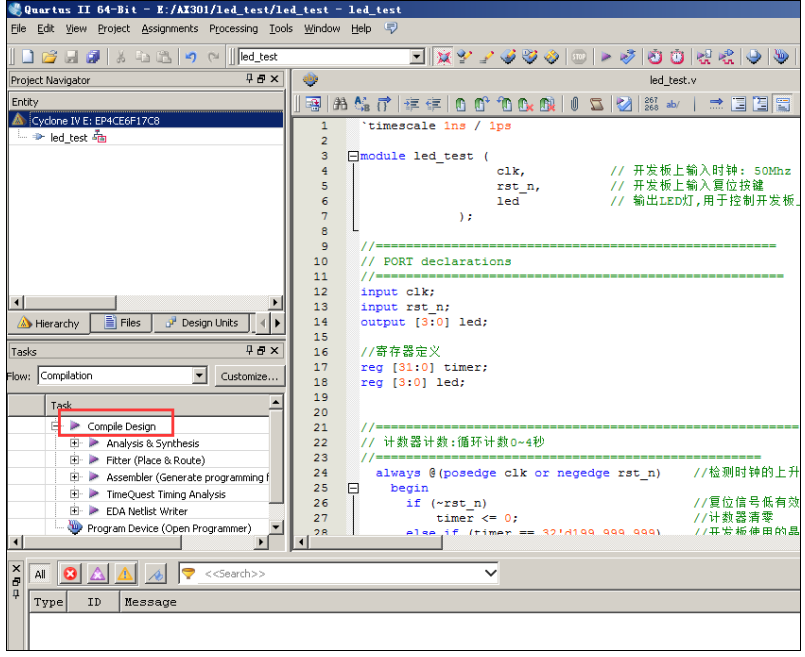

4,点击 compile Design 按钮开始编译工程。

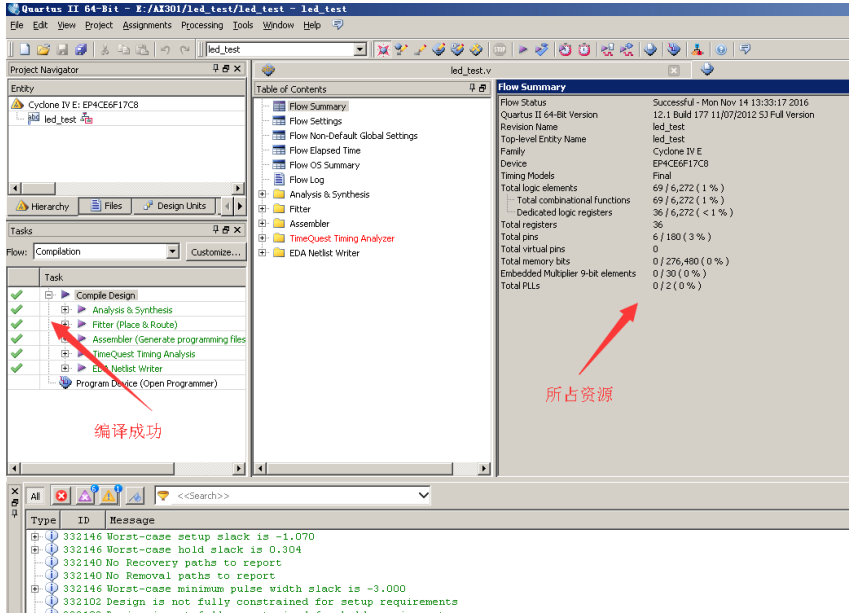

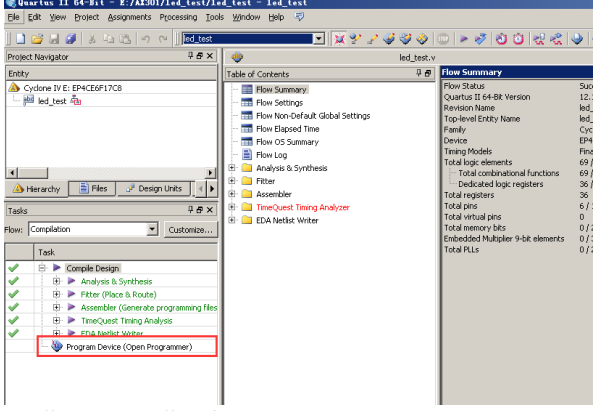

5,编译成功的话, 编译窗口的每一项前面会出现一个绿色的勾, 我们在 Flow Summary 窗口可以观察 FPGA 资源使用的情况

;

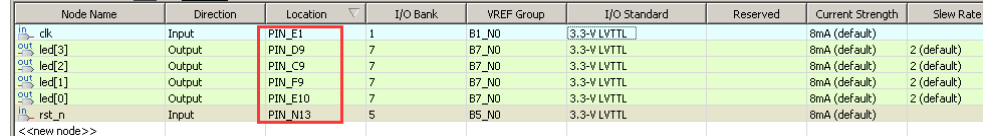

6,我们再来为 led_test 添加管脚约束,让编译器知道工程中的每个端口信号对应 FPGA 的哪个管脚。 选择菜单 Assignment->Pin Planner

;

7,在 Location 这列输入每个信号对应 FPGA 管脚号, 这个管脚具体的对应关系大家需要参考开发板的用户手册或者原理图,这里的复位管脚"rst_n"我们使用开发板上的按键 Reset 作为复位管脚。 输入管脚号后如下图:

四,时序的约束 :(个人觉得简单系统一般不需要这个)

时序约束是告诉 Quartus 编译器在编译程序的时候需要按照你的时序要求去布局布线。一般的项目只需要对全局时钟进行约束,高速信号的设计还需要对各个节点,输出输入端口的延迟进行约束。

以下为全局时钟约束的方法:

1. 点击菜单 Tool->TimeQuest Timing Analyzer, 打开 TimeQuest Timing Analyzer 界面。

2. 点击菜单 Tools->TimeQuest Timing Analyzer Wizard..

3. 进入 TimeQuest Timing Analyzer Wizard 向导,点 Next

4. 这里我们增加了一个时钟的约束, clock Name 项输入 clk, input Pin 项选择 clk, period是时钟周期,这个要和板子上的输入时钟周期一样,我们板上的时钟输入是 50Mhz, 也就是20ns, Rising 设置为 0, Falling 设置为 10,这样时钟的占空比就是 50%。

5, 接下来是输入管脚对应时钟的约束,这里是定义高速输入的数据对于时钟的约束,比如数据的 setup 的时间(tsu)和 holdup 的时间(th)。因为这里输入信号只有 rst 信号,是个按键复位,无需约束。点击 next

。

6,接下来是输出管脚对应时钟的约束,也是设置输出管脚对于时钟上升沿的数据最小保持时间(mintco)和最大保持时间(tco)。在本例程中我们只输出 LED 灯,这项也没有必要设置,点击next。

7,程序会自动生成一个 LED.sdc 的约束文件,并添加到工程中。点击 Finish。

8,关闭 TimeQuest Timing Analyzer 窗口,在 Quartus 的 Files 栏里我们可以看到一个LED.sdc 文件已经添加到项目中。

五,编译和 FPGA 下载 :

1. 全部保存工程, 再点击 compile Design 按钮重新编译一下工程。

2. 编译完成后, Quartus 会在 output file 文件夹内生成一个 led_test.sof 文件,下面我们会使用这个 sof 文件来下载 FPGA。

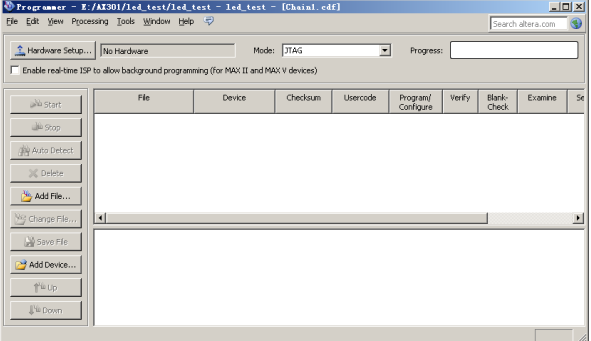

3. 现在我们可以把 SOF 文件下载到 FPGA 芯片中,看一下 LED 实际运行的效果。 在下载程序之前先要确认下载器已经连接, FPGA 开发板已经上电。 再点击 Program Device(OpenProgrammer) 打开 Programmer 软件进行 FPGA 的下载。

4. 打开后的 Programmer 的界面如下图所示:

5. 点击“Hardware Setup...”按钮 。

6. 在 Hardware Setup 的界面里选择 Currently Select hardware 为 USB-Blaster[USB-0],再点击 Close。

7. 再来添加我们刚才生成的 LED.sof 文件,点击“Add File...”按钮添加。

8. 打开 output_files 目录下的 led_test.sof 文件。

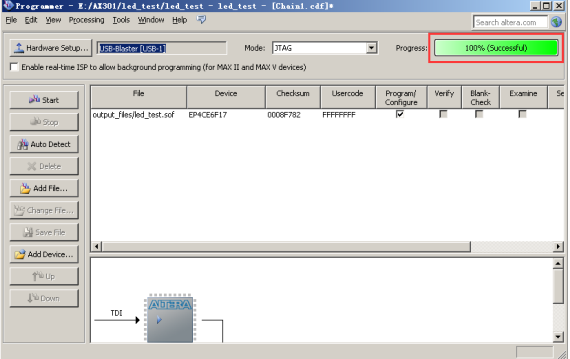

9. 点击"Start"按钮开始 Program FPGA。

10,下载成功, Progress 栏会出现 100%(Successful)的字样。

六,JIC 文件生成 :

可能已经有朋友发现下载 SOF 文件到 FPGA 后,开发板重新上电后配置程序已经丢失,还需要 JTAG 重新下载。这岂不麻烦!好吧,这一节我们来介绍如何把 FPGA 程序下载到开发板上的 FLASH 中,这样不用担心掉电后程序丢失了。在我们的开发板上有一个 8Pin 的 16Mbit 的 SPI FLASH M25P16, 用于存储 FPGA 的配置程序。我们不能直接把 SOF 文件下载到这个 FLASH 中,需要先把 SOF 文件转换成 JIC 文件。下面是 SOF 文件转换成 JIC 文件的具体步骤:

1 . 在 Quartus 中选择菜单 File→Convert Programming File...

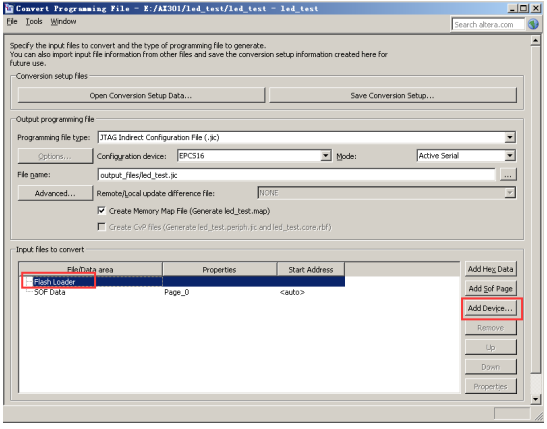

2. 在 Convert Programming File 界面里选择输出的文件类型为.jic; Configuration device为 EPCS16, 这个型号跟我们开发板上的 M25P16 是兼容的 ; File name 栏输入 JIC 文件的存放地址和文件名,这里我们输入LED.jic,保存在 output_files 目录下。

3. 选中 Input files to convert 框里的 Flash Loader, 点击右边的“Add Device...”按钮 。

4,在 Device family 列表里选择"Cyclone IV E", Devices name 框中选中 EP4CE6(如果是AX4010 的用户选择"EP4CE10"),再点击 OK 完成。

5. 再选中 Input files to convert 框里的 SOF Data, 点击右边的“Add File...”按钮添加 SOF文件。 选择 output_files 目录下的 LED.sof 文件,并打开。

6.点击“Generate”按钮生成 JIC 文件 。出现 Success 对话框, jic 文件生成成功。

【】生成了 JIC 文件后,我们就可以通过 JTAG 把 JIC 文件下载到开发板的 FLASH 中了。

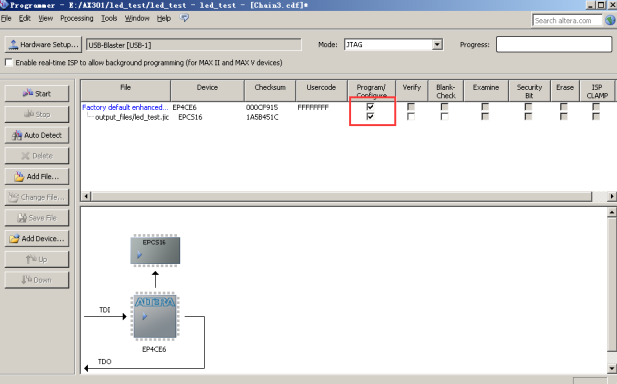

1 . 双击 Quartus 界面里的 Program Device 打开 Programmer 界面。

2. 点击"Add File..."按钮添加编程文件。 选择刚才生成的 led_test.jic 文件并打开。

3. 选中 Program/Configure 列中的选择框。

4. 点击"Start"按钮开始对 Flash 进行编程。

等待 Progress 状态为 100%(Successful), Flash 烧写成功。

浙公网安备 33010602011771号

浙公网安备 33010602011771号