STM32:cm3内核概览

1 架构

芯片架构是以指令集架构和存储架构为基础,加上各种功能单元搭建而成的交互接口标准;

ARM(Advanced RISC Machine)高级 精简指令集 处理器,简称ARM架构;是嵌入式微处理器的主流芯片架构;

1.1 主流芯片架构

| CPU架构 | 代表芯片 | 指令集架构 | 功能 |

| ARM | ARM | RISC指令集 | 主要用于移动,嵌入式领域;逻辑门少,发热低,so功耗低;搭配哈佛存储结构使用; |

| X86 | intel,AMD | CISC指令集 | 主要是用在电脑CPU上,性能高,速度快;搭配冯诺依曼存储结构使用; |

| MIPS | 龙芯 | RISC指令集 | 用于部分音频处理器,网络设备上和北斗卫星上,市场极小任重道远; |

| RISC-V | RISC-V指令集 | 开源免费的指令集,在国与国意识形态分裂下,前景较好;还在流片试验阶段; |

写博客的时候还没有risc-v的芯片,现在gd32f1已经用上risc-v了,速度很快呀,这两年嵌入式行情是真好,没去上班从职业角度看确实可惜;

1.2 指令集架构

通过软件对硬件寄存器进行操作的指令接口标准,称之为指令集架构;

1.2.1 CISC(complex instruction set computer) 复杂指令集;

1.2.2 RISC(Reduced Instruction Set Computer) 精简指令集;是基于CISC精简优化后得到的指令集架构;

1.2.3 RISC-V指令集;是基于RISC优化后得到的第五代开源免费的指令集架构;

1.3 存储架构

1.3.1 哈佛结构:指令寄存器和数据寄存器存放在不同的内存里,需要分别寻址的CPU结构;

1)代码编译之后相当于指令,这些指令通常会固定存放在单片机的rom的寄存器里,使用指令总线来顺序寻址指令寄存器;

相当于指令寄存器全部划分在一块固定的区域,指令总线和数据总线同时操作该区域的指令寄存器;

2)单片机执行过程中的数据存放在ram的寄存器里,使用地址总线对需要操作的数据寄存器进行寻址,然后使用数据总线传递数据;

相当于数据寄存器全部划分在一块固定的区域,地址总线和数据总线可以同时操作该区域的数据寄存器;

优势:代码安全性较高,效率较高;

1.3.2 冯诺依曼结构:指令寄存器和数据寄存器存放在相同的内存里,不需要分别寻址的CPU结构;

代码A编译之后存放在内存中,该代码A使用的数据A存放在代码A地址后;新的代码B继续放在数据A之后,然后再存放数据B...

指令寄存器的存储区域和数据寄存器的存储区域混在一块区域,也就是说指令总线和地址总线是相同的总线,需要分时复用;

冯诺依曼是早期的cpu结构,执行的速度由处理器速度限制;优势的话。。。可能在处理器速度很快的情况下很快把。。。

1.4 字节存储(endian)顺序

| endian模式 | 功能 | data[31:0]=0x87654321, 地址:0x0000 0010,0x0000 0011,0x0000 0012,0x0000 0013 |

| 小端模式 | 数据的低位存放在地址低位中 | data[7:0]存放在0x0000 0010中 |

| 大端模式 | 数据的高位存放在地址低位中 | data[31:24]存放在0x0000 0010中 |

cortex-m3内核有些指令只使用小端模式存储;

1.5 cortex系列内核

ARM公司作为IP(intellectual property)知识产权服务提供商,专注于ARM架构的芯片设计出售;

以ARM架构为基础的芯片设计是芯片的软件系统核心部分,通常将其称为内核(core system);

ARM公司推出了多种芯片内核,具体官网,此处我们只了解一下cortex系列内核;STM32采用cortex-M系列内核来具体执行和实现功能;

1) cortex-A系列内核:application系列,专注于高端消费类电子,诸如高通,MTK等的手机芯片;

2) cortex-R系列内核:real-time系列,专注于要求实时性的领域,诸如航空航天之类的;

3) cortex-M系列内核:micro-controller系列,专注于中低端的嵌入式产品,也就是本文接下来要说的系列了;

2 cortex-M3存储器地址映射

ARM的地址总线为32bits;所以存储器的寻址空间为4G;寄存器最小单位是8位寄存器,8bits可存储1byte;每个32位地址寻址1个寄存器;

CM3存储器地址映射在所有的cortex-m3内核的芯片上都是相同的,方便了不同芯片程序的裁剪和移植;

| 地址 | 大小 | 类型 | 功能 |

| 0x0000 0000-0x1fff ffff | 512M bytes | flash | 代码存储区 |

| 0x2000 0000-0x3fff ffff | 512M bytes | SRAM | |

| 0x4000 0000-0x5fff ffff | 512M bytes | 用于存储片上外设 | |

| 0x6000 0000-0x9fff ffff | 1G bytes | 外部RAM | 扩展外部存储器的寻址 |

| 0xa000 0000-0xdfff ffff | 1G bytes | 扩展片外的外设 | |

| 0xe000 0000-0xffff ffff | 512M bytes | 内核相关寄存器,片上调试组件等,AHB总线,APB总线 |

3 cortex-M3内核

cortex-m3为cortex系列推出的第一个内核,发布于2005年;本文就以cortex-m3举例,stm32f1系列使用cortex-m3内核;

cortex-m3为32位处理器内核;数据总线,指令总线,地址总线,寄存器都是32位的,采用哈佛结构总线;

cortex-m3只使用thumb-2指令集;thumb-2指令集包含32bit指令和16bit指令;thumb指令集只包含16bit指令;

以下为cm3内核的架构框图,橙色是内核核心功能,紫色为调试组件,绿色为存储保护单元,蓝色为内部总线与外设的接口;

I-code总线负责指令寻址,D-code总线负责查表等操作;

AHB总线只用于CM3内部的AHB外设,如NVIC,FPB,DWT和ITM;APB总线既用于CM3内部的APB外设,也用于片外扩展的外设;

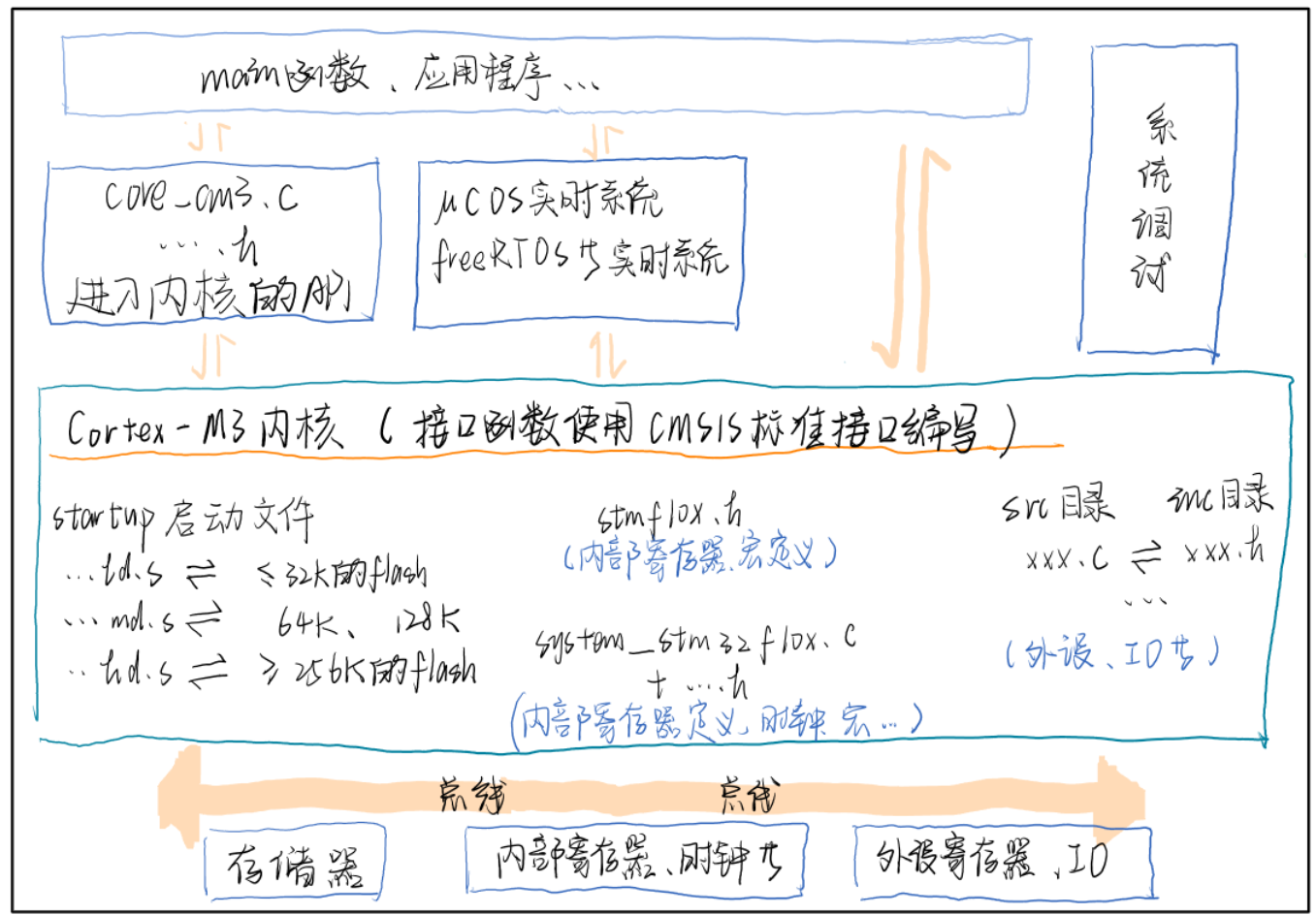

3.1 CMSIS 程序接口标准

CMSIS全称Cortex-Mx software interface standard,是cortex-M系列内核的API应用程序接口标准;

以下为cm3内核的代码架构分层示意图;分别是用户层的应用程序,实时操作系统层,内核程序接口层(CMSIS标准编写),硬件寄存器外设层;

Libraries目录下内核代码,将底层寄存器操作封装成API函数,函数格式符合CMSIS标准的格式;CMSIS如下图第三部分所示;

3.2 register bank寄存器

CM3内核拥有一个寄存器组,该寄存器组内共有16个寄存器;以及一些特殊功能寄存器;

3.2.1 寄存器组

| 寄存器 | 寄存器名称 | 可访问指令 | 功能 |

| R0,...,R7 | 通用寄存器 | thumb, thumb-2 | 数据操作,Low registers复位后初始值不定 |

| R8,...,R12 | 通用寄存器 | thumb-2 | 数据操作,High registers复位后初始值不定 |

| R13 | 主堆栈指针 MSP | thumb-2 | main_SP,复位后缺省使用的堆栈指针,用于操作系统内核以及异常处理例程(包括中断服务例程); |

| 进程堆栈指针 PSP | thumb-2 | process_SP,由用户的应用程序代码使用(用户代码不处于中断时); | |

| R13寄存器的最低两位被硬件置0,所以内存的地址总是4字节对齐;堆栈指针的切换由硬件自动完成; | |||

| R14 | 连接寄存器 LR | thumb-2 | 调用子函数时,用来存储主调函数的地址;多级调用时会将主调函数的地址存到堆栈中; |

| R15 | 程序计数器 PC | thumb-2 | 存储当前程序运行到的程序地址。如果修改它的值,就能改变程序的执行流; |

3.2.2 特殊功能寄存器

特殊功能寄存器组没有存储器地址,只能使用MRS(读)和MSR(写)指令访问;

| 寄存器 | 寄存器名称 |

功能 |

|||

|

xPSR

|

程序状态字

寄存器组

|

APSR

|

APSR 应用程序状态寄存器:记录 ALU 标志,

IPSR 中断号状态寄存器:当前正服务的中断号,

EPSR 执行状态寄存器:程序执行状态

|

||

|

IPSR

|

|||||

| EPSR | |||||

|

PRIMASK

|

中断屏蔽

寄存器组

|

1bit |

除能所有中断,NMI和hard fault除外; 缺省为0,不除能; |

目的:让实时性要求高的任务能够顺利执行 |

|

|

FAULTMASK

|

1bit |

除能所有fault,NMI不可屏蔽中断除外; 缺省为0,不除能; |

|||

|

BASEPRI

|

9bit

|

除能所有优先级不高于某个阈值的所有中断

|

|||

|

CONTROL

|

控制

寄存器

|

CONTORL[1]

|

1bit |

为0时,都使用MSP堆栈指针;为缺省值;

为1时,thread使用PSP堆栈指针,

handler使用MSP指针;

|

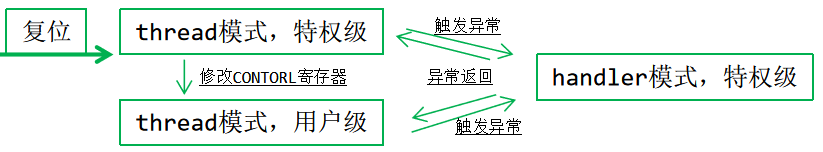

handler模式时,为0,都是使用MSP堆栈, thread模式时,为0或1,分别复用为MSP/PSP堆栈; |

| CONTROL[0] |

1bit

|

0:thread模式处于privileged特权级权限; 1:thread模式处于user级权限 |

当模式处于thread时,使用CONTROL[0]来配置权限 | ||

| 操作模式 | 操作权限 | 操作程序 | 使用的堆栈指针 | 操作配置 |

| thread 线程模式 | 特权级,用户级 | 普通应用程序的操作模式 | PSP/MSP |

根据操作模式和操作权限配置CONTROL[1:0]来修改状态 |

| handler 处理模式 | 特权级 | 异常服务程序的操作模式 | MSP |