modelsim学习笔记(1)

modelsim作为轻量级fpga仿真软件,可以让开发者在不需要连接硬件的情况下进行仿真,非常方便。下面是我在学习使用modelsim的一些记录。

在安装好modelsim之后,首先进入主界面。

在开始写程序之前,我们首先要建立一个自己的库,在file菜单栏找到new这里将库命名为work1。

在建立好库之后,在这个库的目录下建立新的工程,将工程命名为pro1。

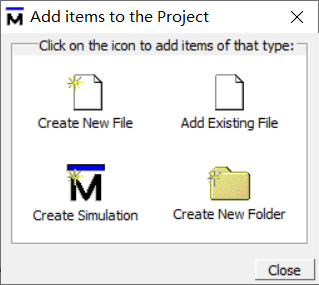

建立好工程以后会出现下面这个界面,我们要写新的程序所以选择create new file

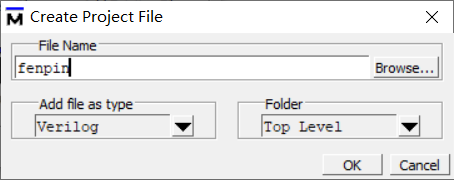

在新出现的界面中设置文件名和使用的语言,这里我选择verilog然后创建即可生成一个空的fenpin.v文件

在主程序外,我们还需要一个测试文件,按照上面的操作再建立一个fenpin_test.v文件

我希望实现一个分频的功能,那么实现思路就是分频信号在指定的时钟上升沿变化,这样分频信号的频率就是时钟的1/n,达到分频的要求。

这里就用最简单的2分频来说明

module fenpin( input clk, input rst, output clk_s ); reg clk_s1; always @(posedge clk or negedge rst) begin if (rst==1'b0) begin clk_s1<=0; end else begin if (clk==1'b1) clk_s1 <= ~clk_s1; end end assign clk_s=clk_s1; endmodule

分频功能实现以后,需要测试文件来验证功能的正确,通过生成一个时钟信号,调用分频模块,观察输出信号是否正确。

`timescale 1ns/1ns module fenpin_test; reg clk; reg rst; initial begin clk=0; #5 rst=0; #6 rst=1; end always #20 clk= ~clk; fenpin U1( .clk(clk), .rst(rst), .clk_s(clk_s) ); endmodule

下面是一些调试上面程序时的经验教训:

一定要缩进,结构清晰可以减少调试时间。

模块输出可以在最后用中间的reg变量来assign赋值

模块尽量保证复位功能,复位通常用下降沿检测。

测试程序一定要初始化复位信号,令其从低电平到高电平保持,否则仿真输出波形会出现STX的红线。

浙公网安备 33010602011771号

浙公网安备 33010602011771号