Bryce1010的微机接口课设

- 8086CPU知识回顾

8086 CPU 中寄存器总共为 14 个,且均为 16 位 。

即 AX,BX,CX,DX,SP,BP,SI,DI,IP,FLAG,CS,DS,SS,ES 共 14 个。

而这 14 个寄存器按照一定方式又分为了通用寄存器,控制寄存器和段寄存器。

通用寄存器

AX,BX,CX,DX 称作为数据寄存器:

AX (Accumulator):累加寄存器,也称之为累加器;

BX (Base):基地址寄存器;

CX (Count):计数器寄存器;

DX (Data):数据寄存器;

SP 和 BP 又称作为指针寄存器:SP (Stack Pointer):堆栈指针寄存器;

BP (Base Pointer):基指针寄存器;

SI 和 DI 又称作为变址寄存器:

SI (Source Index):源变址寄存器;

DI (Destination Index):目的变址寄存器;

控制寄存器:

IP (Instruction Pointer):指令指针寄存器;

FLAG:标志寄存器;

段寄存器:

CS (Code Segment):代码段寄存器;

DS (Data Segment):数据段寄存器;

SS (Stack Segment):堆栈段寄存器;

ES (Extra Segment):附加段寄存器;

- 74273就是一个8位的数据锁存器。

第1脚是复位脚,平时应保持高电平;低电平时1Q~8Q输出全部低电平,同时内部寄存器全部清零。

1D~8D为数据输入,在11脚(CLK)从低电平跳变到高电平时(即上跳沿),1D~8D被保存到74273寄存器中,同时1Q~8Q输出对应1D~8D的电平。

第1脚保持高电平,第11脚为低电平、高电平、高电平到低电平跳变(下跳沿)这些状态对输出1Q~8Q及74273内部保存的数据无影响。

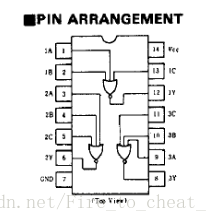

7427芯片

输入端三或非门

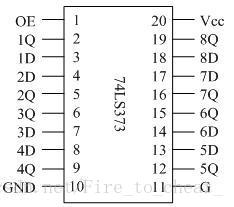

对74373

(1).1脚是输出使能(OE),是低电平有效,当1脚是高电平时,不管输入3、4、7、8、13、14、17、18如何,也不管11脚(锁存控制端,G)如何,输出2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)全部呈现高阻状态(或者叫浮空状态);

(2).当1脚是低电平时,只要11脚(锁存控制端,G)上出现一个下降沿,输出2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)立即呈现输入脚3、4、7、8、13、14、17、18的状态.

对373来说,1脚接低电平,保证使能,11脚直接接单片机的ALE信号.

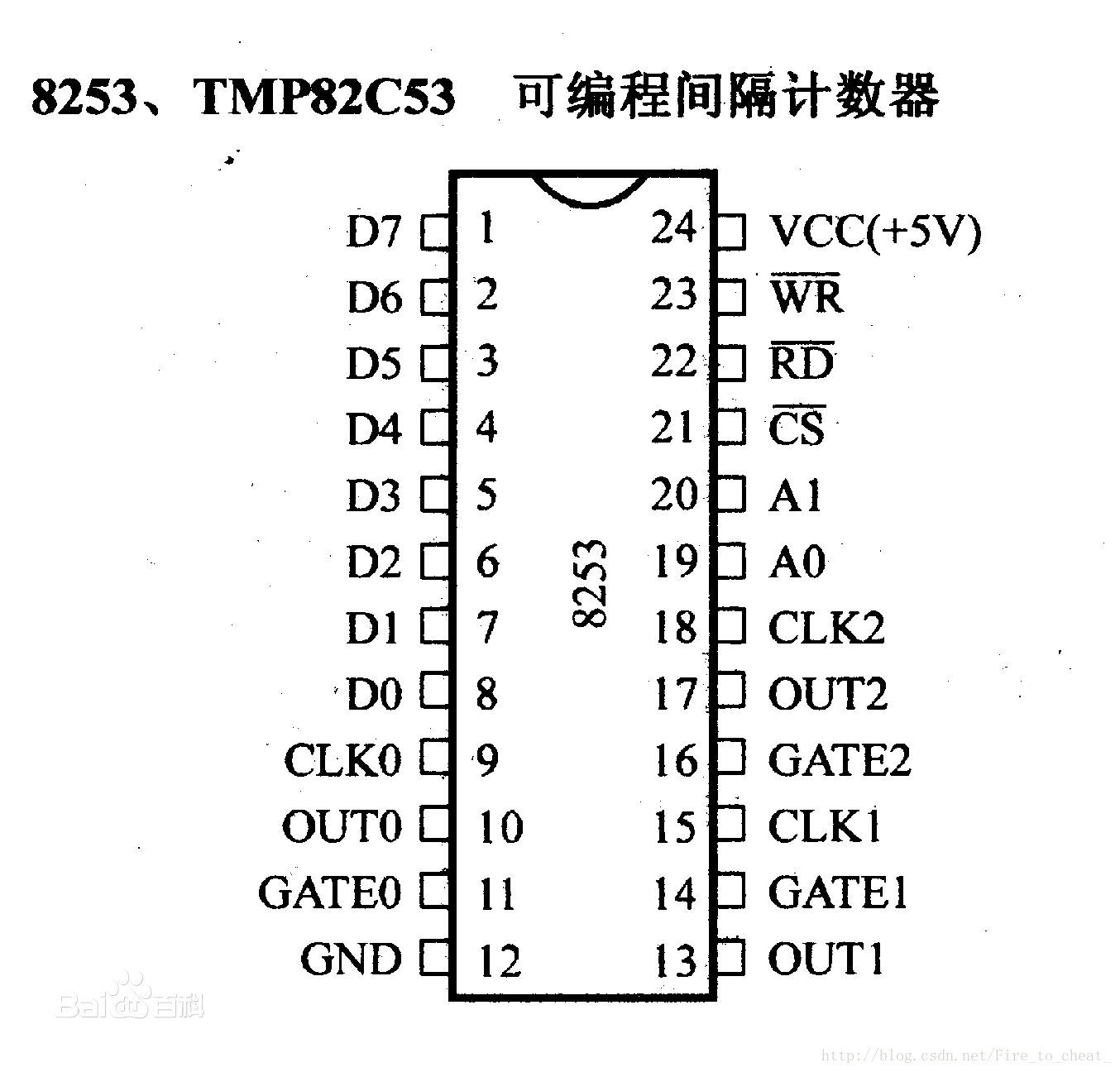

可编程定时/计时8253芯片

8253的初始化编程就是对其工作方式的确定。具体实现就是在8253上电后,由CPU向8253的控制寄存器写入一个控制字,就可以规定8253的工作方式、计数值的长度以及计数所用的数制等,另外根据要求将计数值写入8253的相应通道。- 方式0:计数结束则中断 xx(计数器)xx(读取字节数) 000x

- 方式1:单脉冲发生器 001x

- 方式2:速率波发生器 010x

- 方式3:方波发生器 011x

- 方式4:软件触发方式计数 100x

- 方式5:硬件触发方式计数 101x

课设报告如下:

(等本学期结束后上传工程文档和课设报告!)

2017.12.23

已上传课设工程,下载需要一点点积分

download.csdn.net/download/fire_to_cheat_/10170321

浙公网安备 33010602011771号

浙公网安备 33010602011771号