DDR数据线和地址线

一、CPU和DDR的Fanout

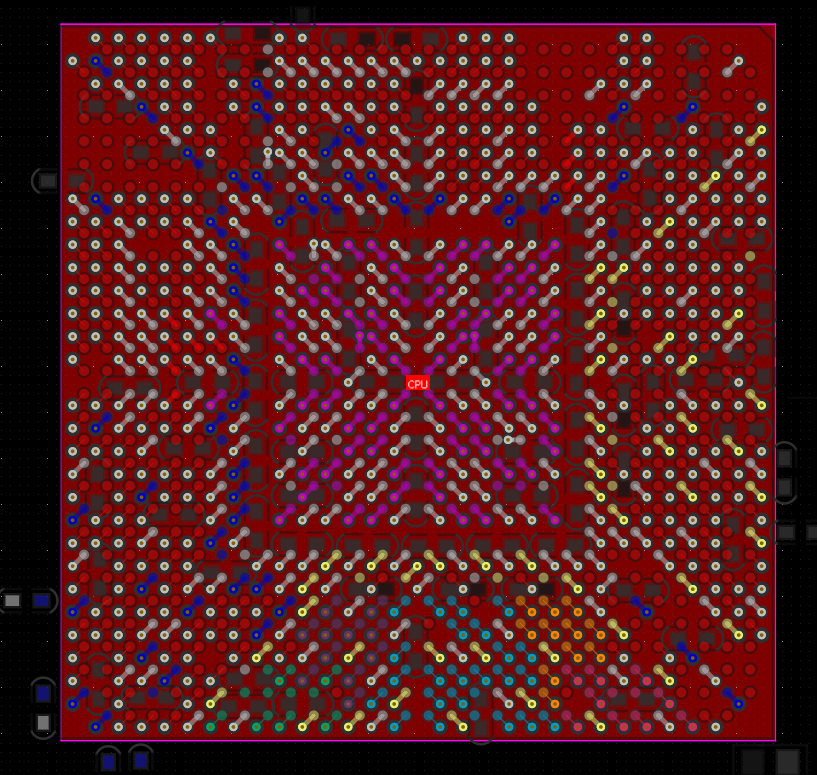

CPU的扇出

选择布线->扇出->器件,待鼠标变为十字光标后,点击CPU,进行扇出。

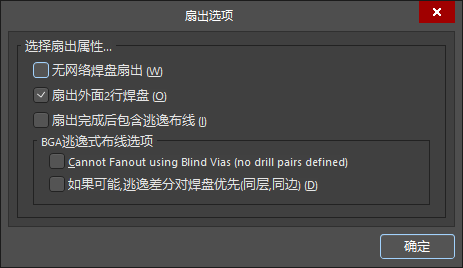

扇出选项图

技术要点:

扇出前,筛选器要选择Compenents开启。否则,扇出时会找不到位号。

扇出后,会根据前一节中对类的设置的对应规则出线,过孔会根据ROOM的规则设置变化。

扇出后的CPU图

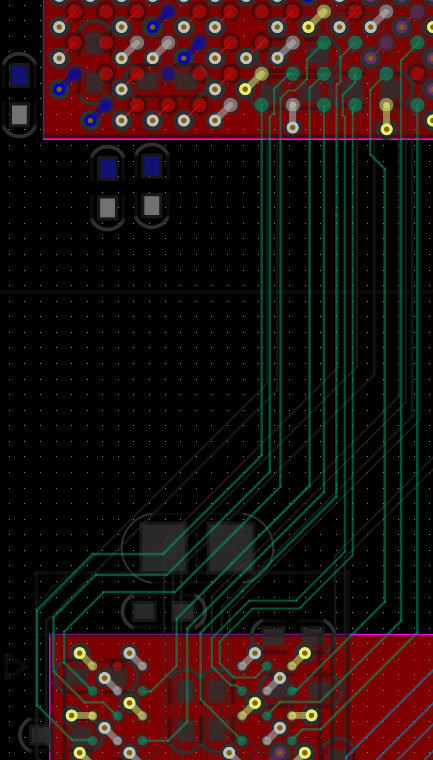

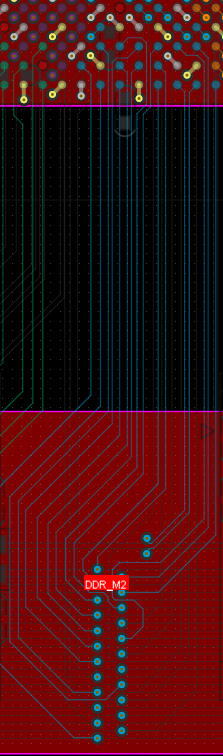

DDR的扇出

DDR为矩形区域,自动扇出往往不理想,要手工扇出。先只需要扇出电源即可。

扇出后的DDR图

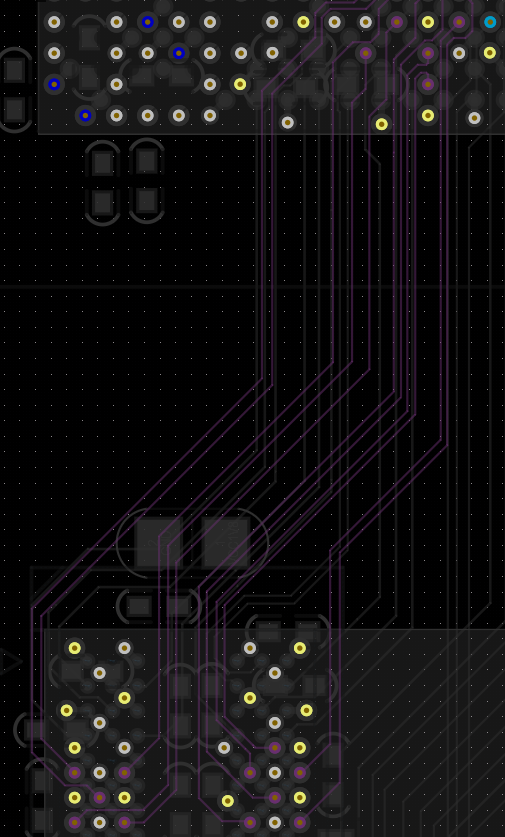

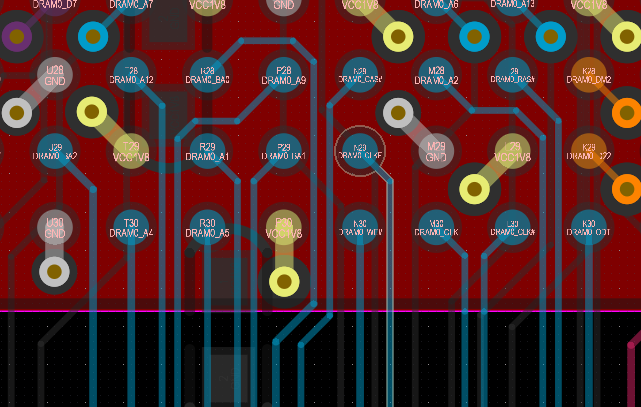

二、DDR数据线互联

技术要点1:

数据线走线需要遵守同组同层走线,根据上一节类的分组来走线。

技术要点2:

数据线走线先走差分,再走单端。

根据上一节的分类,连接数据线。

TOP层和L3层进行走线。

三、地址线和T点的互联

由于T点设计时已经占用一层,即L3层,这里只能使用表层和底层来进行设计。

技术要点1:

CPU到T点,CPU的引脚内外分层走,外面三排走表层,里面三排走底层。

技术要点2:

数据线走线先走差分,再走单端。

浙公网安备 33010602011771号

浙公网安备 33010602011771号