2片DDR布局布线

2片DDR布局布线

一、ROOM区域与规则

放置DDR的ROOM和CPU的ROOM

注意事项 :放置的ROOM不需要很大,覆盖BGA焊盘,适量大小即可。

首先,选中器件,然后使用D M T 快捷键,放置矩形ROOM。最后,选中ROOM,从四边调整ROOM大小,覆盖BGA焊盘。如下图所示:

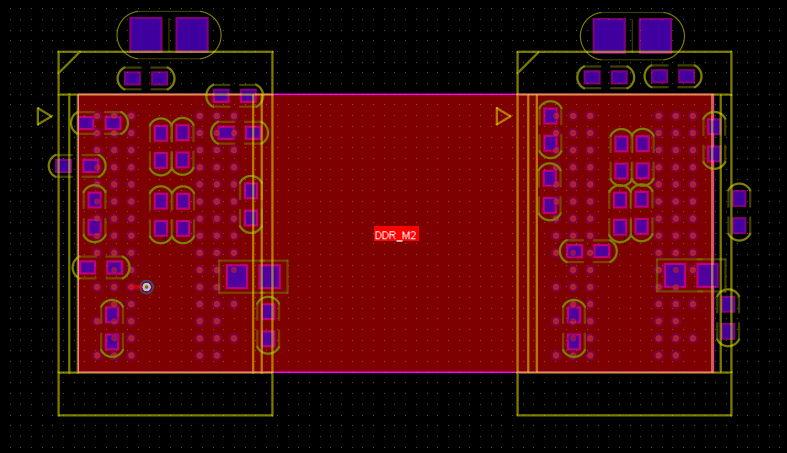

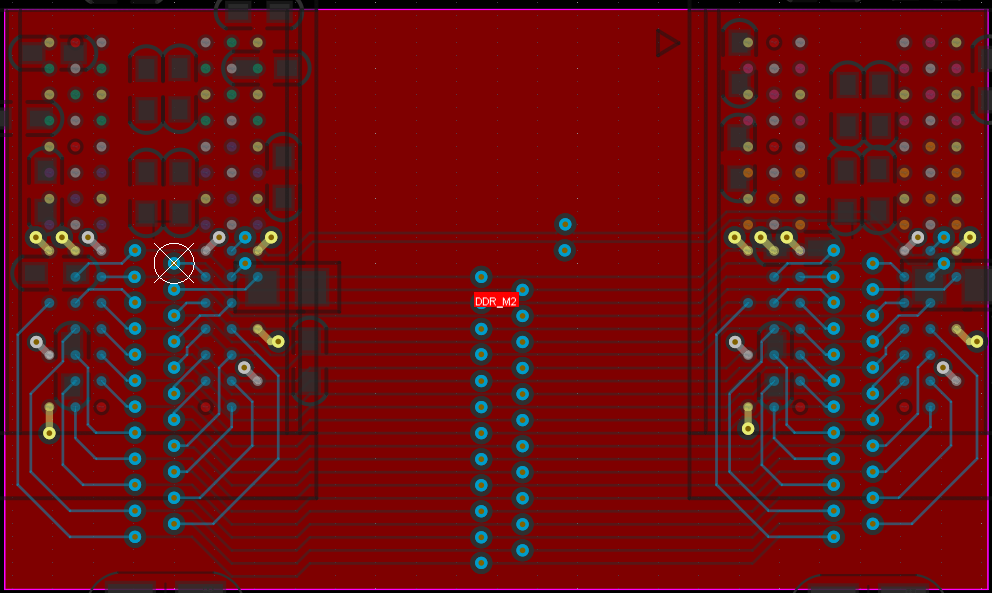

DDR ROOM图

注意事项 :DDR走线和扇出需要在中间进行T点设计,所以它的ROOM要把两片DDR都覆盖上。

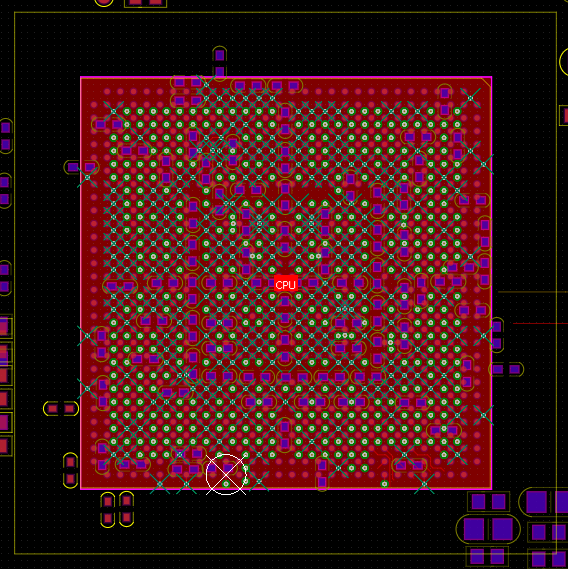

CPU ROOM图

重复上述步骤,给DDR和CPU都放置好ROOM。

修改ROOM参数

- ROOM名称

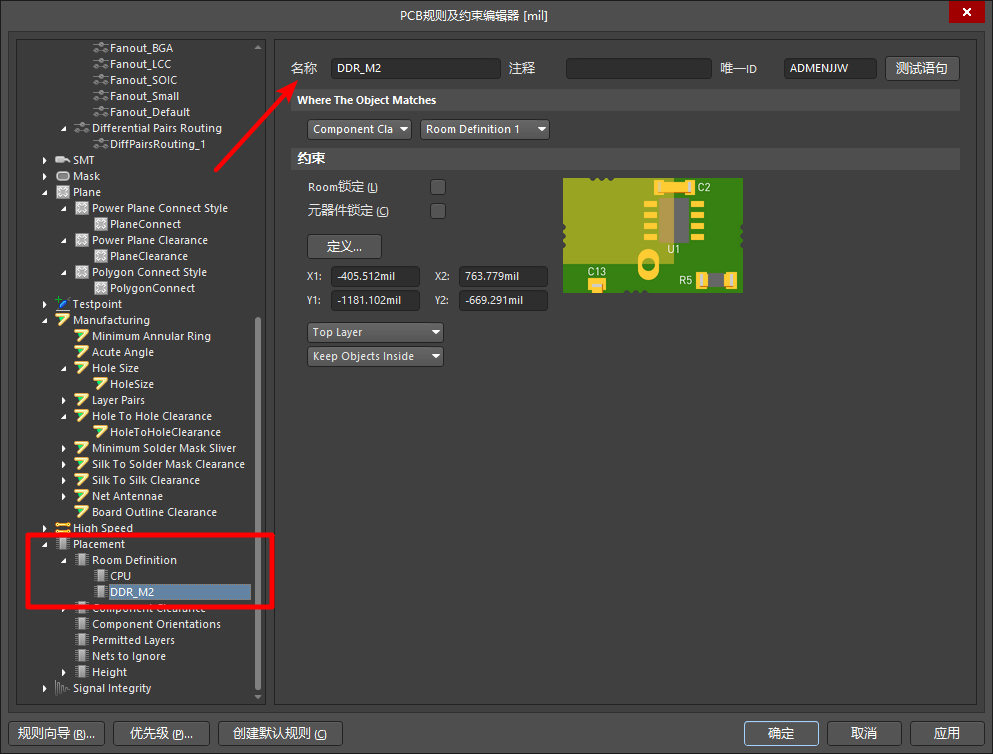

按下快捷键 D R,打开规则管理器,选择Placement->Room Definition,修改ROOM的名称。修改时,对应器件的名称。修改完毕,如下图所示:

- ROOM电气规则(Clearance和Width)——CPU

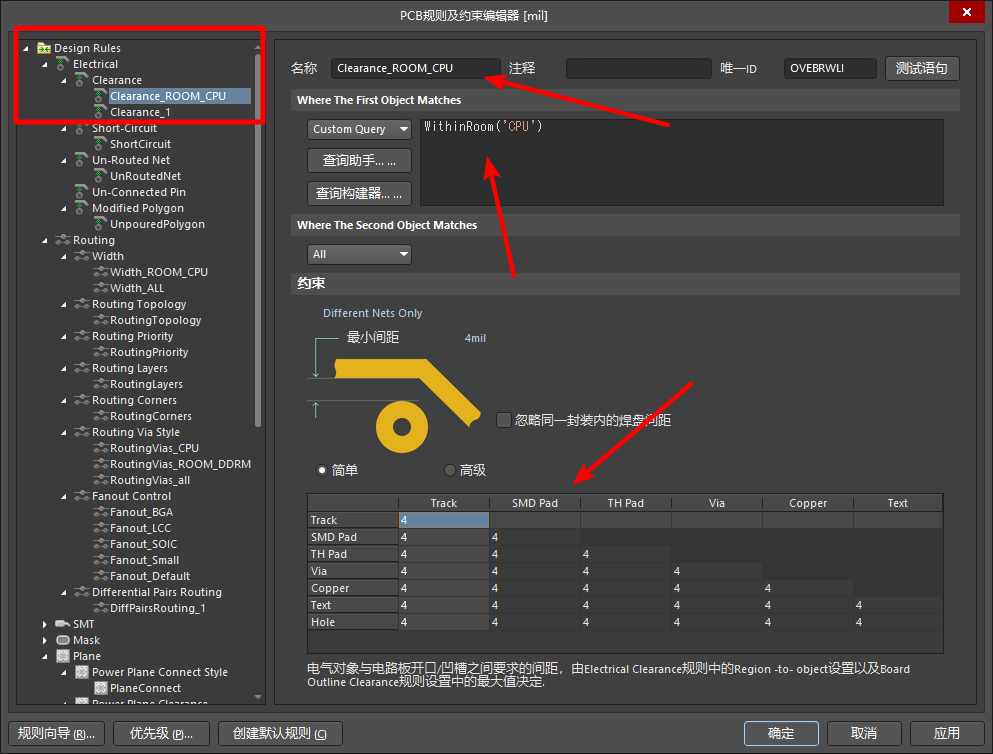

按下快捷键 D R,打开规则管理器,选择Electrical->Clearance,新建规则,修改名称为Clearance_ROOM_CPU,再将应用改规则的区域改为WithinRoom('CPU'),然后修改约束规则,再移动该规则到高一级优先级。如下图所示:

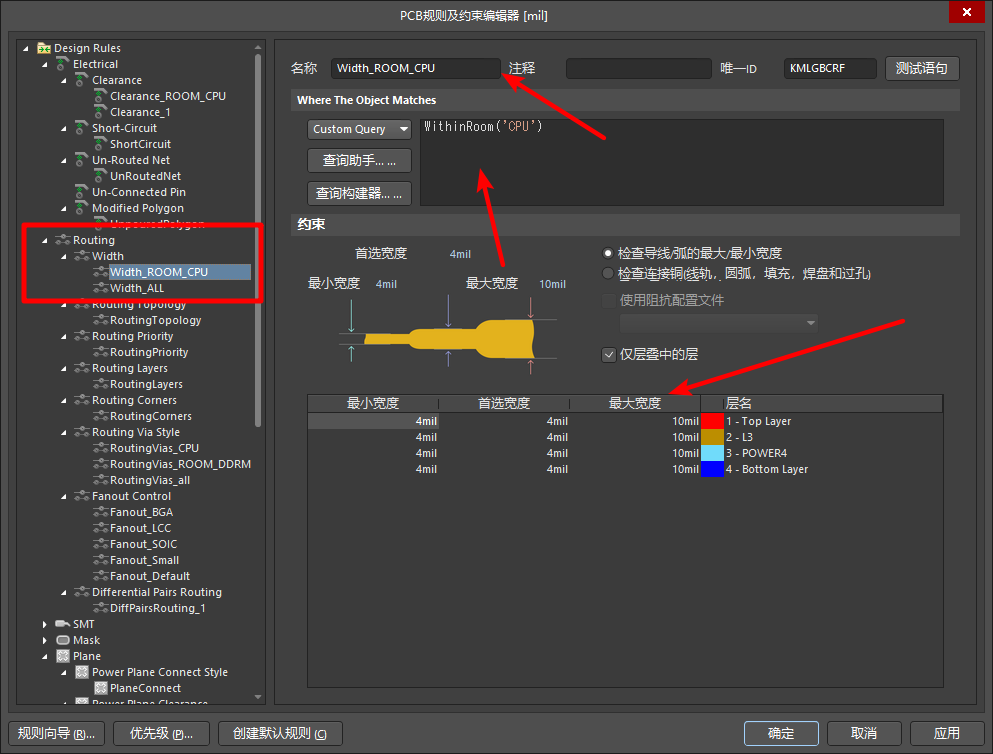

然后选择Routing->Width,新建规则,修改其名称为Width_ROOM_CPU,再将应用改规则的区域改为WithinRoom('CPU'),然后修改约束规则,再移动该规则到高一级优先级。如下图所示:

- ROOM电气规则(Routing Via)——DDR和CPU

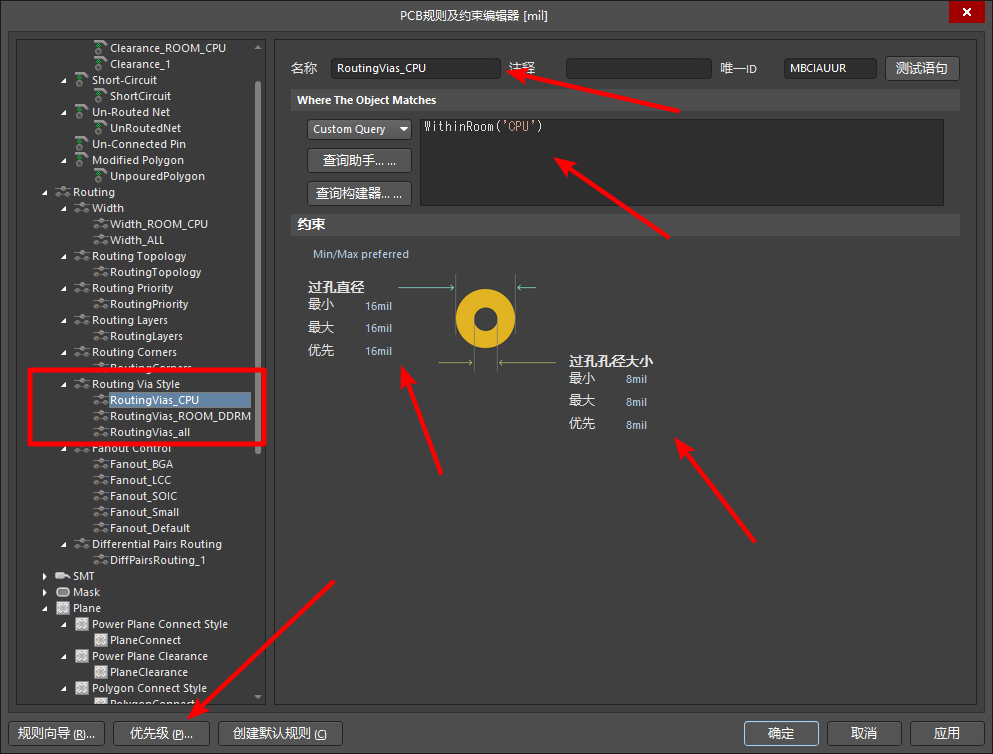

然后选择Routing->Routing Via Style,新建规则,修改其名称为RoutingVias_ROOM_CPU,再将应用改规则的区域改为WithinRoom('CPU') ,然后修改约束规则,再移动该规则到高一级优先级。如下图所示:

技巧:在走线的时候,按下小键盘的2,可以扇出ROOM规则设置的过孔。

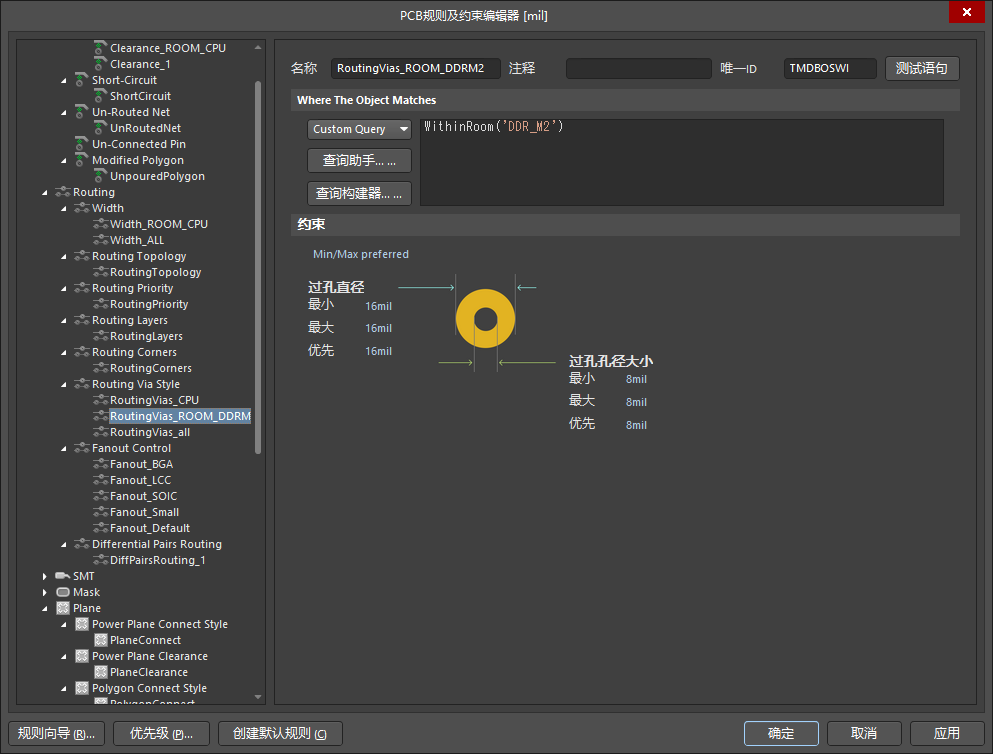

同样的,然后选择Routing->Routing Via Style,新建规则,修改其名称为RoutingVias_ROOM_DDRM2,再将应用改规则的区域改为 WithinRoom('DDR_M2'),然后修改约束规则,再移动该规则到高一级优先级。如下图所示:

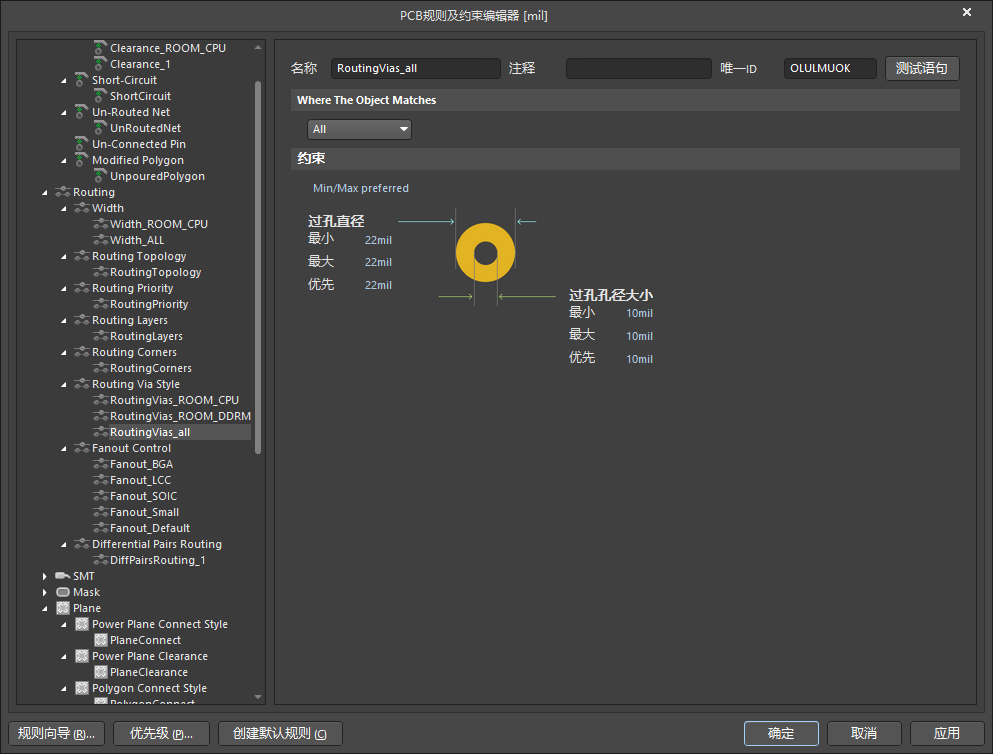

再将普通过孔设置如下的规则,并设置为最低的优先级。

技巧:0.8 mm和1 mm的BGA间距,都可以用8mile/16mile的孔扇出

二、类的设置

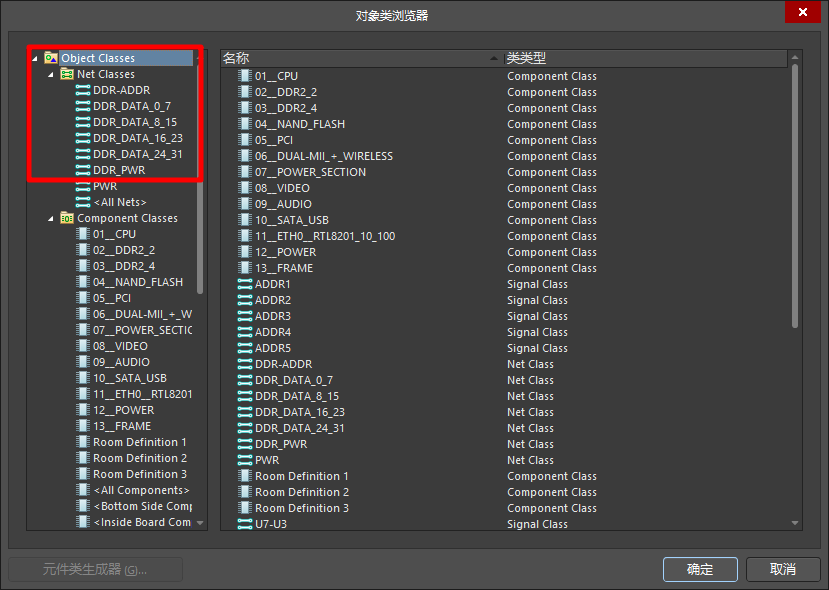

按快捷键,D C,选择Net Classes,新建一个类。DDR需要新建如下几个类。

DDR类:

数据 DDR_DATA_0_7,包括线:D0-D7,DM0和DQS0的差分对。

数据 DDR_DATA_8_15,包括线:D8-D15,DM1和DQS1的差分对。

数据 DDR_DATA_16_23,包括线:D16-D23,DM2和DQS2的差分对。

数据 DDR_DATA_24_31,包括线:D24-D31,DM3和DQS3的差分对。

地址 DDR_ADDR,包括线:A0-A13,BA0,BA1,BA2,CS#,CAS#,Clk#,Clk,RAS#,ODT,WE#,CLKEN

电源 DDR_PWR ,1V8 VREFDDR (电源类可以归到总电源类)

DDR类创建:

三、地址线的T点设计

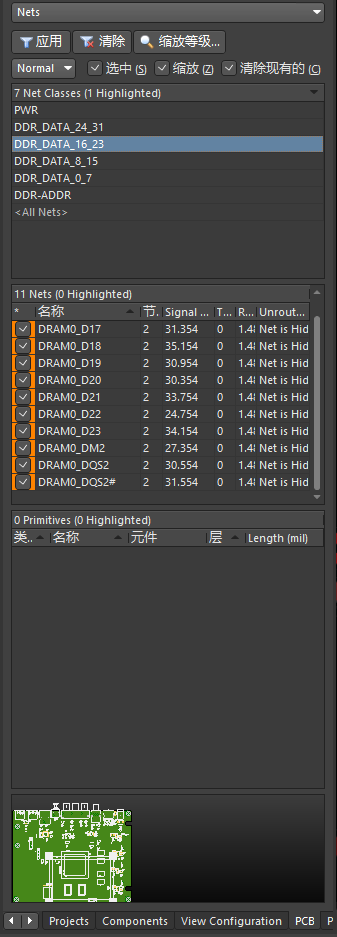

调整CLASS的颜色

选择PCB,筛选NETS,然后选择一CLASS类,全选后选择change net color 修改颜色。

技巧:F5开启/关闭颜色模式。

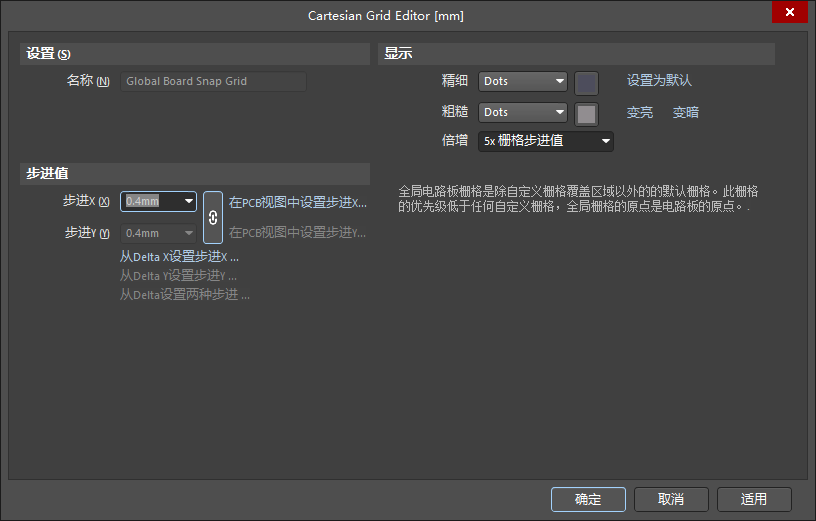

设置步进

使用快捷键 Ctrl+G,设置步进为GBA间距的一半,例如0.8mm间距的BGA,步进调整为0.4mm。然后按格点走线。

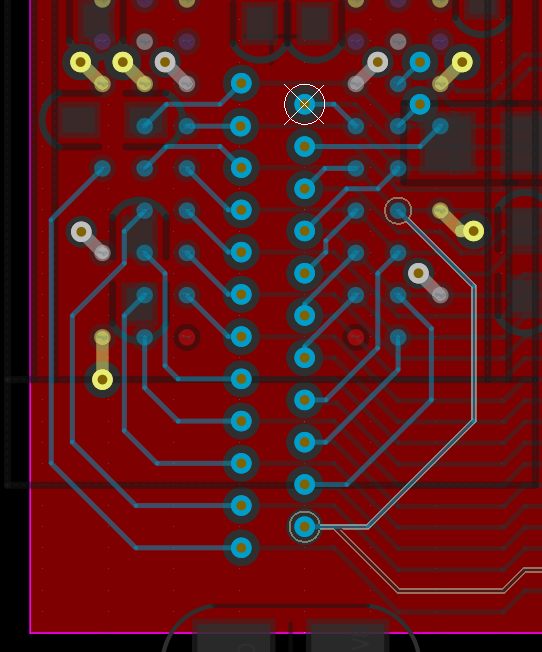

走线小T点

使用走线和快速过孔(走线中按小键盘2)来走出地址线,如下图所示。

将一片DDR的地址线走出来,然后设置原点在该片DDR的焊盘上,并以该点为参考点,复制走线到第二片DDR。如下图所示:

添加差分对

如果原理图中已经标注了差分对,该步骤可以省略。

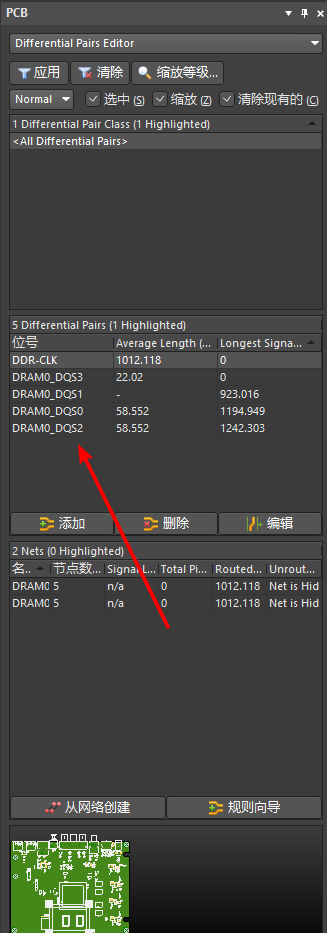

选择PCB,筛选差分对,依次添加下面的五组差分对:

CLK,DQS0-DQS3。

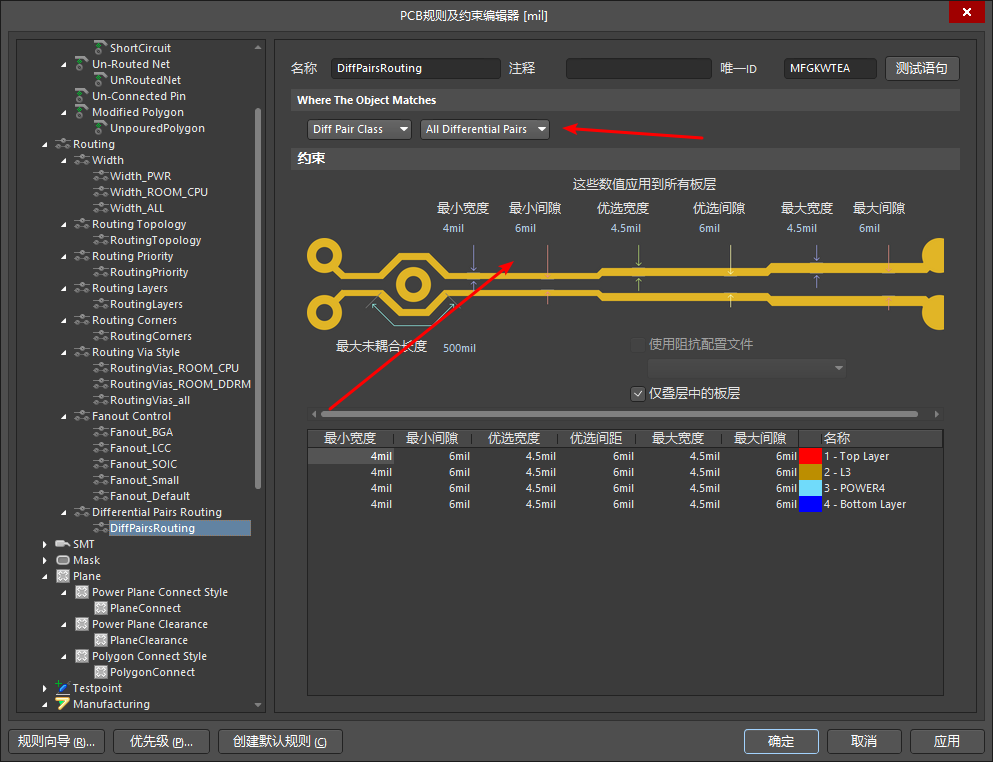

差分对走线规则

选择Routing->Differential Pairs Routing,新建规则,修改其名称为DiffPairsRouting,再将应用改规则的区域改为All Differential Pairs ,然后修改如下的走线规则。如下图所示:

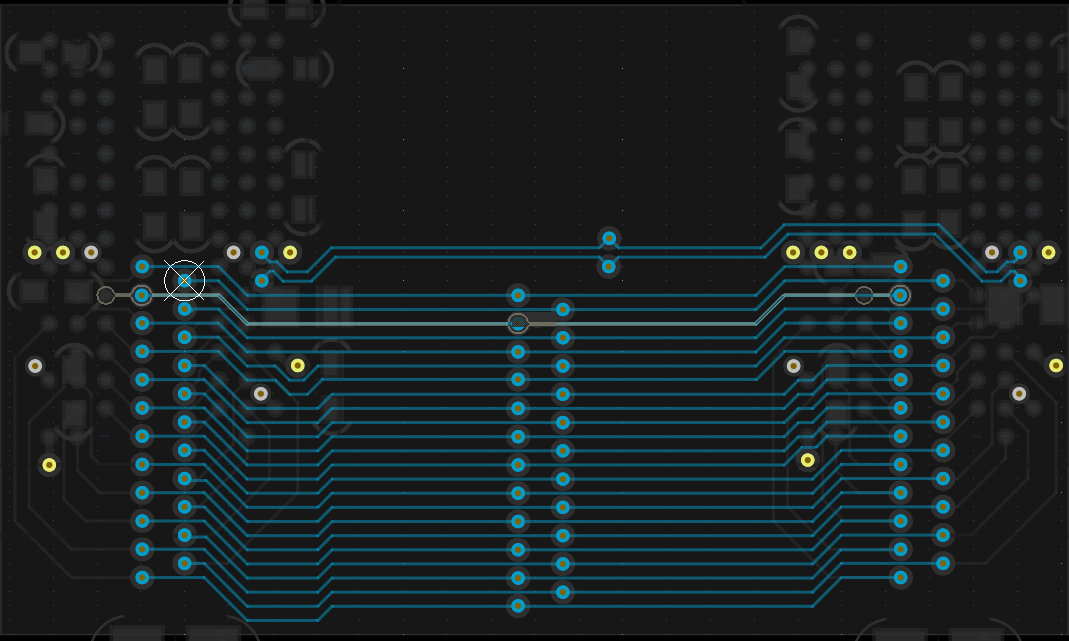

走线大T点

先走差分对,连接两个DDR。然后在线中间放置过孔。如下图所示:

技术要点:大T点的孔要尽量放在连接两片DDR的走线中间。可以使用放置“原点”,来快速测量大T点的孔位。

浙公网安备 33010602011771号

浙公网安备 33010602011771号