信号上升沿检测

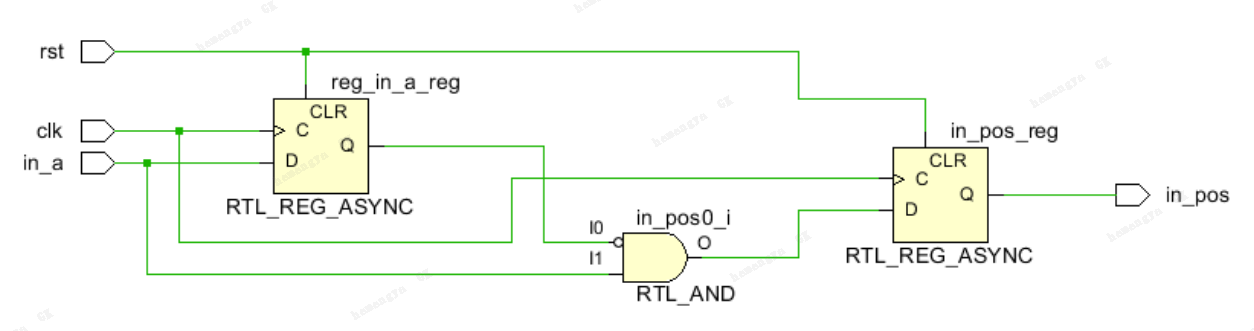

1、单比特信号上升沿检测

module pos_detect( input wire clk , input wire rst , input wire in_a , output reg in_pos ); reg reg_in_a ; always@(posedge clk or posedge rst) begin if(rst) begin reg_in_a <= 1'b0 ; end else begin reg_in_a <= in_a ; end end always@(posedge clk or posedge rst) begin if(rst) beginin_pos <= 1'b0 ; end else begin in_pos <= ~reg_in_a && in_a ; end end endmodule

2、8bit信号上升沿检测

module top_module( input clk, input [7:0] in, output reg [7:0] Pedge ); // answer reg [7:0] R_in; always @(posedge clk) begin R_in <= in; end always @(posedge clk) begin Pedge <= (~R_in) & in; // 注意这里要用按位反而不是逻辑反。 end endmodule

浙公网安备 33010602011771号

浙公网安备 33010602011771号