基于Ubuntu的iverilog编程

1、进入ubuntu的终端

鼠标右击,点击open in Terminal

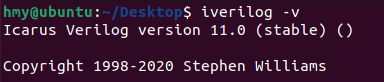

2、安装iverilog和gtkwave

下面的命令用来确认iverilog和gtkwave是否安转成功

3、以一个简单的程序hello iverilog开始

可以参考iverilog官网使用网址:https://iverilog.fandom.com/wiki/User_Guide

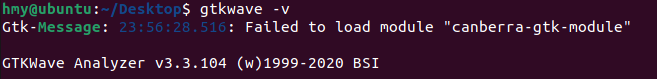

1)鼠标置于桌面空白处,右击点击New Folder,新建一个test的文件夹,然后双击进入该文件夹。鼠标再次右击,点击open in Terminal,

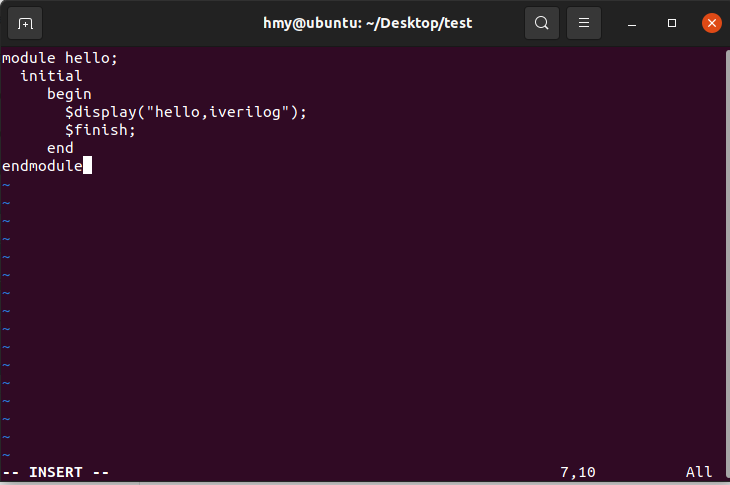

进入终端,输入命令vim hello(这条命令是创建并编辑文本hello)

最好是vim hello.v,建立hello.v文件更规范

2)然后回车,输入a,就可以输入代码啦

3)点击Esc退出编辑,输入:wq,然后回车,回到终端

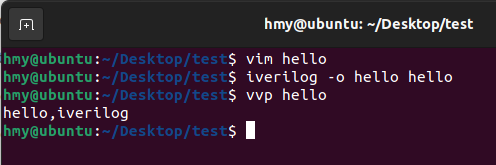

使用以下命令编译该程序:iverilog -o hello hello,“-o”标志告诉编译器将编译结果放在哪里

使用以下命令编译该程序:vvp hello,运行程序

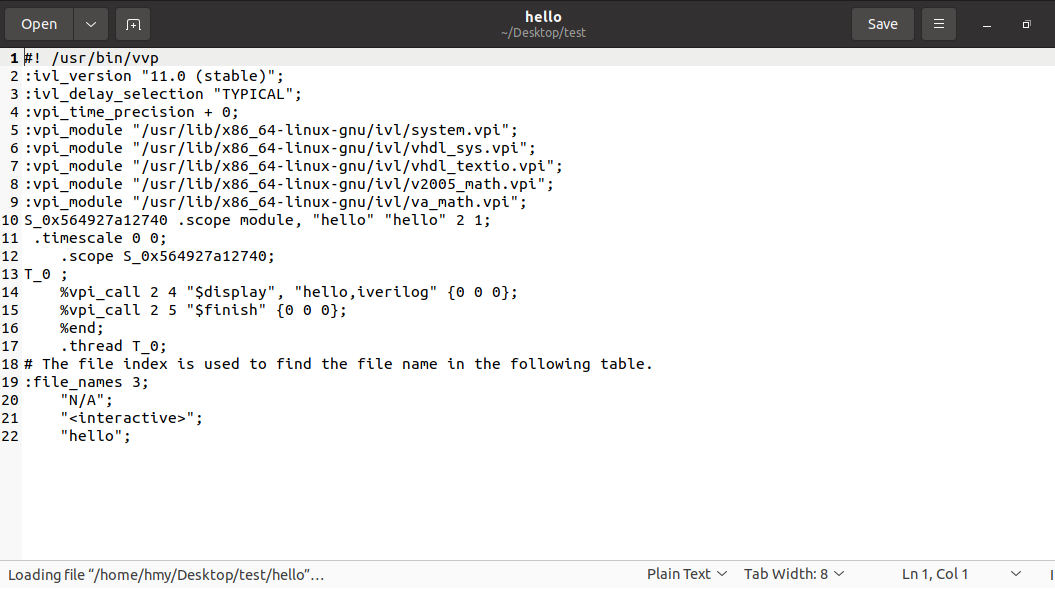

4)运行完毕后的hello文件内容

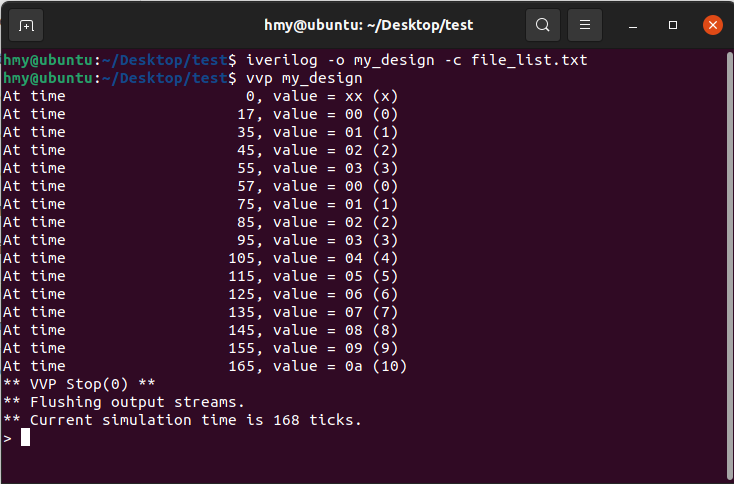

4、跨文件编译

counter.v

module counter(out, clk, reset); parameter WIDTH = 8; output [WIDTH-1 : 0] out; input clk, reset; reg [WIDTH-1 : 0] out; wire clk, reset; always @(posedge clk or posedge reset) if (reset) out <= 0; else out <= out + 1; endmodule // counter

counter_tb.v

module test; /* Make a reset that pulses once. */ reg reset = 0; initial begin # 17 reset = 1; # 11 reset = 0; # 29 reset = 1; # 11 reset = 0; # 100 $stop; end /* Make a regular pulsing clock. */ reg clk = 0; always #5 clk = !clk; wire [7:0] value; counter c1 (value, clk, reset); initial $monitor("At time %t, value = %h (%0d)", $time, value, value); endmodule // test

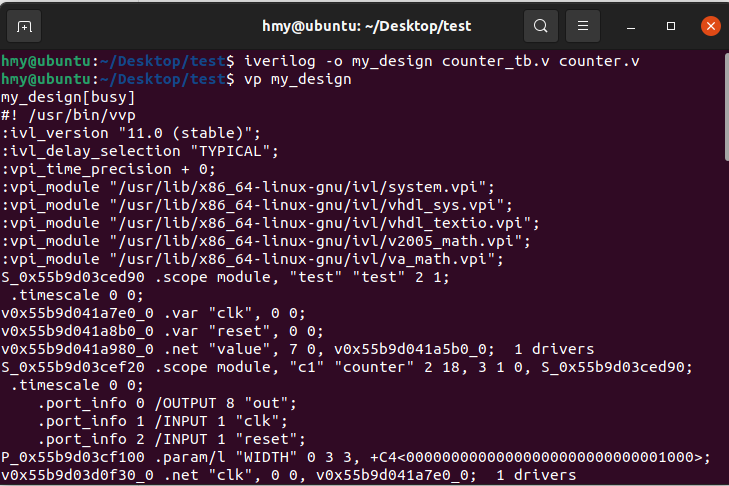

编译执行

方法1:

方法2:

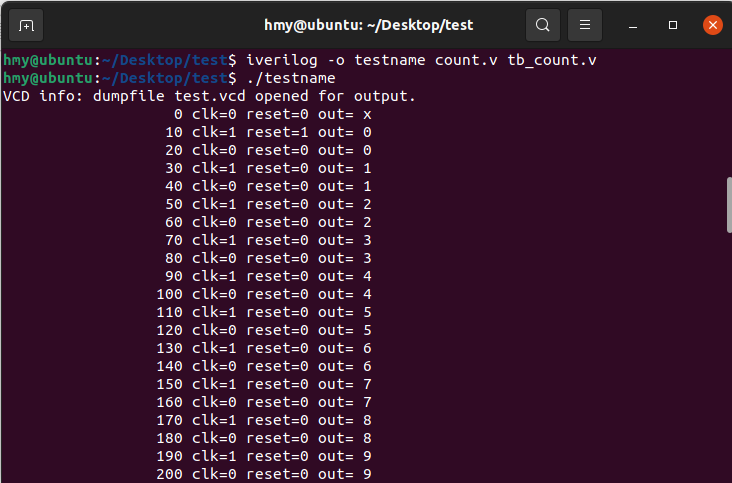

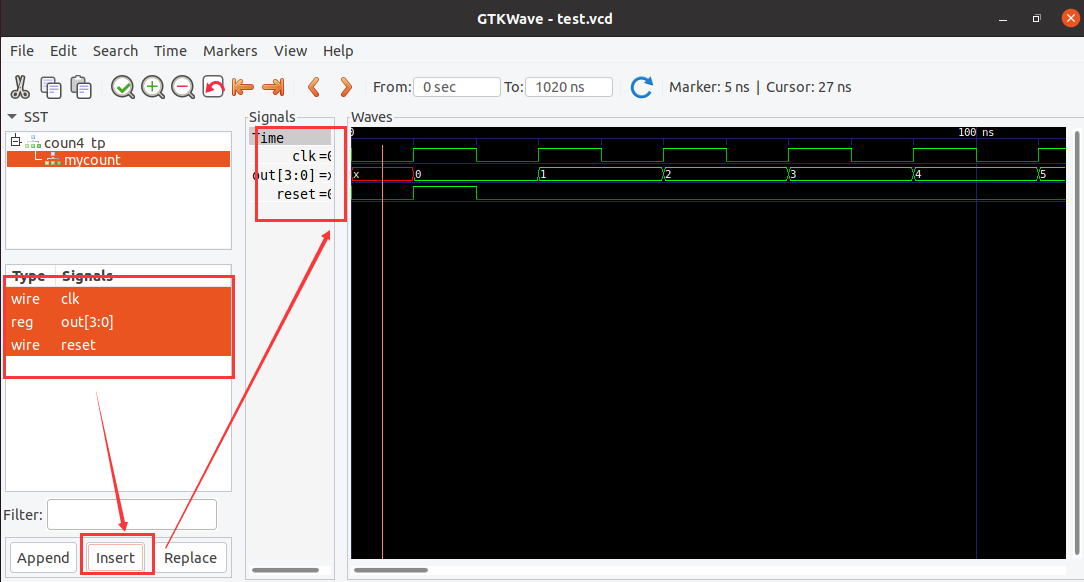

5、仿真波形

参考博文:https://blog.csdn.net/longintchar/article/details/113075606?utm_medium=distribute.wap_relevant.none-task-blog-2~default~baidujs_title~default-0.wap_blog_relevant_pic&spm=1001.2101.3001.4242.1

count.v

module count4(out,reset,clk); output[3:0] out; input reset,clk; reg[3:0] out; always @(posedge clk) begin if (reset) out<=0; else out<=out+1; end endmodule

tb_count.v

`timescale 1ns/1ns module coun4_tp; reg clk, reset; wire[3:0] out; count4 mycount(out,reset,clk); always #10 clk = ~clk; initial begin clk=0; reset=0; #10 reset=1; #10 reset=0; #1000 $stop; end initial $monitor($time,,"clk=%d reset=%d out=%d", clk, reset, out); initial begin $dumpfile("test.vcd"); $dumpvars(0, coun4_tp); end endmodule

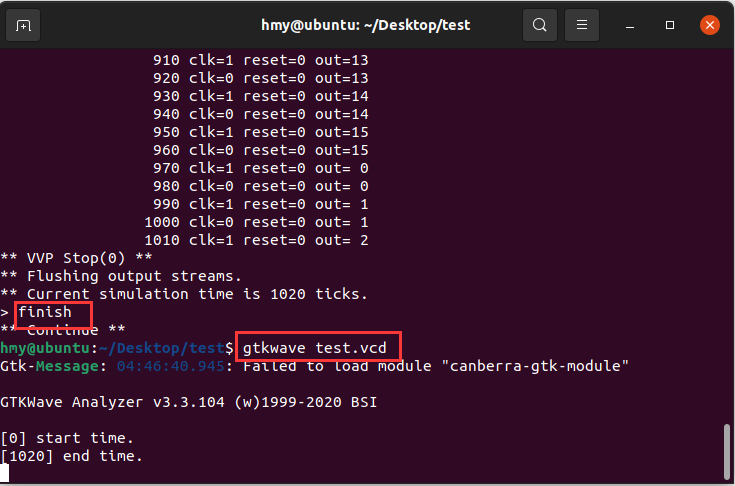

运行命令iverilog -o testname count.v tb_count.v

运行./testname 就会生成 .vcd 波形文件

这时候,又会多出一个 test.vcd 文件

使用 命令gtkwave test.vcd,查看 .vcd 文件

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· TypeScript + Deepseek 打造卜卦网站:技术与玄学的结合

· Manus的开源复刻OpenManus初探

· AI 智能体引爆开源社区「GitHub 热点速览」

· C#/.NET/.NET Core技术前沿周刊 | 第 29 期(2025年3.1-3.9)

· 从HTTP原因短语缺失研究HTTP/2和HTTP/3的设计差异