HDLbits day2

2、Vectors

2.1、Vectors

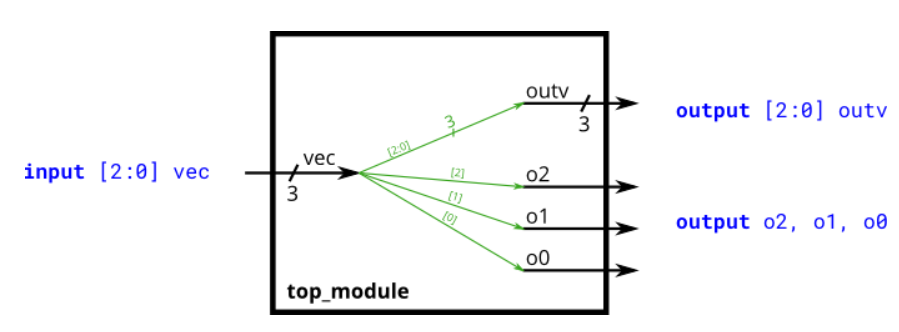

构建一个具有一个 3 位输入的电路,然后输出相同的向量,并将其拆分为三个单独的 1 位输出。将输出连接o0到输入向量的位置 0。

向量用于使用一个名称对相关信号进行分组,以便于操作。例如,wire [7:0] w;声明一个名为w的 8 位向量,它在功能上等同于具有 8 条单独的连线。

module top_module ( input wire [2:0] vec, output wire [2:0] outv, output wire o2, output wire o1, output wire o0 ); // Module body starts after module declaration assign outv=vec; assign o2=vec[2],o1=vec[1],o0=vec[0]; endmodule

2.2、Vectors in more detail

构建一个组合电路,将输入半字(16 位, [15:0] )拆分为低 [7:0] 和高 [15:8] 字节。

`default_nettype none // Disable implicit nets. Reduces some types of bugs. module top_module( input wire [15:0] in, output wire [7:0] out_hi, output wire [7:0] out_lo ); assign out_hi=in[15:8],out_lo=in[7:0]; endmodule

2.3、Vector part select

一个 32 位向量可以被视为包含 4 个字节(位 [31:24]、[23:16] 等)。构建一个将反转4 字节字 的字节顺序的电路。

AaaaaaaaBbbbbbbbCcccccccDdddddddd => DddddddCcccccccBbbbbbbbAaaaaaaaa

module top_module( input [31:0] in, output [31:0] out );// // assign out[31:24] = ...; assign out[7:0]=in[31:24]; assign out[15:8]=in[23:16]; assign out[23:16]=in[15:8]; assign out[31:24]=in[7:0]; endmodule

2.4、Bitwise operators

构建一个具有两个 3 位输入的电路,用于计算两个向量的按位或、两个向量的逻辑或以及两个向量的逆 (NOT)。

将 out_not的 [5:3]存放b的反,将 out_not下半部分存放a的反。

module top_module( input [2:0] a, input [2:0] b, output [2:0] out_or_bitwise, output out_or_logical, output [5:0] out_not ); assign out_or_bitwise=a|b; assign out_or_logical=a||b; assign out_not[5:3]=~b; assign out_not[2:0]=~a; endmodule

2.5、Four-input gates

构建一个具有四个输入的组合电路in[3:0]。

有3个输出:

- out_and:4 输入与门的输出。

- out_or:4 输入或门的输出。

- out_xor:4 输入异或门的输出。

module top_module( input [3:0] in, output out_and, output out_or, output out_xor ); assign out_and=∈ assign out_or=|in; assign out_xor=^in; endmodule

2.6、Vector concatenation operator

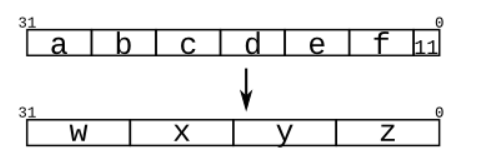

给定几个输入向量,将它们连接在一起,然后将它们分成几个输出向量。

有六个 5 位输入向量:a、b、c、d、e 和 f,总共 30 位输入。

有四个 8 位输出向量:w、x、y 和 z,用于 32 位输出。

输出应该是输入向量的串联,后跟两个1位:

module top_module ( input [4:0] a, b, c, d, e, f, output [7:0] w, x, y, z );// // assign { ... } = { ... }; assign {w,x,y,z}={a,b,c,d,e,f,1'b1,1'b1}; endmodule

2.7、Vector reversal 1

给定一个 8 位输入向量 [7:0],反转其位顺序

介绍generate语法

https://blog.csdn.net/woshiyuzhoushizhe/article/details/90453189

module top_module( input [7:0] in, output [7:0] out ); generate genvar i; for(i=0;i<=7;i=i+1) begin:name assign out[i]=in[7-i]; end endgenerate endmodule

2.8、Replication operator

构建一个将 8 位数字符号扩展为 32 位的电路。这需要连接 24 个符号位副本(即复制位 [7] 24 次),然后是 8 位数字本身。

看到复制运算符的一个常见地方是,将较小的数字符号扩展为较大的数字,同时保留其符号值。这是通过将较小数字的符号位(最高有效位)复制到左侧来完成的。例如,将4'b 0 101 (5) 符号扩展至 8 位会产生8'b 0000 0101 (5),而将4'b 1 101 (-3) 符号扩展至 8 位会产生8'b 1111 1101 (-3)。

module top_module ( input [7:0] in, output [31:0] out );// // assign out = { replicate-sign-bit , the-input }; assign out={{24{in[7]}},in}; endmodule

2.9、More replication

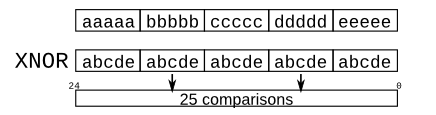

给定五个 1 位信号(a、b、c、d 和 e),计算 25 位输出向量中的所有 25 个成对的一位比较。如果被比较的两位相等,则输出应为 1。

out[24] = ~a ^ a; // a == a, so out[24] is always 1.

out[23] = ~a ^ b;

out[22] = ~a ^ c;

...

out[ 1] = ~e ^ d;

out[ 0] = ~e ^ e;

module top_module ( input a, b, c, d, e, output [24:0] out );// // The output is XNOR of two vectors created by // concatenating and replicating the five inputs. // assign out = ~{ ... } ^ { ... }; assign out=~{{5{a}},{5{b}},{5{c}},{5{d}},{5{e}}}^{5{a,b,c,d,e}}; endmodule