【计组实验】实验f2 一位全加器

一、实验目标

测试全加器f_adder的功能,并做出仿真波形。

二、实验原理

全加器f_adder由两个半加器h_adder和一个或门or2a组成,先完成半加器和或门的VHDL代码,然后在全加器的VHDL代码中调用半加器和或门就可以实现全加器的功能。

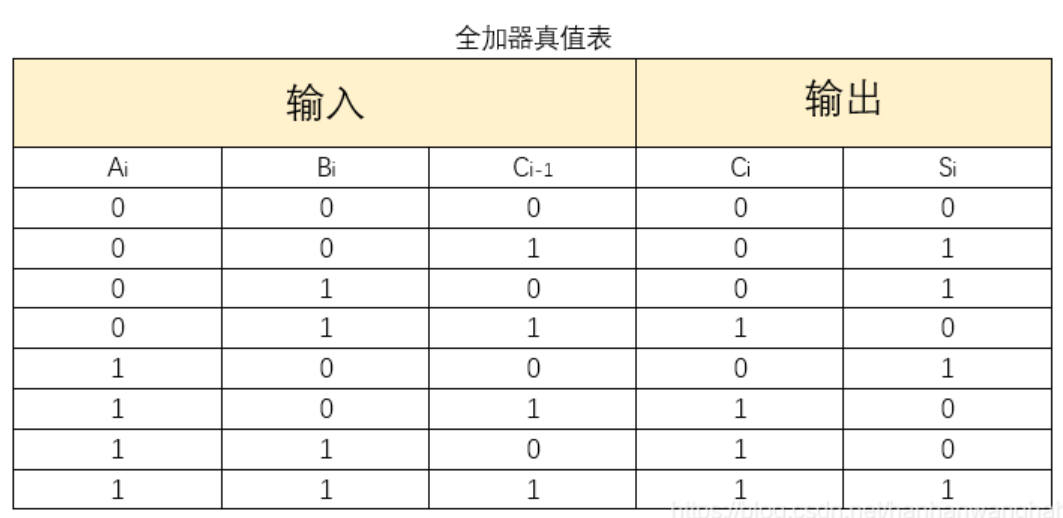

真值表

三、实验代码

或门 or2a

LIBRARY IEEE ; --或门逻辑描述

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY or2a IS

PORT (a, b : IN STD_LOGIC; c : OUT STD_LOGIC );

END ENTITY or2a ;

ARCHITECTURE one OF or2a IS

BEGIN

c <= a OR b ;

END ARCHITECTURE one ;

半加器 h_adder

LIBRARY IEEE; --半加器描述(1):布尔方程描述方法

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY h_adder IS

PORT ( a, b : IN STD_LOGIC;

co, so : OUT STD_LOGIC);

END ENTITY h_adder;

ARCHITECTURE fh1 OF h_adder IS

BEGIN

so <= NOT(a XOR (NOT b)) ; co <= a AND b ;

END ARCHITECTURE fh1;

全加器 f_adder

LIBRARY IEEE; --1位二进制全加器顶层设计描述

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY f_adder IS

PORT (ain, bin, cin : IN STD_LOGIC;

cout, sum : OUT STD_LOGIC);

END ENTITY f_adder;

ARCHITECTURE fd1 OF f_adder IS

COMPONENT h_adder --调用半加器声明语句

PORT ( a, b : IN STD_LOGIC;

co, so : OUT STD_LOGIC);

END COMPONENT;

COMPONENT or2a

PORT (a, b : IN STD_LOGIC;

c : OUT STD_LOGIC);

END COMPONENT;

SIGNAL d, e, f : STD_LOGIC; --定义3个信号作为内部的连接线

BEGIN

u1 : h_adder PORT MAP(a=>ain, b=>bin, co=>d, so=>e); --例化语句

u2 : h_adder PORT MAP(a=>e, b=>cin, co=>f, so=>sum);

u3 : or2a PORT MAP(a=>d, b=>f, c=>cout);

END ARCHITECTURE fd1;

四、实验过程

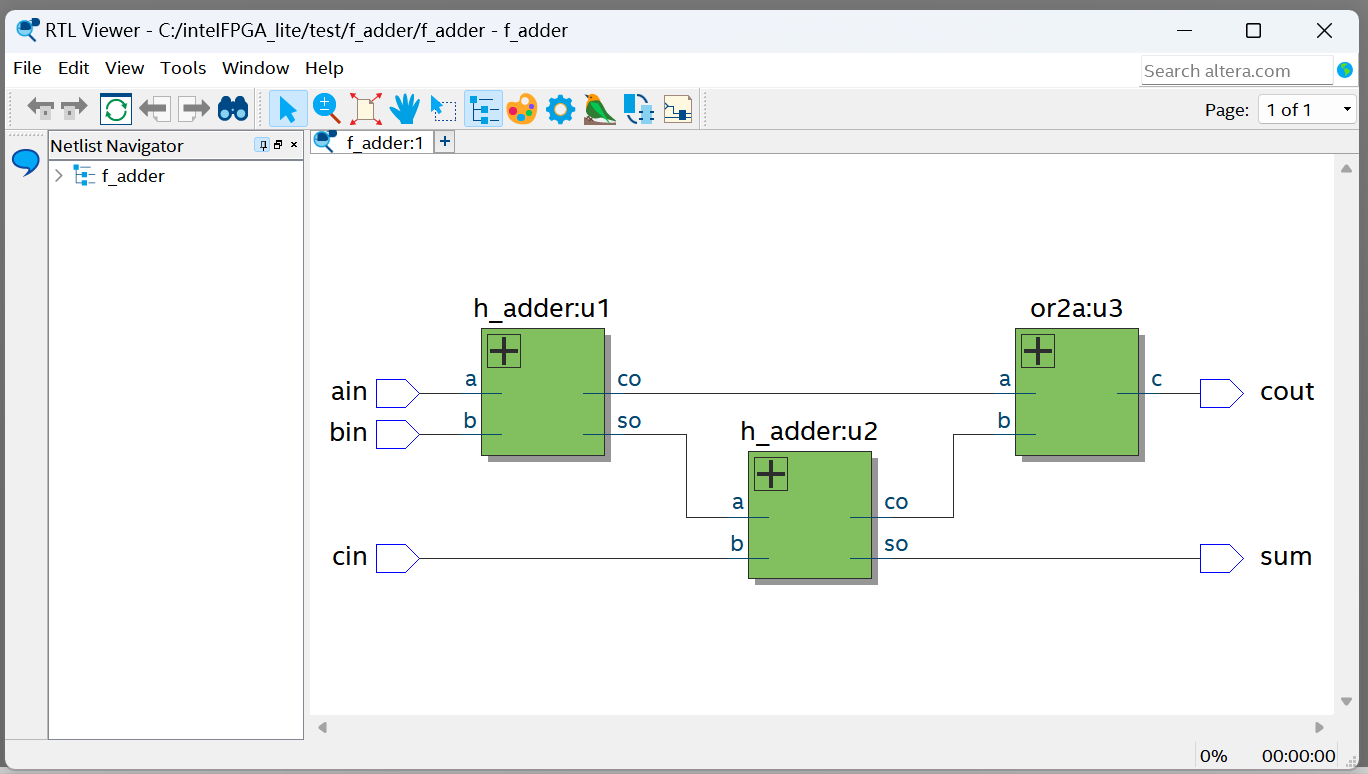

元件图

可以看到,全加器f_adder就是由两个半加器h_adder和一个或门or2a组成的,符合上面全加器f_adder VHDL代码。

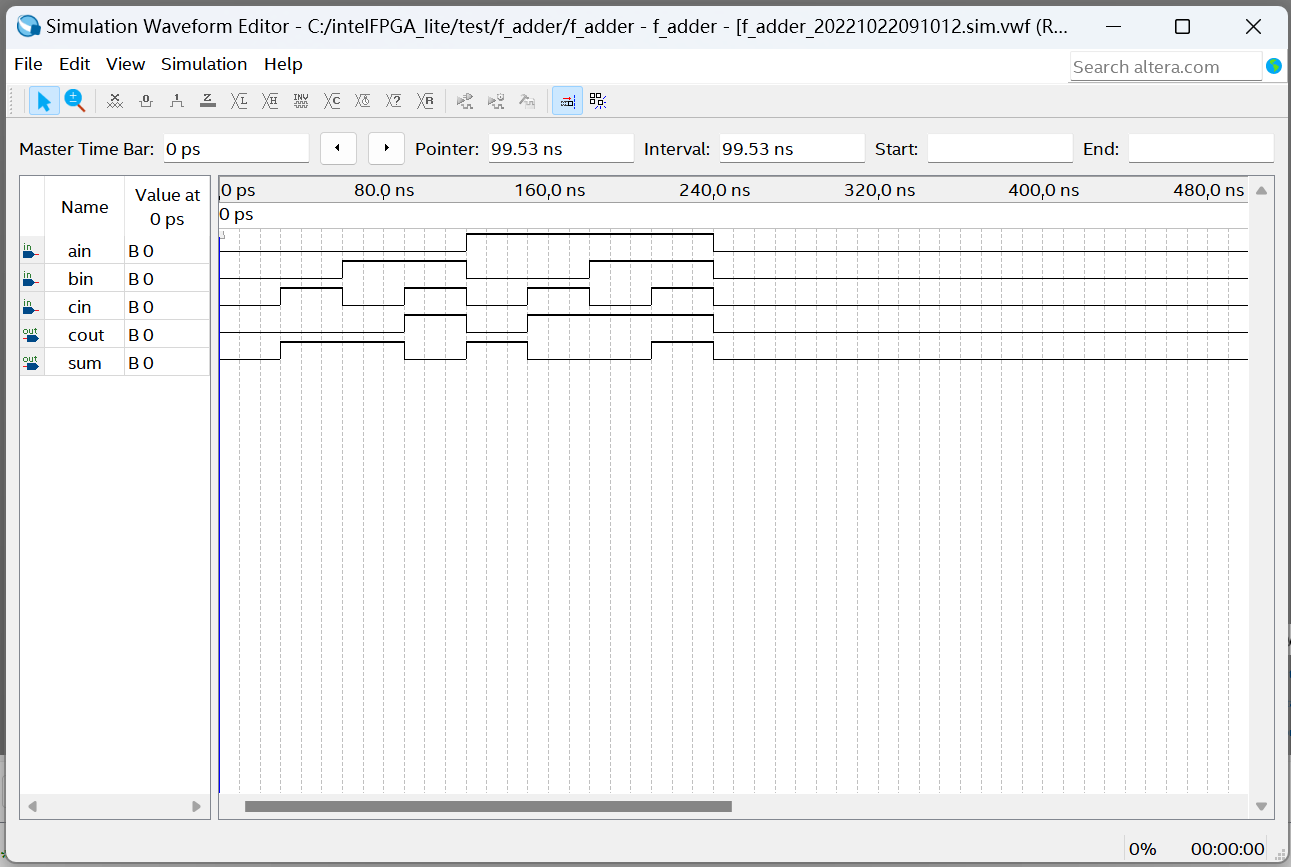

测试波形

测试:共有三个输入a,b,c,我测试了三个输入的所有8种不同组合,通过判断cout,sum两个输出的波形可得符合全加器的真值表。

测试结果:测试波形符合一位全加器的真值表;当只有一个输入为高电平时,进位输出cout为低电平,结果输出sum为高电平;当任意两个输入为高电平时,进位输出cout为高电平,结果输出sum为低电平;当所有输入都为高电平时,进位输出cout和结果输出sum都为高电平。

五、实验总结

本次实验比上一次实验难度稍微大些,但有了上一次实验作为基础,在做本次实验是就不再是那种找不着头脑的状态。本次实验是实现和验证一位全加器,在实验中我学会了可以在用VHDL实现一种元器件时调用调用其他元器件,比如全加器就是通过调用了半加器和或门实现的。本次实验后,我加深了对VHDL语言的理解,同时也能更加熟练地使用Quartus了。

浙公网安备 33010602011771号

浙公网安备 33010602011771号