电赛错误集锦

1、7月24日上午

今天调试示波器,通过外部触发存储波形,原理其实很简单,就是把vga有效区域内的数据存储到ram当中,然后当按键触发时再把数据掉出来,

但是奇怪的是,vga存储的波形只有最后六分之一的波形,搞了一上午,最后才发现在ram生成IP的过成中,手残,读写地址线是5位宽,忘记改了,、

所以在vga上只显示了部分重复的波形。

2、7月24日晚上

晚上帮队友调试AD硬件板,AD输出引脚在示波器上明明有输出,但是在sigtab上却看不见,调了好长时间才发现是ad的引脚输出定义位output。

这样的问题真的没有价值,有非常的浪费时间。

3、7月26日下午

刚开始学习Verilog的时候,语法非常死板,都有带着位宽的习惯,渐渐的,比较懒了,能省的都省了,但是这样不太好,不带位宽,会出现警告,

虽然说不影响程序运行,但是警告如果太多的话,影响你查找别的错误,于是从今往后,我要把位宽给带上。

4、7月26日下午

之前出现这个警告Warning (12125): Using design file shift_sig.v, which is not specified as a design file for the current project, but contains definitions for 1 design units and 1 entities in project,没有注意,刚刚google了一下,发现是因为文件没有添加到工程当中,虽然说不影响程序运行,但是有警告,看着也不顺眼。

5、7月27日中午

今天上午调试逻辑分析仪,将数据存到RAM当中,读的时候发现数据延迟了两个数据,上网搜了一下,发现地址线经过两个D触发器,才能将数据输出,SOUGA

6、7月27日下午

Error (10228): Verilog HDL error at ram_256x64.v(39): module "ram_256x64" cannot be declared more than once,在quartus中,添加文件,如果都添加进去的话,

会出现错误提示,意思就是模块的重复例化,其实在生成ram的时候,qip文件已经包含该顶层文件,不需要人工进行例化。

7、7月28日早上

Error (10257): Verilog HDL error at key_control.v(78): unsized constants are not allowed in concaten , 错误应该是在拼接语句当中,没有加上位宽的大小 for example 1'b1

8、7月29日中午

always @(posedge clk or negedge rst_n) begin if(!rst_n) M_sync_clk <= 1'd0; else if(cnt_sync_clk >= num_sig - 1'b1 || sig_in_pos) M_sync_clk <= 1'd1; else if(cnt_sync_clk == half_num - 1) M_sync_clk <= 1'd0; else M_sync_clk <= M_sync_clk; end

今天再调试M序列同步的程序,最终结果就是没有输出,最终发现

if(cnt_sync_clk == half_num - 1) 这一句话本来是等于一半时置0,之前是这样写的 if(cnt_sync_clk == num_sig >> 1 - 1),没有注意优先级,所以出不来。

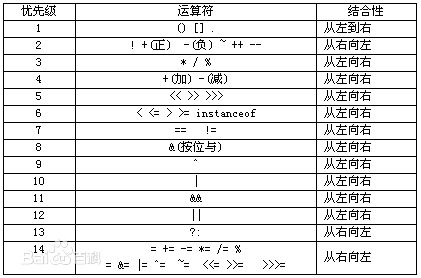

附一张优先级图品

9、7月31日中午

昨天晚上在调试FFTIP核,因为fft输入的数据核source_exp缩放因子都是有符号的数,记录一下如何把二进制转换成十进制,例如110100.第一点,最高位是1,所以确定它是一个负数,

第二部减1得110011,第三部取反001100最后数据是12,因为是负数所以是-12

10、8月2日上午

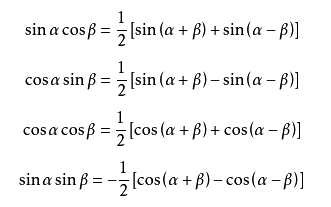

2013年频率特性测试仪用到了乘法器,回忆一下积化合差公式

11、8月6日中午

今天上午打开学长往年写的程序,结果啥都没有,发现程序所在的位置不能有中文目录。

12、8月8日晚上

fifo初始化状态就是满的,所以必须有读时钟才可以。

13、8月8日晚上

写FIFO和读fifo控制速率尽量用读写使能端控制