fpga驱动VGA显示

简单的介绍一下VGA的驱动时序

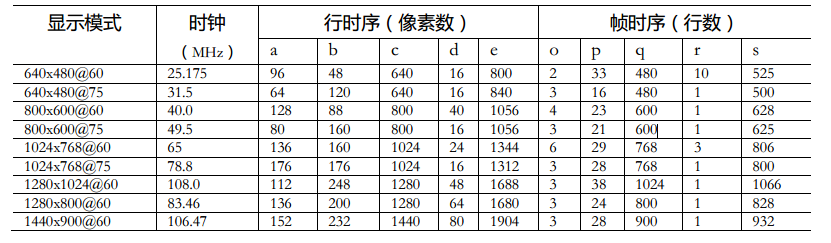

1、不同的时钟有不同的时序要求,通过上表选择不同的参数

HSYNC 是水平同步信号,VSYNC是行同步信号

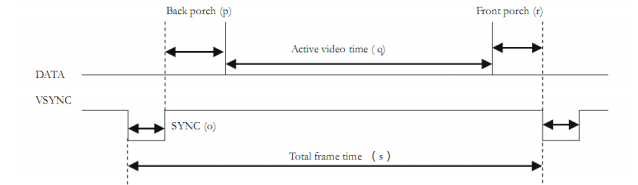

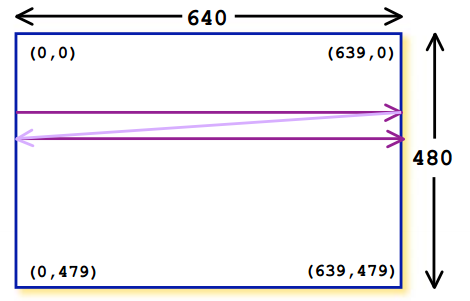

可以通过上图大致了解水平同步(帧)信号一行扫描结束之后,行同步信号才进行扫一次,从左上角的一个像素

一直扫到右下角的最后一个像素,不断刷新。

行同步信号和帧同步信号都有各自的四个区域分别是(a,b,c,d)和(o,p,q,r)各四个区域,分别代表同步

段,后廓段,激活段和前廓段。

其中激活都拿是有效显示区域,显示屏显示的区域就是激活段。

同步段可以通过第二三幅图看出,行同步信号和帧同步信号,在这两个阶段是需要拉低的。

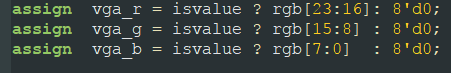

每个像素是rgb24格式的,其中红绿蓝三原色各代表其中八个位宽,那么每个颜色有256中可能性,

24位的话就有2^24中颜色。

贴上部分代码

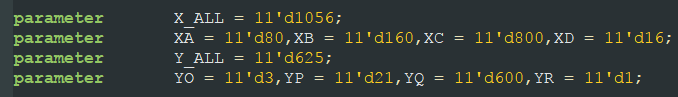

先声明部分参数,根据第一张图提取四个区域

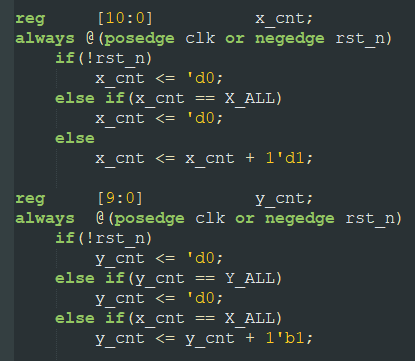

通过x,y计数来代表水平同步信号和行同步信号

在激活段显示相应的颜色

在同步段拉低,其余置高