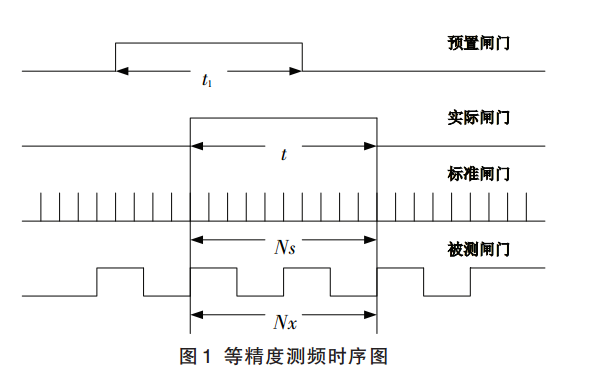

等精度测频

module detect( clk, rst_n, sig_in, pinlv ); input clk; input rst_n; input sig_in; output [31:0] pinlv; reg fgate; reg start_cnt; reg [31:0] fx_cnt_temp; reg [31:0] fb_cnt_temp; reg [31:0] fx_cnt; reg [31:0] fb_cnt; always @(posedge clk or negedge rst_n) if(!rst_n) fgate <= 1'd0; else if(fb_cnt_temp >= 50_000_000) fgate <= 1'd0; else fgate <= 1'd1; always @(posedge clk) if(start_cnt) fb_cnt_temp <= fb_cnt_temp + 1'b1; else fb_cnt_temp <= 32'd0; reg r_start; always @(posedge clk) r_start <= start_cnt; always @(posedge sig_in) if(start_cnt) fx_cnt_temp <= fx_cnt_temp + 1'b1; else if(!(!start_cnt && r_start)) fx_cnt_temp <= 32'd0; always @(posedge sig_in) if(fgate) start_cnt <= 1'd1; else start_cnt <= 1'd0; always @(negedge start_cnt)begin fb_cnt <= fb_cnt_temp; fx_cnt <= fx_cnt_temp; end assign pinlv = fx_cnt - 1; //pinlv /* wire [31:0] result_sig; div div_inst ( .denom ( 50_000_000 ), .numer ( fb_cnt ), .quotient ( result_sig ), .remain ( ) ); mul mul_inst ( .dataa ( result_sig ), .datab ( fx_cnt ), .result ( pinlv ) ); */ endmodule

//更改了,原来pinlv老为0的原因,现在延时一拍就ok了 module detect( clk, rst_n, sig_in, pinlv ); input clk; input rst_n; input sig_in; output [31:0] pinlv; reg fgate; reg start_cnt; reg [31:0] fx_cnt_temp; reg [31:0] fb_cnt_temp; reg [31:0] fx_cnt; reg [31:0] fb_cnt; always @(posedge clk or negedge rst_n) if(!rst_n) fgate <= 1'd0; else if(fb_cnt_temp >= 50_000_000) fgate <= 1'd0; else fgate <= 1'd1; always @(posedge clk) if(start_cnt) fb_cnt_temp <= fb_cnt_temp + 1'b1; else if(!(!start_cnt && r_start)) fb_cnt_temp <= 32'd0; reg r_start; always @(posedge clk) r_start <= start_cnt; always @(posedge sig_in) if(start_cnt) fx_cnt_temp <= fx_cnt_temp + 1'b1; else if(!(!start_cnt && r_start)) fx_cnt_temp <= 32'd0; always @(posedge sig_in) if(fgate) start_cnt <= 1'd1; else start_cnt <= 1'd0; always @(negedge start_cnt)begin fb_cnt <= fb_cnt_temp; fx_cnt <= fx_cnt_temp; end //assign pinlv = fx_cnt - 1; //pinlv wire [31:0] result_sig; div div_inst ( .denom ( 50_000_000 ), .numer ( fb_cnt ), .quotient ( result_sig ), .remain ( ) ); mul mul_inst ( .dataa ( result_sig ), .datab ( fx_cnt ), .result ( pinlv ) ); endmodule

频率低的话误差1hz左右,频率高的话误差在10hz左右