VLSI测试方法学和可测试设计 第6章 扫描路径法

一,基本的扫描路径设计

二,部分扫描设计

1,隔离的串行扫描设计

2,非串行的扫描设计

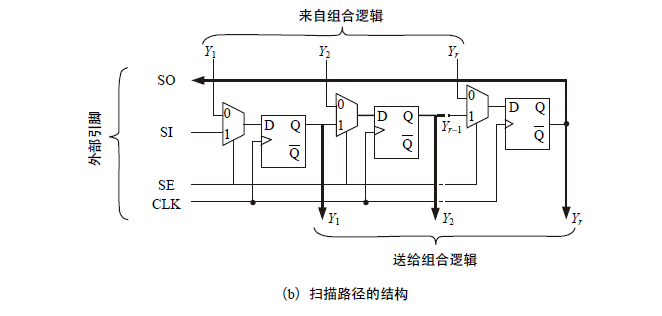

三,扫描路径的测试方法

1,组合电路部分的测试生成

只对组合电路进行测试生成的前提是:

(1)电路中没有异步信号,包括触发器的置位/复位信号;

(2)锁存有非重叠的时钟控制;

(3)测试生成时,信号传播结束点是触发器的一个输入端,此输入端按电路的原始输

出考虑;验证结束点是触发器的一个输出端,此输出端按电路的原始输入考2,

2,测试施加

测试施加分为两个阶段:先测试触发器,然后测试组合电路部分。先测试触发器的原因是,对组合电路部分的测试控制和观察要用到触发器。

四,扫描路径的结构

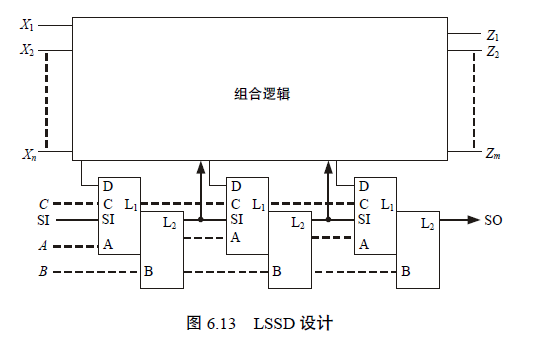

1,电平敏化扫描设计(LSSD)

(1)触发器是有效电平触发而不是边沿触发(电平敏化)

(2) 测试方式中所有触发器相互连接形成移位寄存器,可对其“读”或“写”,以供测试和分析组合电路部分(扫描设计)

采用LSSD 方法设计电路应遵循以下规则:

(1)扫描路径上所有触发器必须是双锁存设计(L1,L2);

(2)触发器必须由两个或两个以上的不重叠时钟控制;

(3)触发器不能由其输出信号的衍生的时钟所控制;

(4)每个时钟输入必须独立控制;

(5)系统时钟C 只能接到触发器的时钟输入;

(6)测试时,所有触发器应级连形成移位寄存器,其输入/输出应由时钟A 和B 可控,触发器也可级连成多个移位寄存器;

(7)除了A、B 时钟,其他时钟在测试时应不工作。

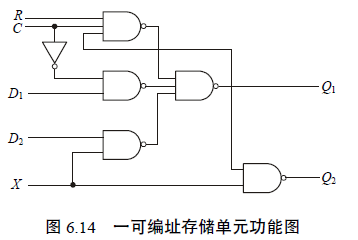

2,随机编址的存储单元

随机存取扫描技术是另一种存储单元的设计方法,它采用随机编址的存储单元构成时序

电路,允许独立地对每个存储单元的状态进行设置、重置和检查。图6.14 表示了一个可编址

的存储单元的典型结构。该结构中包括:两个附加的数据输入D1 和D2,地址线X,存储单

元输出Q1 和Q2,复位R,时钟C。D1, X, D2 以及所有存储单元的第二个输入/输出都“线或”

起来,因此电路总的只有一个附加输入和输出,此电路还包含译码器及地址寄存器。

附: 锁存器和触发器

https://www.i4k.xyz/article/Andy_ICer/111545351#1%E3%80%81%E5%8F%8C%E7%A8%B3%E6%80%81%E5%99%A8%E4%BB%B6