第1章 ARM概述及其基本编程模型

1.1 ARM技术的应用领域及其特点

无线技术

蓝牙技术

联网

消费电子

汽车

海量存储设备

成像

安全产品

arm具有RISC的一般特点:

-具有大量的寄存器。

-绝大多数操作都在寄存器中进行,通过Load/Store的体系结构在内存和寄存器之间传递数据。

-寻址方式简单。

-采用固定长度的指令格式。

还采用了特别的技术,保证在高性能的同时尽量减小体积,减少功耗:

-在同一条数据处理指令中包含算术逻辑处理单元处理和移位处理。

-使用地址自动增加(减少)来优化程序中循环处理。

-Load/Store指令可以批量传输数据,从而提高数据传输的效率。

-所有指令都可以根据前面指令执行结果,决定是否执行,以提高指令执行的效率。

1.2 ARM体系结构的版本及命名方法

1.2.1 ARM体系结构的版本

1. 版本1

2. 版本2

3. 版本3

4. 版本4

5. 版本5

6. 版本6

1.2.2 ARM体系的变种

1. Thumb指令集(T变种)

2. 长乘法指令(M变种)

3. 增强型DSP指令(E变种)

4. Java加速器Jazelle(J变种)

5. ARM媒体功能扩展(SIMD变种)

1.2.3 ARM/Thumb体系版本的命名格式

字符串ARMv。

ARM指令集版本号。

目前是1~6的数字字符。

表示变种的字符。

由于在ARM体系版本4以后,M变种成为系统的标准功能,字符M通常不需要列出来。

使用字符x表示排除某种写功能。

1.3 ARM处理器系列

ARM处理器目前包括下面几个系列的处理器产品以及其他厂商实现的基于ARM体系结构的处理器。

ARM7系列。

ARM9系列。

ARM9E系列。

ARM10E系列。

SecurCore系列。

Intel的Xscale。

Intel的StrongARM。

1.4 ARM处理器模式

1.5 ARM寄存器介绍

ARM处理器共有37个寄存器。其中包括:

31个通用寄存器,包括程序计数器(PC)在内。这些寄存器都是32位寄存器。

6个状态寄存器。这些寄存器都是32位寄存器,但目前只使用了其中12位。

ARM处理器共有7种不同的处理器模式,在每一种处理器模式中有一组相应的寄存器组。任意时刻(也就是任意的处理器模式下),可见的寄存器包括15个通用寄存器(R0~R14)、一个或两个状态寄存器及程序计数器(PC)。在所有的寄存器中,有些是各模式共用的同一个物理寄存器;有一些寄存器是各模式自己拥有的独立的物理寄存器。

通用寄存器可以分为下面3类:

未备份寄存器(The unbanked registers),包括R0~R7。

备份寄存器(The banked registers),包括R8~R14。

程序计数器PC,即R15。

CPSR(当前程序状态寄存器)可以在任何处理器模式下被访问。它包含了条件标志位、中断禁止位、当前处理器模式标志以及其他的一些控制和状态位。每一种处理器模式下都有一个专用的物理状态寄存器,称为SPSR(备份程序状态寄存器)。当特定的异常中断发生时,这个寄存器用于存放当前程序状态寄存器的内容。在异常中断程序退出时,可以用SPSR中保存的值来恢复CPSR。

1. 条件标志位

2. Q标志位

3. CPSR中的控制位

4. CPSR中的其他位

1.6 ARM体系的异常中断

在ARM体系中通常有以下3种方式控制程序的执行流程:

在正常程序执行过程中,每执行一条ARM指令,程序计数器寄存器(PC)的值加4个字节;每执行一条Thumb指令,程序计数器寄存器(PC)的值加两个字节。

整个过程是按顺序执行。通过跳转指令,程序可以跳转到特定的地址标号处执行,或者跳转到特定的子程序处执行。

当异常中断发生时,系统执行完当前指令后,将跳转到相应的异常中断处理程序处执行。

ARM处理器对异常中断的响应过程如下所述。

保存处理器当前状态、中断屏蔽位以及各条件标志位。

设置当前程序状态寄存器CPSR中相应的位。

将寄存器lr_mode设置成返回地址。

将程序计数器值(PC),设置成该异常中断的中断向量地址,从而跳转到相应的异常中断处理程序处执行。

从异常中断处理程序中返回包括以下两个基本操作:

恢复被中断的程序的处理器状态,即将SPSR_mode寄存器内容复制到CPSR中。

返回到发生异常中断的指令的下一条指令处执行,即将lr_mode寄存器的内容复制到程序计数器PC中。

复位异常中断处理程序不需要返回。

在复位异常中断处理程序开始整个用户程序的执行,因而它不需要返回。

1.7 ARM体系中存储系统

ARM体系使用单一的平板地址空间。该地址空间的大小为232个8位字节。这些字节单元的地址是一个无符号的32位数值,其取值范围为0到232-1。

ARM的地址空间也可以看作是230个32位的字单元。这些字单元的地址可以被4整除,也就是说该地址的低两位为0b00。地址为A的字数据包括地址为A、A+1、A+2、A+3 4个字节单元的内容。

在ARM版本4及以上的版本中,ARM的地址空间也可以看作是231个16位的半字单元。这些半字单元的地址可以被2整除,也就是说该地址的最低位为 0b0。地址为A的半字数据包括地址为A、A+1两个字节单元的内容。

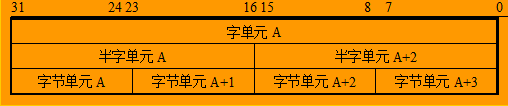

在ARM体系中,每个字单元中包含4个字节单元或者两个半字单元;1个半字单元中包含两个字节单元。但是在字单元中,4个字节哪一个是高位字节,哪一个是低位字节则有两种不同的格式:big-endian格式和little-endian格式。在big-endian格式中,对于地址为A的字单元包括字节单元A、A+1、A+2及A+3,其中字节单元由高位到低位字节顺序为A、A+1、A+2、A+3;地址为A的字单元包括半字单元A、A+2,其中半字单元由高位到低位字节顺序为A、A+2;地址为A的半字单元包括字节单元A、A+1,其中字节单元由高位到低位字节顺序为A、A+1。这种存储器格式如图1.1所示。

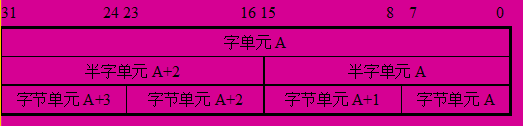

在little-endian格式中,地址为A的字单元包括字节单元A、A+1、A+2及A+3,其中字节单元由高位到低位字节顺序为A+3、A+2、A+1、A;地址为A的字单元包括半字单元A、A+2,其中半字单元由高位到低位字节顺序为A+2、A;地址为A的半字单元包括字节单元A、A+1,其中字节单元由高位到低位字节顺序为A+1、A。这种存储器格式如图1.2所示。

在ARM中,通常希望字单元的地址是字对齐的(地址的低两位为0b00),半字单元的地址是半字对齐的(地址的最低位为0b0)。在存储访问操作中,如果存储单元的地址没有遵守上述的对齐规则,则称为非对齐(unaligned)的存储访问操作。

1. 非对齐的指令预取操作

2. 非对齐的数据访问操作

在ARM中允许指令预取。在CPU执行当前指令的同时,可以从存储器中预取其后若干条指令,具体预取多少条指令,不同的ARM实现中有不同的数值。预取的指令并不一定能够得到执行。 自修改代码指的是代码在执行过程中可能修改自身。对于支持指令预取的ARM系统,自修改代码可能带来潜在的问题。当指令被预取后,在该指令被执行前,如果有数据访问指令修改了位于主存中的该指令,这时被预取的指令和主存中对应的指令不同,从而可能使执行的结果发生错误。