LCD显示的一些基本概念以及DSI的一些clock解释

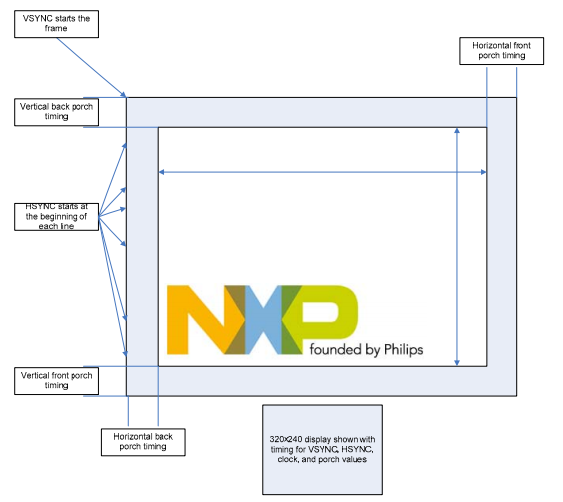

水平消隐:电子枪从左到右画出象素,它每次只能画一条扫描线,画下一条之前要先回到左边并做好画下一条扫描线的准备,这之间有一段时间叫做水平消隐(HBlank)。

垂直消隐:在画完全部256条扫描线之后它又回到屏幕左上角准备下一次画屏幕(帧),这之间的一段时间就是垂直消隐(VBlank)。电子枪就是在不断的走‘之’字形。

HFP: Horizon front porch

HBP: Horizon back porch

VFP: Vertical front porch

VBP: Vertical back porch

HDP: Horizon display period

VDP: Vertical display period

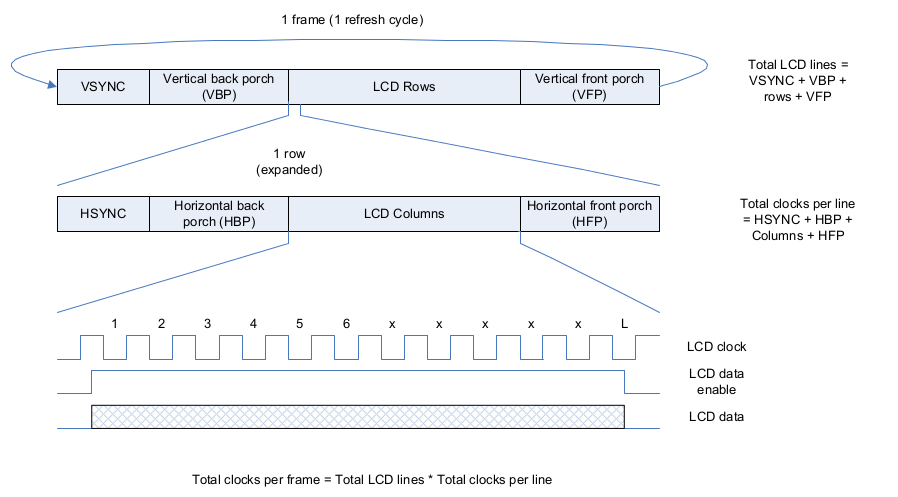

HTP = HSYNC + HDP + HFP + HBP

VTR = VSYNC + VDP + VFP + VBP

f dot _ clk = pixel clock

f dot _ clk = f v * VTR * HTP

f v = vertical frequency (这个是频率,平时见到的很多时候是60HZ)

pixel clock = ()

制式 总扫描线 图像区域扫描线 水平总象素 图像区域水平象素 采样频率

1080I/60Hz 1125 1080 2200 1920 74.25MHz

1080I/50Hz 1125 1080 2640 1920 74.25MHz

720P/60Hz 750 720 1650 1280 74.25MHz

720P/50Hz 750 720 1980 1280 74.25MHz

带宽:视频带宽代表显示器显示能力的一个综合指标,指每秒钟所扫描的图素个数,即单位时间内每条扫描线上显示的频点数总和,在模拟视频中以MHz为单位,图1的视频模拟带宽计算如下:,

DSI Clock

目前主流的lcd都是使用mipi总线,涉及到的一些clock在这里整理一下:

H-total = HorizontalActive + HorizontalFrontPorch + HorizontalBackPorch + HorizontalSyncPulse + HorizontalSyncSkew

V-total = VerticalActive + VerticalFrontPorch + VerticalBackPorch + VerticalSyncPulse + VerticalSyncSkew

Total pixel = H-total * V-total * 60(Hz通常都是这个,当然可以变).

Bitclk = Total pixel * bpp(byte) *8/lane number(有几路mipi data lane).

Byteclk = bitclk/8

Dsipclk(Dsi pixel clock) = (Byteclk * lane number)/bpp(byte) = Total pixel * 8

Byteclk = pclk * pixel depth / lane number