一文搞懂"衬底"“外延”的区别和联系

在半导体产业链中,特别是第三代半导体(宽禁带半导体)产业链中,会有衬底及外延层之分,那外延层的存在有何意义?和衬底的区别是什么呢?

首先,先普及一个小概念:晶圆制备包括衬底制备和外延工艺两大环节。衬底(substrate)是由半导体单晶材料制造而成的晶圆片,衬底可以直接进入晶圆制造环节生产半导体器件,也可以进行外延工艺加工生产外延片。外延(epitaxy)是指在经过切、磨、抛等仔细加工的单晶衬底上生长一层新单晶的过程,新单晶可以与衬底为同一材料,也可以是不同材料(同质外延或者是异质外延)。由于新生单晶层按衬底晶相延伸生长,从而被称之为外延层(厚度通常为几微米,以硅为例:硅外延生长其意义是在具有一定晶向的硅单晶衬底上生长一层具有和衬底相同晶向的电阻率与厚度不同的晶格结构完整性好的晶体),而长了外延层的衬底称为外延片(外延片=外延层+衬底)。器件制作在外延层上展开。

对于传统的硅半导体产业链而言,在硅片上制作器件(特别是高频大功率)无法实现集电区高击穿电压,小串联电阻,小饱和压降要小的要求。而外延技术的发展则成功地解决了这一困难。解决方案:在电阻极低的硅衬底上生长一层高电阻率外延层,器件制作在外延层上,这样高电阻率的外延层保证了管子有高的击穿电压,而低电阻的衬底又降低了基片的电阻,从而降低了饱和压降,从而解决了二者的矛盾。此外,GaAs等Ⅲ-Ⅴ族、Ⅱ-Ⅵ族以及其他分子化合物半导体材料的气相外延、液相外延等外延技术也都得到很大的发展,已成为绝大多数微波器件、光电器件、功率器件等制作不可缺少的工艺技术,特别是分子束、金属有机气相外延技术在薄层、超晶格、量子阱、应变超晶格、原子级薄层外延方面的成功应用,为半导体研究的新领域“能带工程”的开拓打下了夯实的基础。

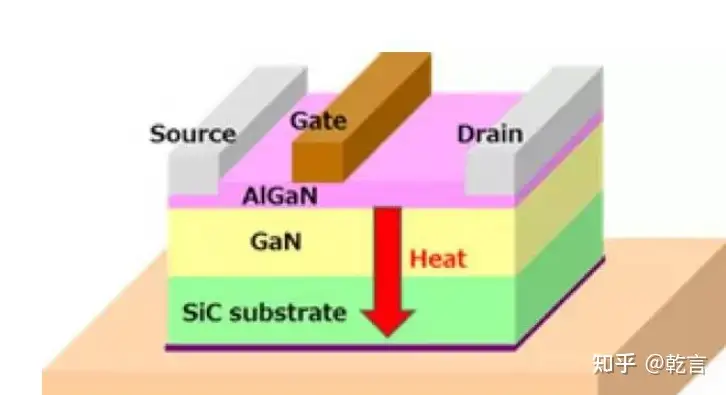

就第三代半导体器件而言,这类半导体器件几乎都做在外延层上,碳化硅晶片本身只作为衬底。SiC外延材料的厚度、背景载流子浓度等参数直接决定着SiC器件的各项电学性能。高电压应用的碳化硅器件对于外延材料的厚度、背景载流子浓度等参数提出新的要求。因此,碳化硅外延技术对于碳化硅器件性能的充分发挥具有决定性的作用,几乎所有SiC功率器件的制备均是基于高质量SiC外延片,外延层的制作是宽禁带半导体产业重要的一环。

【更新1】“同质外延的意义是什么?”

有粉丝问到,外延分为同质外延和异质外延,其中同质外延是在衬底上生长与衬底相同材料的外延层,同质外延的意义在哪儿?比如SiC衬底,外延SiC,这个跟直接在SiC晶圆上制作有什么区别吗?

这里统一回答下——提高产品稳定性和可靠性。虽然同质外延是生长与衬底相同材料的外延层,虽然材料相同,但可以提升晶圆表面的材料纯度和均匀度,通过外延处理的衬底,相比于机械抛光的抛光片,其表面平整度高、洁净度高、微缺陷少、表面杂质少,因此电阻率更加均匀,对于表面颗粒、层错、位错等缺陷也更容易控制。外延不仅仅提高了产品的性能,也能保证产品的稳定性和可靠性。

引用 https://zhuanlan.zhihu.com/p/349080786

浙公网安备 33010602011771号

浙公网安备 33010602011771号