quartus ii 与 modelsim联合仿真方法

学习Verilog 有一段时间了,今天总结下quartus ii 与 modelsim联合仿真方法步骤(开发板芯片用的是Altera的EP4CE10F17C8)

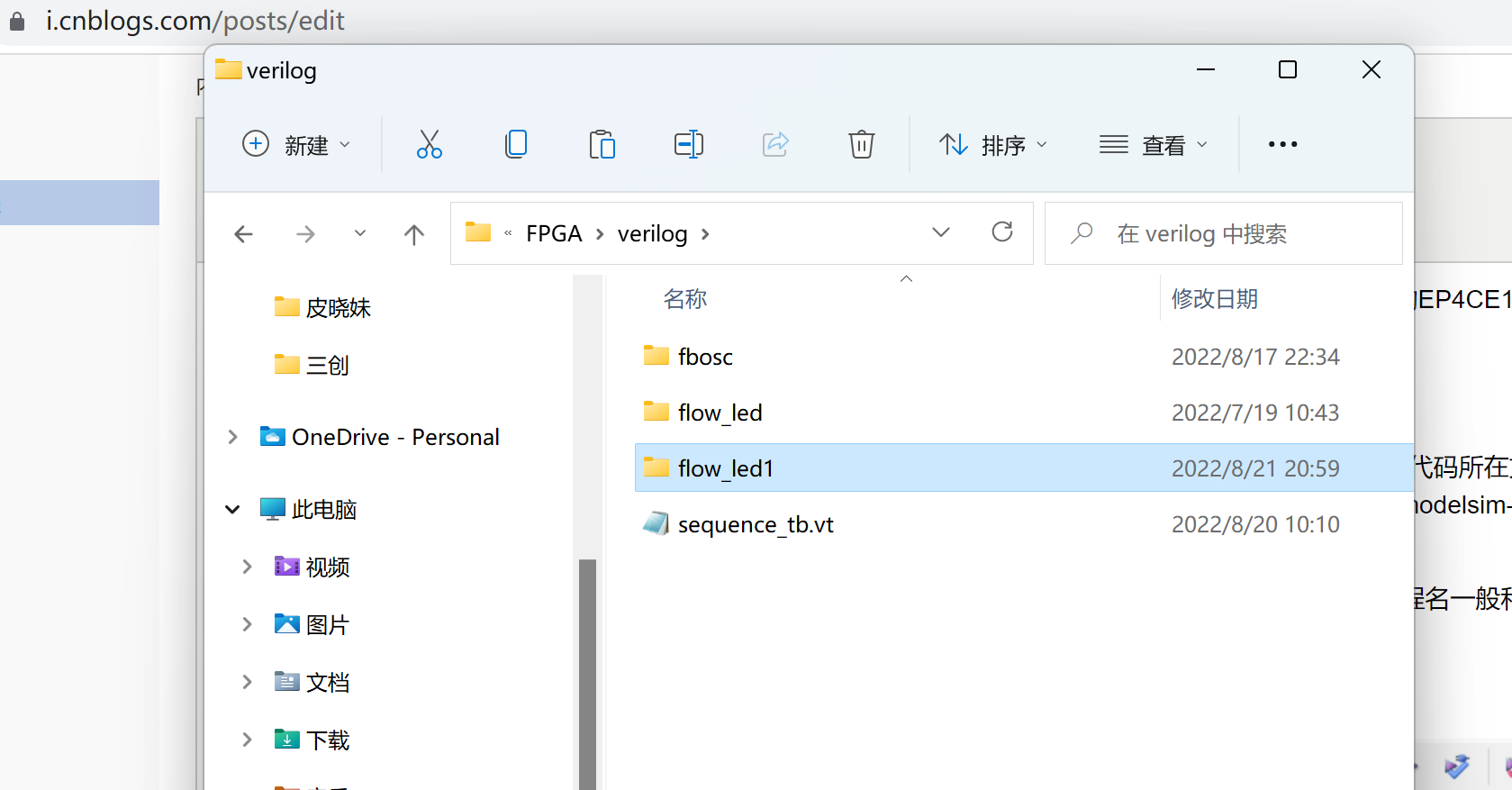

1. 首先说一下新建工程:选定工程所在的文件夹下一般以新建一工程文件夹:工程文件夹flow_led1如图:

在该文件夹下新建4个子文件夹:分别是par(工程文件,在quartus ii 里新建工程时选择该文件夹),rtl(源代码所在文件夹,工程建好后在工程下新建代码文件选择该文件夹),sim(仿真源代码所在文件夹,但联合仿真quartus ii生成的模板一般是par-->simulation-->modelsim-->.tb ),doc(存放项目文档),养成良好的习惯,在新建项目之前先将项目文件夹这样建好。

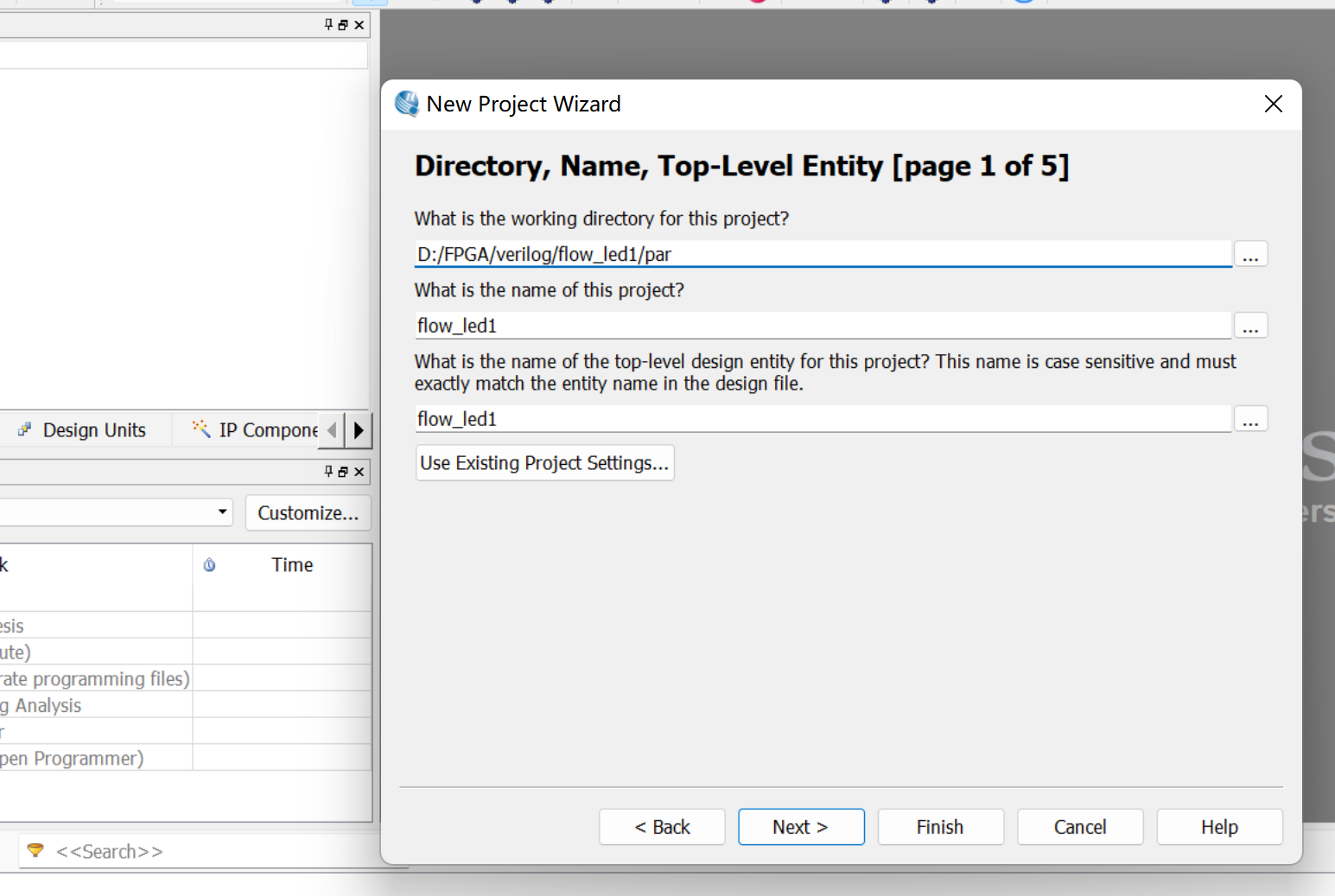

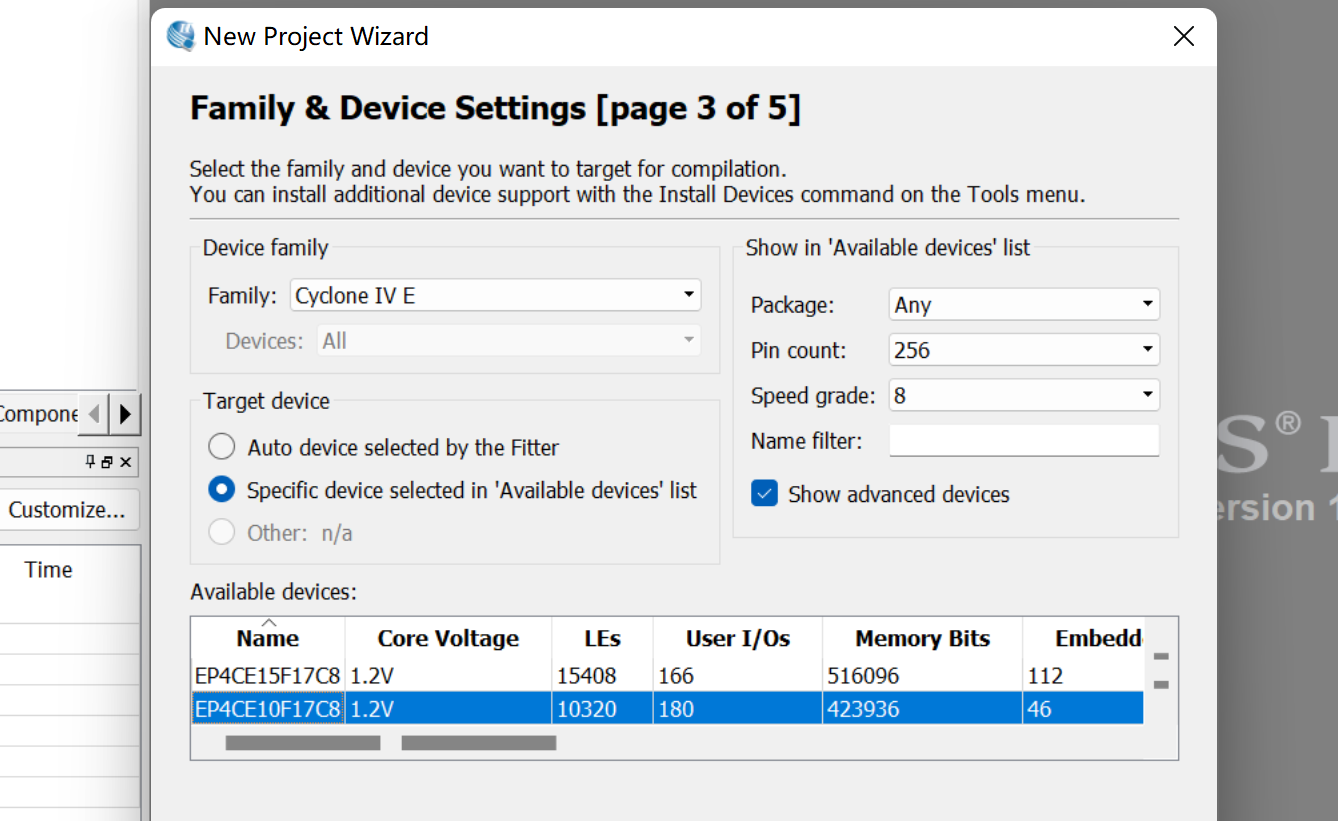

2. 在quartus ii 中新建工程 在file-->new-->quartus ii project新建工程,文件夹选择工程文件夹下面的par,工程名一般和工程文件夹同名(不一定要同名),先不添加文件,器件选择自己开发板的器件型号,我选EP4CE10F17C8,一路next finish

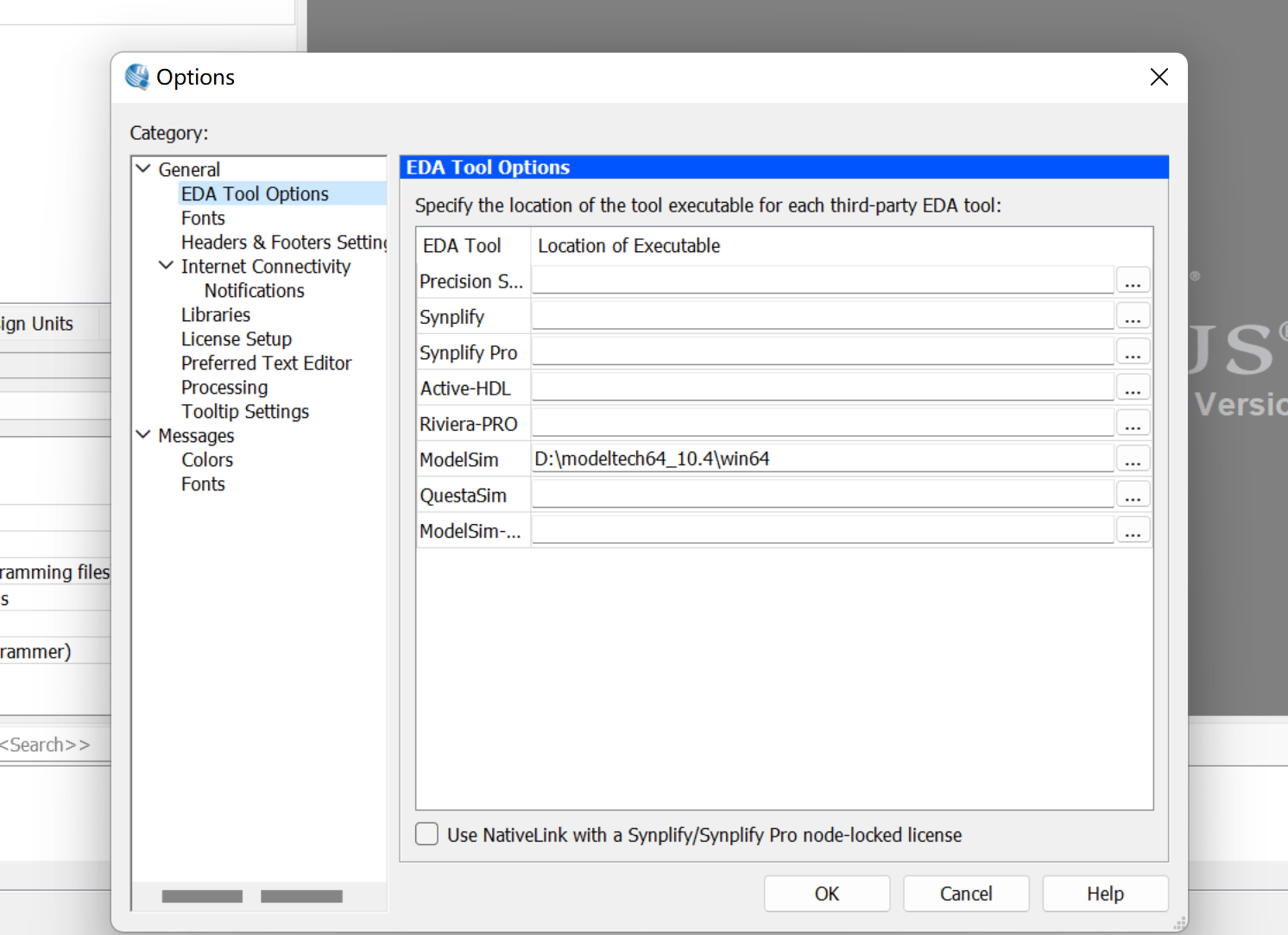

3. 初次使用时,quartus ii 还需绑定 modelsim:在quartus ii 软件中tools-->Options-->EDA tool options modelsim 栏 指定modelsim的安装文件夹,我的是D:\modeltech64_10.4\win64,点OK结束。

4.为项目新建源文件,file-->new-->Verilog HDL file,编辑源文件代码,完成后保存,路径为项目文件夹下的rtl文件夹,然后编译

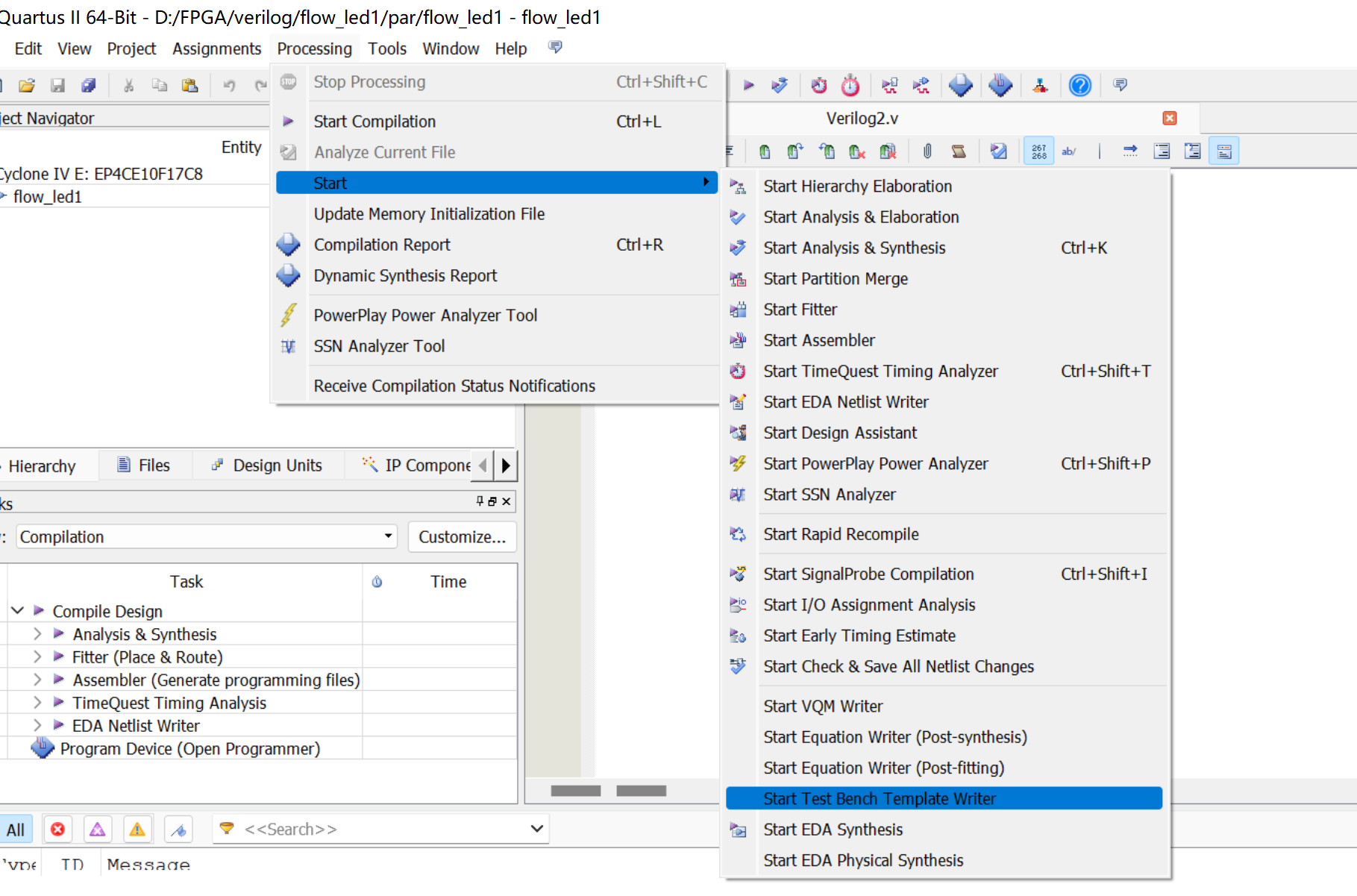

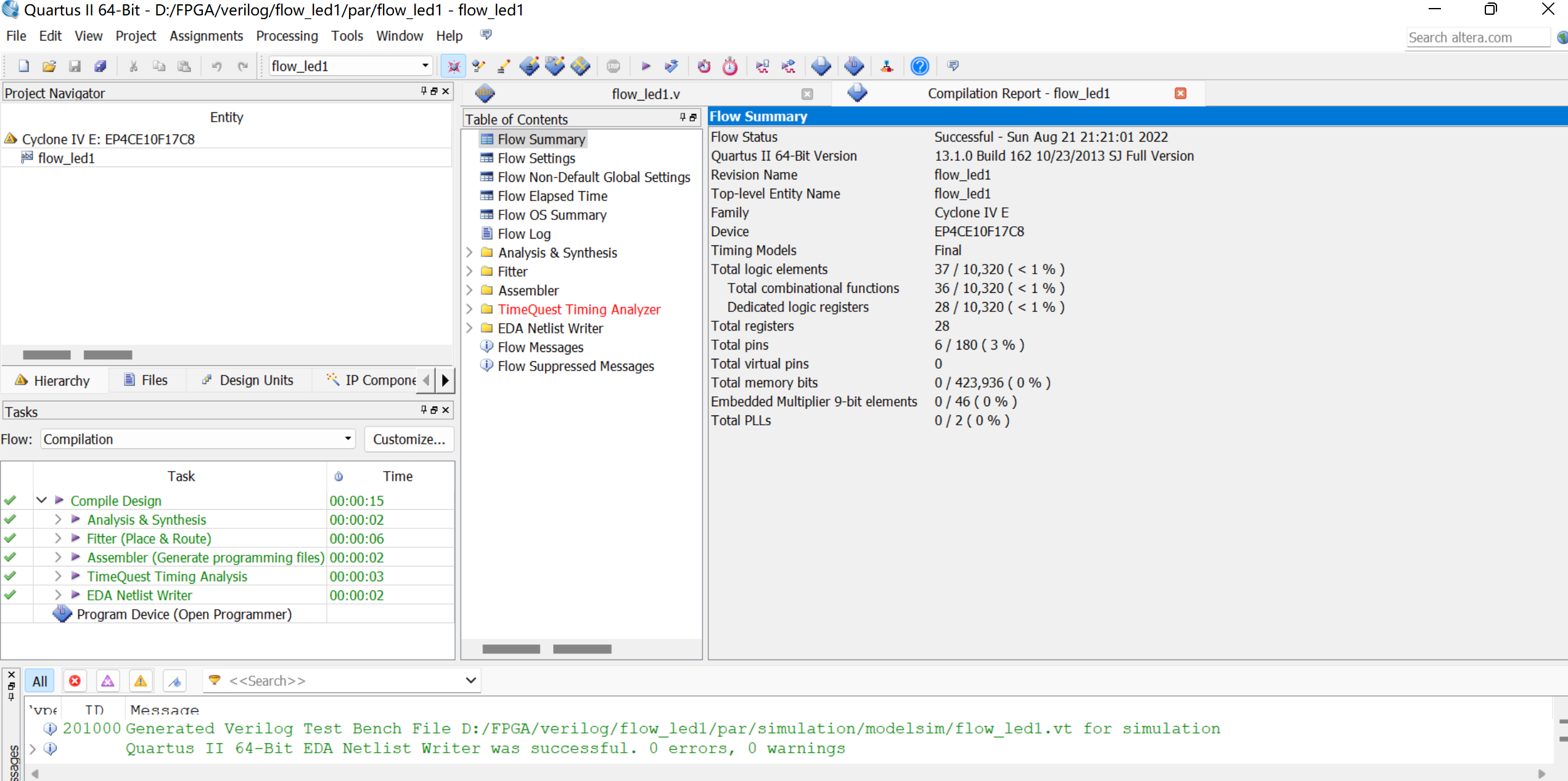

5. 自动生成仿真文件:processing-->start-->start tesbench template writer,会自动在par-->simulation-->modelsim下(EDA在下方会给出路径)产生与被仿真模块同名的仿真文件,扩展名为.vt; 打开编辑并保存仿真文件

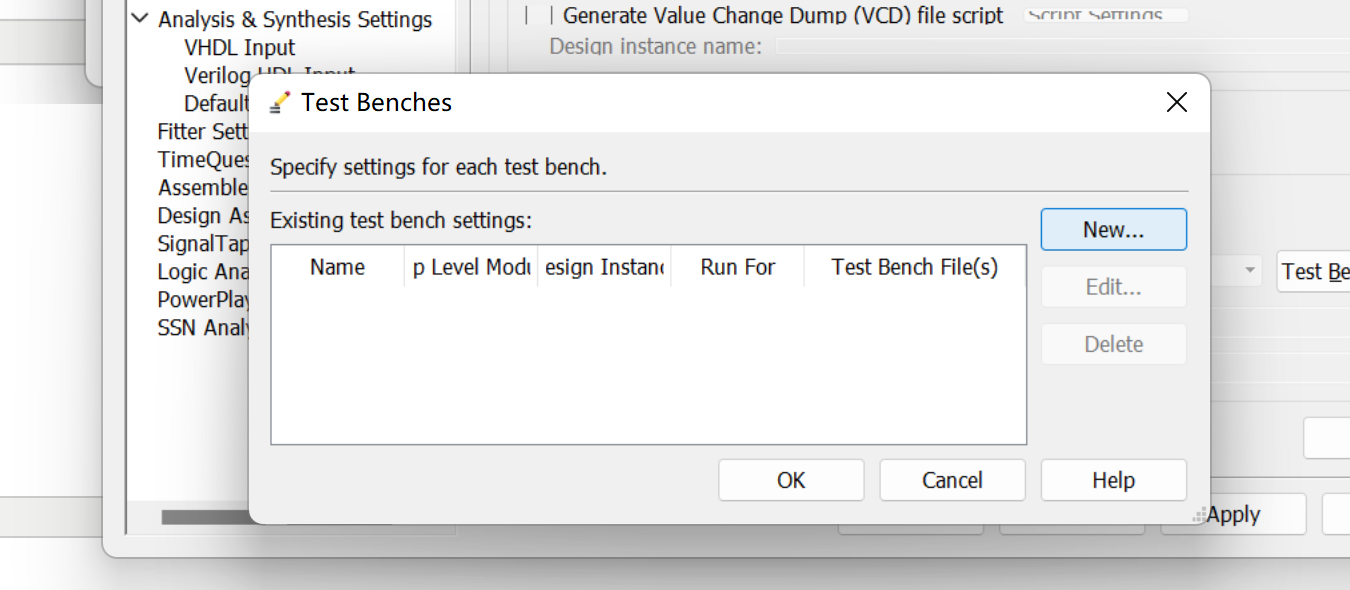

6. assignments --> settings-->simulation,在nativeLinlk settings 中选中 compile test bench,点击右边的test benches, 点击new:

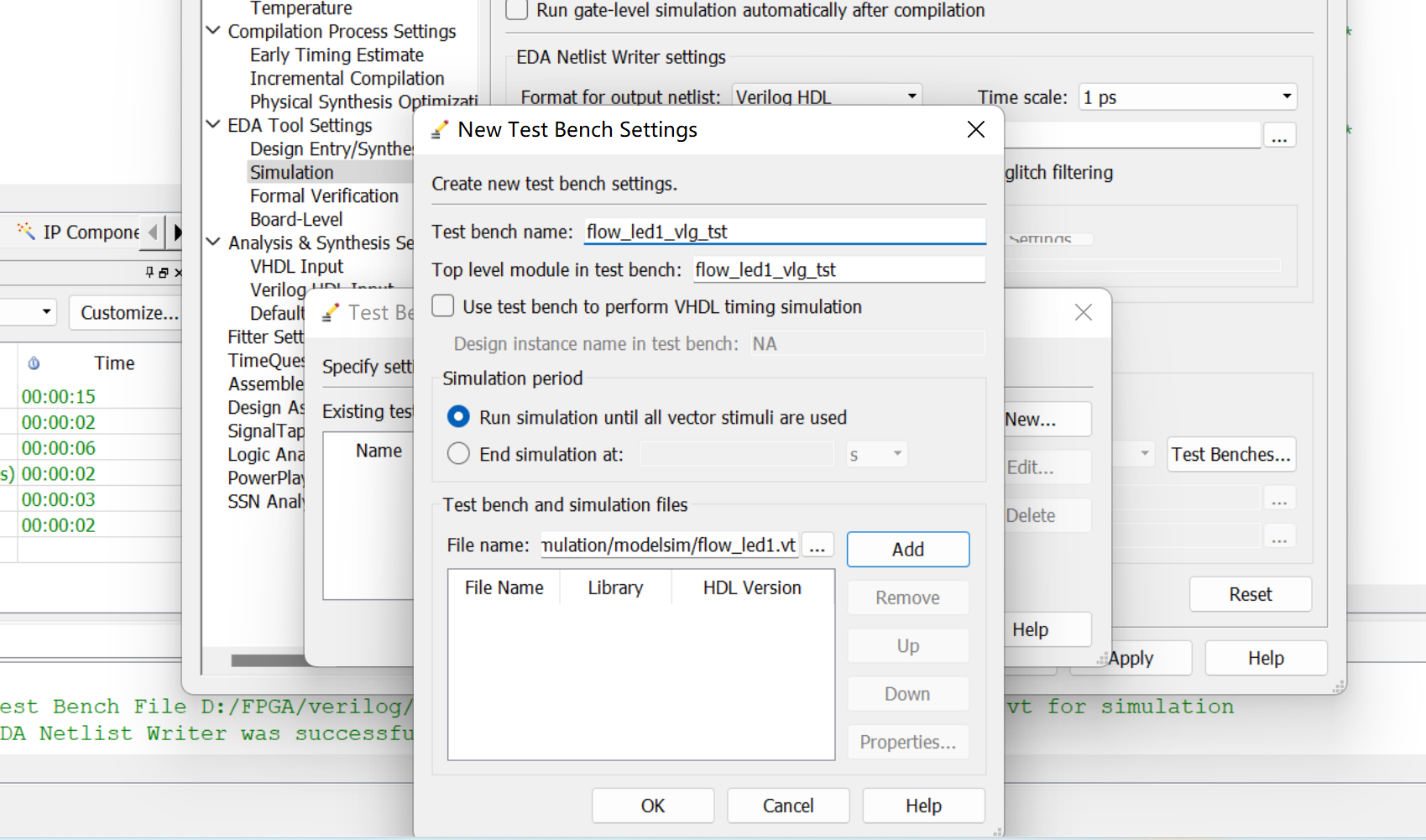

test bench name: 填软件自动生成的仿真模块名(不加括弧,这里为flow_led1_vlg_tst),file name 选择刚刚生成的仿真文件(par-->simulation-->modelsim 路径下的flow_led1.tb 文件),然后点击add,然后一步步 apply,ok。

)

7 . 开始仿真:tools--> run simulation tool-->rtl simulation / gate level simulation;modesim 自动加载并运行。