VIVADO中IO管脚分配 IO PLANING

1.从原理图导出管脚分配文件,这个适用于altera xilinx的管脚分配

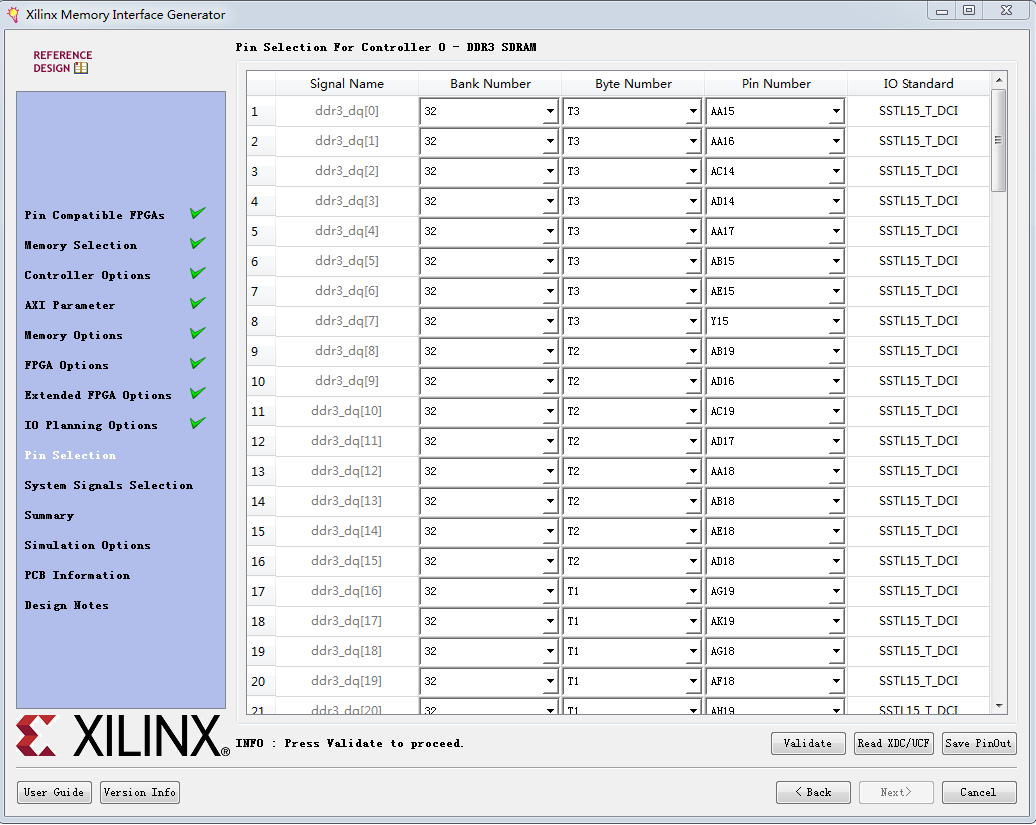

2.对于DDR的管脚分配,我们可以在MIG IP配置时,直接在IP核配置中输入管脚分配;

在这个界面中,如果事先有准备好的XDC/UCF文件,可用read xdc/ucf导入DDR3的管脚分配文件;同时也可以save pinout把管脚分配保存到新的xdc/ucf文件中;

3.其他的管脚我们可以在xdc文件中手动输入对应管脚,对应管脚的电平;

set_property IOSTANDARD LVCMOS15 [get_ports led]

set_property PACKAGE_PIN Y10 [get_ports led]

4.对BUS,对信号线一定要加上{};

set_property PACKAGE_PIN A16 [get_ports {adv7393_data[15]}]

set_property PACKAGE_PIN C16 [get_ports {adv7393_data[14]}]

set_property PACKAGE_PIN B17 [get_ports {adv7393_data[13]}]

set_property PACKAGE_PIN A17 [get_ports {adv7393_data[12]}]

set_property PACKAGE_PIN H20 [get_ports {adv7393_data[11]}]

set_property PACKAGE_PIN D16 [get_ports {adv7393_data[10]}]

set_property PACKAGE_PIN F17 [get_ports {adv7393_data[9]}]

set_property PACKAGE_PIN H19 [get_ports {adv7393_data[8]}]

set_property PACKAGE_PIN G17 [get_ports {adv7393_data[7]}]

set_property PACKAGE_PIN G18 [get_ports {adv7393_data[6]}]

set_property PACKAGE_PIN K20 [get_ports {adv7393_data[5]}]

set_property PACKAGE_PIN J19 [get_ports {adv7393_data[4]}]

set_property PACKAGE_PIN L18 [get_ports {adv7393_data[3]}]

set_property PACKAGE_PIN K18 [get_ports {adv7393_data[2]}]

set_property PACKAGE_PIN J17 [get_ports {adv7393_data[1]}]

set_property PACKAGE_PIN K19 [get_ports {adv7393_data[0]}]