综合的各种类型文件+综合过程+帮助

综合的各种类型文件

https://blog.csdn.net/b18821622297/article/details/119751768

https://blog.csdn.net/weixin_41788560/article/details/117024372

.db文件:

.lib 的二进制格式,人类不可读

.lib文件:

描述cell时序的文件,标准单元的rise timing,hold timing 等信息,以明文书写

.sdb文件

db文件对应的符号库文件

ddc文件

做完综合后吐出的设计延时信息文件,可能还包含基本的布局物理信息。

tf文件

技术文件,和milkway格式的物理信息相关,可用于创建mw_lib

tluplus文件

存储RC系数的二进制表格式。TLUPlus模型通过包括宽度,空间,密度和温度对电阻系数的影响,可以实现精确的RC提取结果

map文件

TLUPlus的层映射文件。

Milkway

https://zhuanlan.zhihu.com/p/103022068

Synopsys公司包含物理库信息的一类文件存储格式,可以通过命令创建该格式库:

# mw_reference_library是路径

create_mw_lib -technology $TECH_FILE \

-mw_reference_library $mw_reference_library \

$mw_design_library

feedth*文件和tap文件

和物理层相关的文件,但是和综合本身以及门级网表无关。

svf文件

https://blog.csdn.net/sz_woshishazi/article/details/108621525

svf文件是DC综合过程中产生的文件,用来记录DC对网表产生的一些变化,防止后续的rtl和门级网表对应不上的问题。

综合过程

https://blog.csdn.net/qq_41467882/article/details/124910074

一般综合分为三个阶段,转换,映射与优化。先通过将RTL代码转化为通用的布尔(Boolean)等式,即GTECH(Generic Technology)格式;然后执行compile命令,该命令按照设计的约束对电路进行逻辑综合和优化,使电路能满足设计的目标或约束,并且使用目标工艺库中的逻辑单元映射成门级网表。

主要命令有:

# set 用来设置 Tcl global variable,即全局变量的值

# set_app_var 用来设置 application variable, 即应用内部的变量值

# 设定RTL或者工艺库等的搜索路径

set search_path "./source/rtl ./scripts ./unmapped"

# 设置目标工艺库,用于GTECH格式映射到该工艺库上

set target_library my_tech.db

# 设置模块或者单元电路的引用,对于所有 DC 可能用到的库,都需要在link_library 中指定

# 包含*, 表示 DC 在引用实例化模块或者单元电路时首先搜索已经调进 DC memory 的模块和单元电路

set link_library " * my_tech.db"

# 设置symbol_library 符号库

# 如果想启动design_analyzer 或 design_vision 来查看、 分析电路时需要设置 symbol_library

# 没有设置,DC会用默认的符号库取代

- 检查库是否设置正确

可以通过file->setup的方式检查是否设置正确,也可以通过以下命令:

printvar target_library

printvar link_library

printvar search_path

check_library # 需要lc_install以后的library compiler支持

check_tlu_plus_files # 检查TLUPlus和技术文件之间的一致性

送出的结果:

点击查看代码

design_vision-topo> check_library

#BEGIN_XCHECK_LIBRARY

Logic Library #1:

Library name cb13fs120_tsmc_max

File name /home/ICer/DC_2017.09-SP4/ref/libs/mw_lib/sc/LM/sc_max.db

Library type non-pg_pin based db

Library Version 1.000000

Tool Created 2003.06

Data Created 21-Jun-101 (INF CREATED ON 1-JUL-2001)

Time unit 1ns

Capacitance unit 1000ff

Leakage power unit 1pW

Current unit 1uA

check_library options

Version O-2018.06-SP1

Check date and time Sun Jan 28 19:28:50 2024

#BEGIN_LIBSCREEN_UPF

Library#1 (cb13fs120_tsmc_max):

No power management cells in library#1.

#END_LIBSCREEN_UPF

#BEGIN_XCHECK_LOGICCELLS

#END_XCHECK_LOGICCELLS

#BEGIN_XCHECK_LOGICPINS

#END_XCHECK_LOGICPINS

#BEGIN_XCHECK_LOGICPGPINS

Library 1 is non-pg_pin library.

#END_XCHECK_LOGICPGPINS

#BEGIN_XCHECK_ARCS

#END_XCHECK_ARCS

#END_XCHECK_LIBRARY

Memory usage for this session 52 Mbytes.

CPU usage for this session 0 seconds ( 0.00 hours ).

Thank you...

Loading db file '/home/ICer/DC_2017.09-SP4/ref/libs/mw_lib/sc/LM/sc_max.db'

#BEGIN_XCHECK_LIBRARY

Logic Library: cb13fs120_tsmc_max

Physical Library: ../ref/libs/mw_lib/sc

check_library options:

Version: O-2018.06-SP1

Check date and time: Sun Jan 28 19:28:51 2024

List of logic library and file names

------------------------------------------------------------------------------

Logic library name Logic library file name

------------------------------------------------------------------------------

cb13fs120_tsmc_max /home/ICer/DC_2017.09-SP4/ref/libs/mw_lib/sc/LM/sc_max.db

------------------------------------------------------------------------------

#BEGIN_XCHECK_LOGICCELLS

Number of cells missing in logic library: 4 (out of 537)

Information: List of cells missing in logic library (LIBCHK-210)

-------------------------------------------------------------------------

Cell name Cell type Physical library

-------------------------------------------------------------------------

feedth3 Core sc

feedth9 Core sc

feedth Core sc

tap Core sc

-------------------------------------------------------------------------

#END_XCHECK_LOGICCELLS

#BEGIN_XCHECK_PHYSICALCELLS

Number of cells missing in physical library: 0 (out of 541)

#END_XCHECK_PHYSICALCELLS

#BEGIN_XCHECK_PINS

Number of cells with missing or mismatched pins in libraries: 0

#END_XCHECK_PINS

#BEGIN_XCHECK_CELLANTENNADIODETYPE

Number of cells with inconsistent antenna_diode_type: 0

#END_XCHECK_CELLANTENNADIODETYPE

Logic vs. physical library check summary:

Number of cells missing in logic library: 4

Information: Logic library is INCONSISTENT with physical library (LIBCHK-220)

#END_XCHECK_LIBRARY

0

design_vision-topo> check_tlu_plus_files

Sanity check for TLU+ vs MW-Tech files:

max_tlu+: ../ref/libs/tlup/cb13_6m_max.tluplus

min_tlu+: **NONE**

mapping_file: ../ref/libs/tlup/cb13_6m.map

max_emul_tlu+: **NONE**

min_emul_tlu+: **NONE**

MW design lib: TOP_LIB

--------- Sanity Check on TLUPlus Files -------------

1. Checking the conducting layer names in ITF and mapping file ...

[ Passed! ]

2. Checking the via layer names in ITF and mapping file ...

[ Passed! ]

3. Checking the consistency of Min Width and Min Spacing between MW-tech and ITF ...

[ Passed! ]

----------------- Check Ends ------------------

1

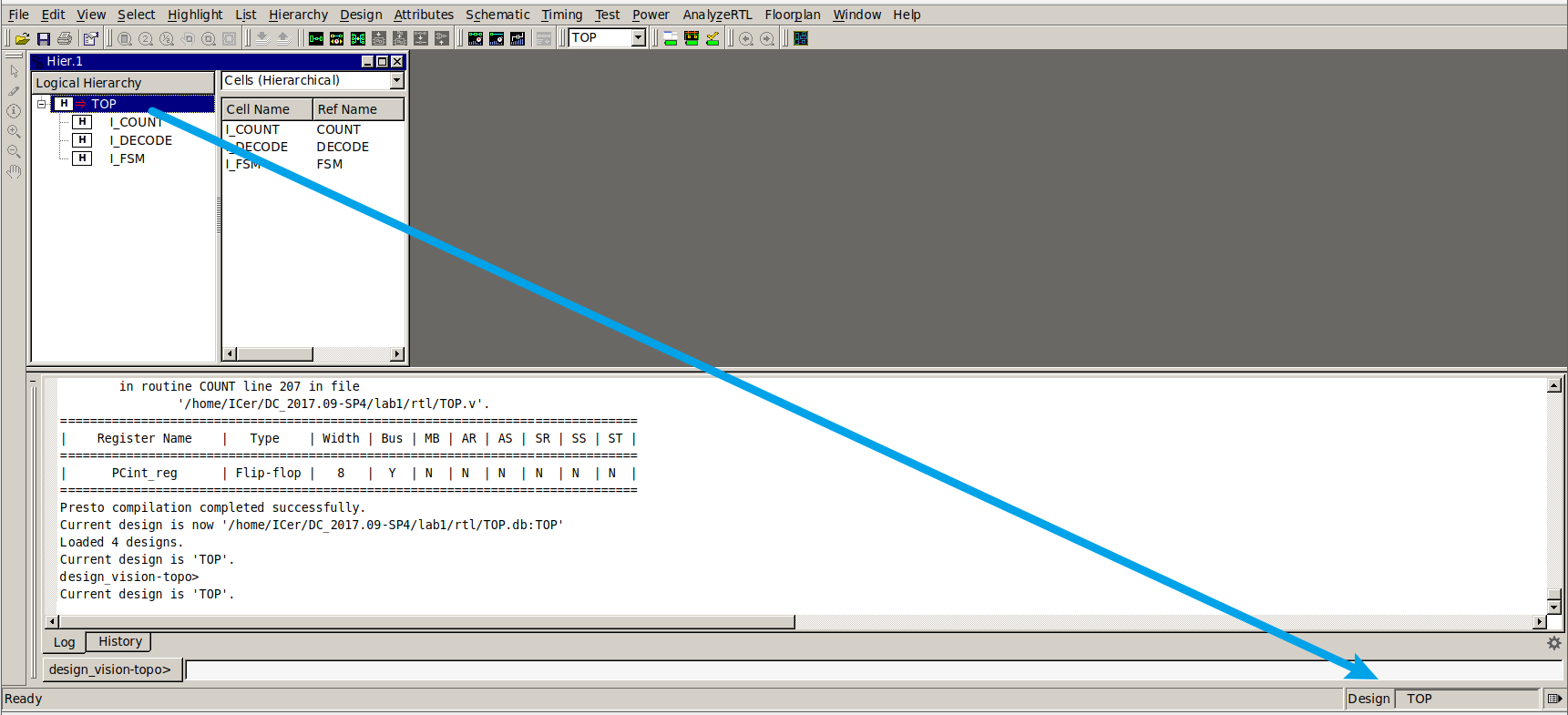

- 点击到最顶层,右下角会有显示,而点击到其它位置,显示的形式变为Cell。

- 点击file -> link design,即可进行链接。

- 然后输入命令,输出ddc文件

write_file -hier -f ddc -out unmapped/TOP.ddc

- 查看lib和design,发现design并未出现

list_libs

list_designs

- 编写约束文件和加载

约束文件如下:

set lib_name cb13fs120_tsmc_max

current_design TOP

# Reset all constraints

reset_design

# Create clock object and set uncertainty

create_clock -period 2 [get_ports Clk]

set_clock_uncertainty -setup 0.2 [get_clocks Clk]

# Set constraints on input ports

suppress_message UID-401

set_driving_cell -max -library $lib_name -lib_cell sdcfq1 [remove_from_collection [all_inputs] [get_ports Clk]]

set_input_delay 0.1 -max -clock Clk [remove_from_collection [all_inputs] [get_ports Clk]]

set_input_delay 1.2 -max -clock Clk [get_ports Neg_Flag]

# Set constraints on output ports

set_output_delay 1 -max -clock Clk [all_outputs]

set_load -max [expr [load_of $lib_name/an02d0/A1] * 15] [all_outputs]

加载方式如下:

source -verbose TOP.con

- 编译

执行如下命令,在非gui界面下编译(否则似乎是会卡死)

gui_stop

compile_ultra

gui_start

编译结果如下:

点击查看代码

design_vision-topo> gui_stop

To restart the GUI, type 'gui_start'.

design_vision-topo> comp

compare_collections compile compile_partitions compile_ultra

compare_delay_calculation compile_inplace_changed_list_file_name compile_prefer_runtime compute_polygons

compare_lib compile_mcl compile_test

design_vision-topo> compile

compile compile_mcl compile_prefer_runtime compile_ultra

compile_inplace_changed_list_file_name compile_partitions compile_test

design_vision-topo> compile

compile compile_mcl compile_prefer_runtime compile_ultra

compile_inplace_changed_list_file_name compile_partitions compile_test

design_vision-topo> compile_ultra

Loading db file '/home/synopsys/syn/O-2018.06-SP1/libraries/syn/dw_foundation.sldb'

Warning: DesignWare synthetic library dw_foundation.sldb is added to the synthetic_library in the current command. (UISN-40)

Information: Performing power optimization. (PWR-850)

Alib files are up-to-date.

TLU+ File = ../ref/libs/tlup/cb13_6m_max.tluplus

--------- Sanity Check on TLUPlus Files -------------

1. Checking the conducting layer names in ITF and mapping file ...

[ Passed! ]

2. Checking the via layer names in ITF and mapping file ...

[ Passed! ]

3. Checking the consistency of Min Width and Min Spacing between MW-tech and ITF ...

[ Passed! ]

----------------- Check Ends ------------------

Information: Evaluating DesignWare library utilization. (UISN-27)

============================================================================

| DesignWare Building Block Library | Version | Available |

============================================================================

| Basic DW Building Blocks | O-2018.06-DWBB_201806.1 | * |

| Licensed DW Building Blocks | O-2018.06-DWBB_201806.1 | * |

============================================================================

Information: Sequential output inversion is enabled. SVF file must be used for formal verification. (OPT-1208)

Simplifying Design 'TOP'

****************************************************************

Information: TLUPlus based RC computation is enabled. (RCEX-141)

****************************************************************

Information: The distance unit in Capacitance and Resistance is 1 micron. (RCEX-007)

Information: The RC model used is TLU+. (RCEX-015)

Information: Library Derived Cap for layer METAL : 0.0002 0.0002 (RCEX-011)

Information: Library Derived Res for layer METAL : 0.00068 0.00068 (RCEX-011)

Information: Library Derived Cap for layer METAL2 : 0.00025 0.00025 (RCEX-011)

Information: Library Derived Res for layer METAL2 : 0.00041 0.00041 (RCEX-011)

Information: Library Derived Cap for layer METAL3 : 0.00025 0.00025 (RCEX-011)

Information: Library Derived Res for layer METAL3 : 0.00041 0.00041 (RCEX-011)

Information: Library Derived Cap for layer METAL4 : 0.00021 0.00021 (RCEX-011)

Information: Library Derived Res for layer METAL4 : 0.0004 0.0004 (RCEX-011)

Information: Library Derived Cap for layer METAL5 : 0.00021 0.00021 (RCEX-011)

Information: Library Derived Res for layer METAL5 : 0.0002 0.0002 (RCEX-011)

Information: Library Derived Cap for layer METAL6 : 0.00027 0.00027 (RCEX-011)

Information: Library Derived Res for layer METAL6 : 6.1e-05 6.1e-05 (RCEX-011)

Information: Library Derived Horizontal Cap : 0.00022 0.00022 (RCEX-011)

Information: Library Derived Horizontal Res : 0.00043 0.00043 (RCEX-011)

Information: Library Derived Vertical Cap : 0.00024 0.00024 (RCEX-011)

Information: Library Derived Vertical Res : 0.00029 0.00029 (RCEX-011)

Information: Using derived R and C coefficients. (RCEX-008)

Information: Using region-based R and C coefficients. (RCEX-013)

Information: Library Derived Via Res : 0.00061 0.00061 (RCEX-011)

Loaded alib file '../alib-52/sc_max.db.alib'

Building model 'DW01_NAND2'

Information: Ungrouping hierarchy I_FSM before Pass 1 (OPT-776)

Information: Ungrouping hierarchy I_DECODE before Pass 1 (OPT-776)

Information: Ungrouping hierarchy I_COUNT before Pass 1 (OPT-776)

Information: Ungrouping 3 of 4 hierarchies before Pass 1 (OPT-775)

Information: State dependent leakage is now switched from on to off.

Beginning Pass 1 Mapping

------------------------

Processing 'TOP'

Implement Synthetic for 'TOP'.

Memory usage for J1 task 411 Mbytes -- main task 411 Mbytes.

Updating timing information

Information: Updating design information... (UID-85)

Beginning Mapping Optimizations (Ultra High effort)

-------------------------------

Mapping Optimization (Phase 1)

Information: Added key list 'DesignWare' to design 'TOP'. (DDB-72)

Beginning Global Optimizations

------------------------------

Global Optimization (Phase 1)

Global Optimization (Phase 2)

Global Optimization (Phase 3)

Global Optimization (Phase 4)

Global Optimization (Phase 5)

Global Optimization (Phase 6)

Global Optimization (Phase 7)

Global Optimization (Phase 8)

Global Optimization (Phase 9)

Global Optimization (Phase 10)

Global Optimization (Phase 11)

Global Optimization (Phase 12)

Global Optimization (Phase 13)

Global Optimization (Phase 14)

Global Optimization (Phase 15)

Global Optimization (Phase 16)

Global Optimization (Phase 17)

Global Optimization (Phase 18)

Global Optimization (Phase 19)

Global Optimization (Phase 20)

Global Optimization (Phase 21)

Global Optimization (Phase 22)

Global Optimization (Phase 23)

Global Optimization (Phase 24)

Global Optimization (Phase 25)

Global Optimization (Phase 26)

Global Optimization (Phase 27)

Beginning Delay Optimization

----------------------------

TOTAL

ELAPSED WORST NEG SETUP DESIGN LEAKAGE

TIME AREA SLACK COST RULE COST ENDPOINT POWER

--------- --------- --------- --------- --------- ------------------------- ---------

0:00:04 211.0 0.35 2.8 0.0 1114243.8750

0:00:04 216.8 0.22 1.8 0.0 1186501.5000

0:00:04 216.8 0.22 1.8 0.0 1186501.5000

0:00:04 231.8 0.22 1.3 0.0 1309036.6250

0:00:04 231.8 0.22 1.3 0.0 1309036.6250

0:00:04 238.8 0.16 1.2 0.0 1394417.1250

0:00:04 238.8 0.16 1.2 0.0 1394417.1250

0:00:05 239.8 0.15 1.3 0.0 1457929.0000

0:00:05 240.8 0.14 1.2 0.0 1467702.0000

Loading db file '/home/ICer/DC_2017.09-SP4/ref/libs/mw_lib/sc/LM/sc_max.db'

Loading design 'TOP'

Information: Base Cell (com): cell xn02d1, w=4510, h=3690 (npin=3)

Information: Base Cell (seq): cell sdcrq1, w=12710, h=3690 (npin=5)

****************************************************************

Information: TLUPlus based RC computation is enabled. (RCEX-141)

****************************************************************

Information: The distance unit in Capacitance and Resistance is 1 micron. (RCEX-007)

Information: The RC model used is TLU+. (RCEX-015)

Information: Library Derived Cap for layer METAL : 0.0002 0.0002 (RCEX-011)

Information: Library Derived Res for layer METAL : 0.00068 0.00068 (RCEX-011)

Information: Library Derived Cap for layer METAL2 : 0.00025 0.00025 (RCEX-011)

Information: Library Derived Res for layer METAL2 : 0.0004 0.0004 (RCEX-011)

Information: Library Derived Cap for layer METAL3 : 0.00025 0.00025 (RCEX-011)

Information: Library Derived Res for layer METAL3 : 0.0004 0.0004 (RCEX-011)

Information: Library Derived Cap for layer METAL4 : 0.00021 0.00021 (RCEX-011)

Information: Library Derived Res for layer METAL4 : 0.0004 0.0004 (RCEX-011)

Information: Library Derived Cap for layer METAL5 : 0.00021 0.00021 (RCEX-011)

Information: Library Derived Res for layer METAL5 : 0.0002 0.0002 (RCEX-011)

Information: Library Derived Cap for layer METAL6 : 0.00027 0.00027 (RCEX-011)

Information: Library Derived Res for layer METAL6 : 6.1e-05 6.1e-05 (RCEX-011)

Information: Library Derived Horizontal Cap : 0.00022 0.00022 (RCEX-011)

Information: Library Derived Horizontal Res : 0.00043 0.00043 (RCEX-011)

Information: Library Derived Vertical Cap : 0.00024 0.00024 (RCEX-011)

Information: Library Derived Vertical Res : 0.00029 0.00029 (RCEX-011)

Information: Using derived R and C coefficients. (RCEX-008)

Information: Using region-based R and C coefficients. (RCEX-013)

Information: Library Derived Via Res : 0.00061 0.00061 (RCEX-011)

...33%...67%...100% done.

Collecting Buffer Trees ... Found 0

Processing Buffer Trees ...

[0] 100% Done ...

Information: Automatic high-fanout synthesis deletes 0 cells. (HFS-802)

Information: Automatic high-fanout synthesis adds 0 new cells. (PSYN-864)

Beginning Timing Optimizations

------------------------------

TOTAL

ELAPSED WORST NEG SETUP DESIGN LEAKAGE

TIME AREA SLACK COST RULE COST ENDPOINT POWER

--------- --------- --------- --------- --------- ------------------------- ---------

0:00:06 240.8 0.08 0.6 0.0 1467702.0000

Global Optimization (Phase 28)

Global Optimization (Phase 29)

Global Optimization (Phase 30)

Global Optimization (Phase 31)

0:00:06 233.2 0.08 0.6 0.0 1371892.1250

0:00:06 224.8 0.08 0.6 0.0 1201157.5000

0:00:06 224.8 0.08 0.6 0.0 1201157.5000

0:00:06 224.8 0.08 0.6 0.0 1201157.5000

0:00:06 224.8 0.08 0.6 0.0 1201157.5000

0:00:06 225.5 0.08 0.6 0.0 1206779.5000

0:00:06 225.5 0.08 0.6 0.0 1206779.5000

0:00:06 225.5 0.08 0.6 0.0 1206779.5000

0:00:06 225.5 0.08 0.6 0.0 1206779.5000

0:00:06 225.8 0.07 0.6 0.0 1214215.1250

0:00:06 225.8 0.07 0.6 0.0 1214215.1250

0:00:07 225.8 0.07 0.6 0.0 1214215.1250

0:00:07 225.8 0.07 0.6 0.0 1214215.1250

0:00:07 227.5 0.07 0.6 0.0 1239151.8750

0:00:07 227.5 0.07 0.6 0.0 1239151.8750

0:00:07 227.5 0.07 0.6 0.0 1239151.8750

0:00:07 227.5 0.07 0.6 0.0 1239151.8750

0:00:07 227.5 0.07 0.6 0.0 1239151.8750

0:00:07 227.5 0.07 0.6 0.0 1239151.8750

0:00:07 224.2 0.07 0.5 0.0 1199485.0000

Beginning High Effort Optimization Phase

----------------------------------------

Beginning Timing Optimization

-----------------------------

TOTAL

ELAPSED WORST NEG SETUP DESIGN LEAKAGE

TIME AREA SLACK COST RULE COST ENDPOINT POWER

--------- --------- --------- --------- --------- ------------------------- ---------

0:00:07 224.2 0.07 0.5 0.0 1199485.0000

0:00:07 224.2 0.07 0.5 0.0 1199485.0000

0:00:07 222.2 0.07 0.5 0.0 1201534.7500

0:00:07 222.2 0.07 0.5 0.0 1201534.7500

0:00:07 223.0 0.08 0.5 0.0 1206598.8750

0:00:07 223.0 0.08 0.5 0.0 1206598.8750

0:00:07 223.0 0.08 0.5 0.0 1206598.8750

High Effort Optimization Phase Complete

---------------------------------------

Information: State dependent leakage is now switched from off to on.

Information: Propagating switching activity (low effort zero delay simulation). (PWR-6)

0:00:07 223.2 0.07 0.5 0.0 1215736.5000

Note: Symbol # after min delay cost means estimated hold TNS across all active scenarios

Optimization Complete

---------------------

Loading db file '/home/ICer/DC_2017.09-SP4/ref/libs/mw_lib/sc/LM/sc_max.db'

1

-

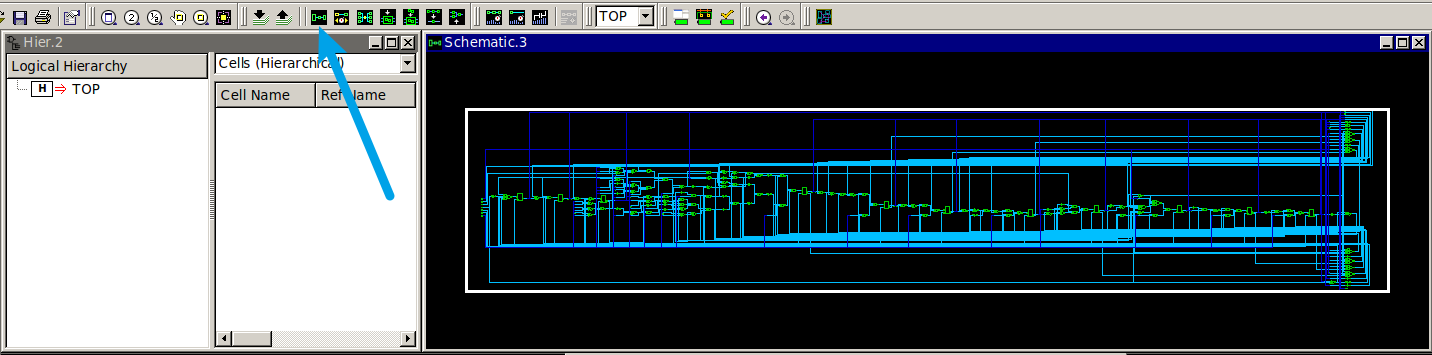

查看

选中设计顶层,点击创建原理图按钮,即可查看到综合的结果:

-

输出报告

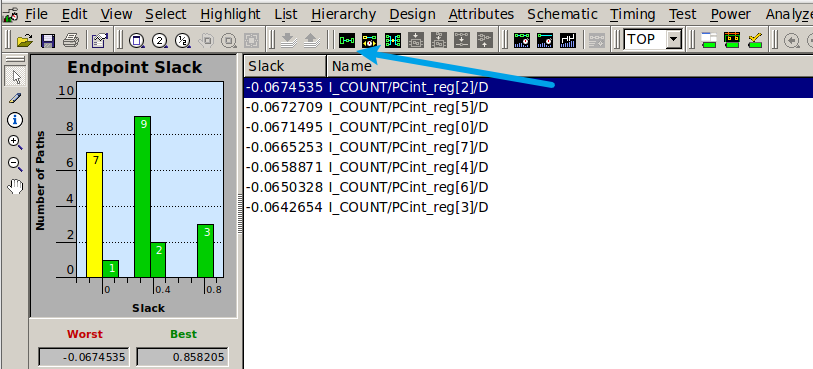

查看约束违例:

# alias rc "report_constraint -all_violators"

rc

输出结果:

点击查看代码

Information: Updating design information... (UID-85)

****************************************

Report : constraint

-all_violators

Design : TOP

Version: O-2018.06-SP1

Date : Sun Jan 28 20:12:43 2024

****************************************

max_delay/setup ('Clk' group)

Required Actual

Endpoint Path Delay Path Delay Slack

-----------------------------------------------------------------

I_COUNT/PCint_reg[2]/D 1.71 1.78 f -0.07 (VIOLATED)

I_COUNT/PCint_reg[5]/D 1.71 1.78 f -0.07 (VIOLATED)

I_COUNT/PCint_reg[0]/D 1.71 1.78 f -0.07 (VIOLATED)

I_COUNT/PCint_reg[7]/D 1.71 1.78 f -0.07 (VIOLATED)

I_COUNT/PCint_reg[4]/D 1.71 1.78 f -0.07 (VIOLATED)

I_COUNT/PCint_reg[6]/D 1.71 1.78 f -0.07 (VIOLATED)

I_COUNT/PCint_reg[3]/D 1.71 1.78 f -0.06 (VIOLATED)

max_leakage_power

Required Actual

Design Leakage Power Leakage Power Slack

-----------------------------------------------------------------

TOP 0.00 1215736.50 -1215736.50

(VIOLATED)

查看每个时钟关键路径上的时序:

# alias rt report_timing

rt

输出结果(slack裕量的值应该大于0才可以):

点击查看代码

****************************************

Report : timing

-path full

-delay max

-max_paths 1

Design : TOP

Version: O-2018.06-SP1

Date : Sun Jan 28 20:15:18 2024

****************************************

* Some/all delay information is back-annotated.

Operating Conditions: cb13fs120_tsmc_max Library: cb13fs120_tsmc_max

Wire Load Model Mode: Inactive.

Startpoint: Neg_Flag (input port clocked by Clk)

Endpoint: I_COUNT/PCint_reg[2]

(rising edge-triggered flip-flop clocked by Clk)

Path Group: Clk

Path Type: max

Point Incr Path

-----------------------------------------------------------

clock Clk (rise edge) 0.00 0.00

clock network delay (ideal) 0.00 0.00

input external delay 1.20 1.20 r

Neg_Flag (in) 0.06 1.26 r

U169/ZN (nd02d1) 0.12 * 1.38 f

U165/ZN (nd02d2) 0.09 * 1.47 r

U150/ZN (invbd2) 0.05 * 1.52 f

U116/ZN (nd02d2) 0.05 * 1.57 r

U117/ZN (invbd4) 0.06 * 1.64 f

U154/ZN (nd02d1) 0.04 * 1.68 r

U156/ZN (nd03d0) 0.10 * 1.78 f

I_COUNT/PCint_reg[2]/D (dfnrb2) 0.00 * 1.78 f

data arrival time 1.78

clock Clk (rise edge) 2.00 2.00

clock network delay (ideal) 0.00 2.00

clock uncertainty -0.20 1.80

I_COUNT/PCint_reg[2]/CP (dfnrb2) 0.00 1.80 r

library setup time -0.09 1.71

data required time 1.71

-----------------------------------------------------------

data required time 1.71

data arrival time -1.78

-----------------------------------------------------------

slack (VIOLATED) -0.07

1

点击查看代码

design_vision-topo> ra

****************************************

Report : area

Design : TOP

Version: O-2018.06-SP1

Date : Sun Jan 28 20:17:56 2024

****************************************

Library(s) Used:

cb13fs120_tsmc_max (File: /home/ICer/DC_2017.09-SP4/ref/libs/mw_lib/sc/LM/sc_max.db)

Number of ports: 56

Number of nets: 187

Number of cells: 144

Number of combinational cells: 133

Number of sequential cells: 11

Number of macros/black boxes: 0

Number of buf/inv: 31

Number of references: 25

Combinational area: 161.000000

Buf/Inv area: 24.750000

Noncombinational area: 62.250000

Macro/Black Box area: 0.000000

Net Interconnect area: undefined (Wire load has zero net area)

Total cell area: 223.250000

Total area: undefined

1

-

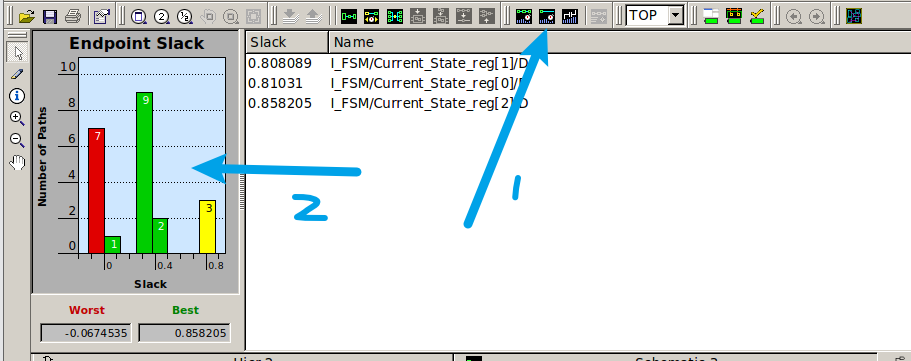

直方图查看违例的统计

绿色表示不违例,红色表示违例,黄色表示选中,并显示了选中的详细信息。

-

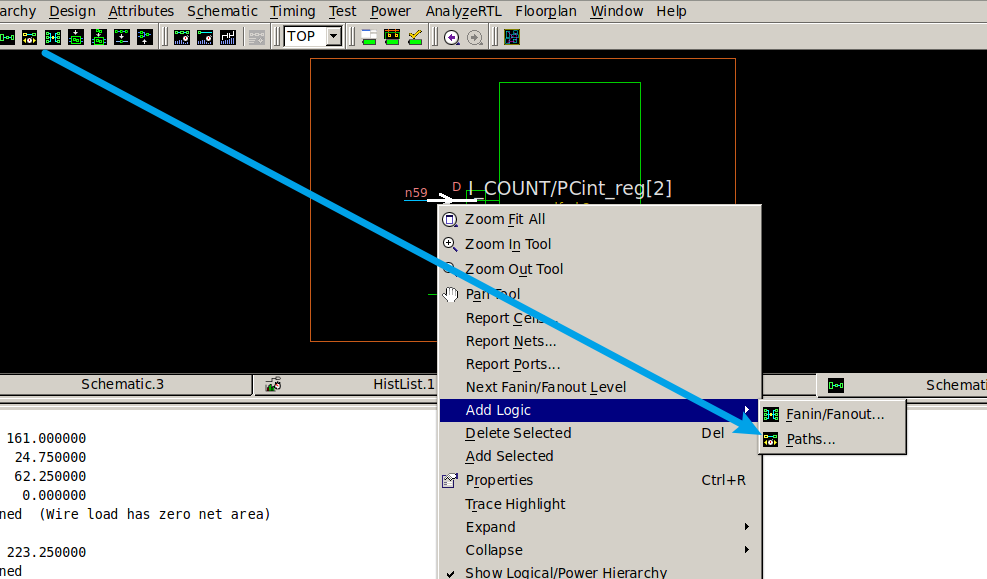

增补布线

选中违例的寄存器,以新建方式打开该寄存器

通过选中后,选中D端,右键可以增补fan in/out,增补path

-

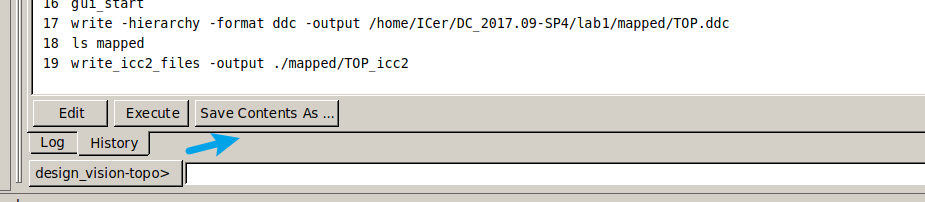

保存映射后的ddc文件

通过file-> save as 的方式,选中映射的文件夹,输出的mapped文件下一个TOP.ddc文件。 -

保存映射后的门级网表

输入以下命令:

write_icc2_files -output ./mapped/TOP_icc2

输出了一个以TOP_icc2命名的文件夹,内有.v文件,是平铺后的门级网表。

12. 保存输入过的命令

- 移除文件和退出

# alias fr "remove_design -designs"

fr

# 保存命令,下次可以用-f <filename>的形式直接执行tcl命令。

exit

- 其它加载rtl和编译的方式

dc_shell -topo

readverilog xxx.v

readsverilog xxxx.sv

current_design xxxx

link

compile_ultra

- 三步法形式的rtl加载和编译方式

file mkdir ./work

define_design_lib WORK -path ./work

analyze -format verilog -library WORK xxxx.v

elaborate TOP

或者vcs形式:

analyze -vcs "-verilog -y ./rtl +libext+.v" TOP.v

elaborate TOP

查看综合帮助手册

在新思的文档里,doc/syn/man中存放了多个文件,使用如下命令:

man -M dir xxxx

可以查找到对应的说明help。

Le vent se lève! . . . il faut tenter de vivre!

Le vent se lève! . . . il faut tenter de vivre!