日常记录(87)逻辑综合DC

高层次的综合流程

- 编写RTL

- 创建setup文件

- 创建约束文件

- 选择合适的编译流程

- 写出设计数据

综合转换

综合=翻译+优化+映射

翻译:根据约束(面积、延时等),将VHDL、Verilog、SVerilog等转换为GTECH或未映射的ddc文件

优化:优化和映射,创建映射的ddc文件(包括了verilog的信息\sdc的信息\sdf信息)。

DC计算延时的方式

WLM线负载模型,根据负载信息计算,未考虑连线。

topographical model,进行预布局后计算延时。真实的延时计算需要版图信息。

启动DC

可视化:

design_vision -topo

Shell:

dc_shell -topo

Batch mode:

dc_shell -topo -f run.tcl | tee -i run.log

在DC的命令

cd

pwd

ls

history

!!(重复上一条)

!7重复第7条history中的命令

sh <linux_command>

get_unix_variable <variable>

printvar <variable>

set_app_var <variable> <content>

dc工程文件目录

config配置文件

mapped综合的Netlist

report

rtl

script

unmapped未综合的ddc文件

DC的内部变量

search_path

target_library 第三方的工艺库,用于编译过程中创建门级网表

link_library

symbol_library

其中,前面有*表示从自己的内存中查找

使用DC

-

读取

read_verilog 读取verilog文件

read_vhdl 读取VHDL文件

最后读取的文件为顶层文件,

read_verilog {a.v b.v c.v},则a.v为顶层文件

read_ddc 读取ddc文件

(加载默认的GTECH库、用户的链接库,翻译为未映射的ddc文件,加载设计文件,设定当前设计(top module)) -

选择顶层文件

current_design MY_TOP

link

在link前说明设定 -

执行外部脚本

source <script_name> -

检查路径约束

check_timing -

编译

compile_ultra -

查看违例

report_constraint -all_violators -

使用html检查设计

check_design -html check_design.html

并打开

sh firefox check_design.html -

分析

analyze -format verilog {A.v TOP.v}

elaborate MY_TOP -

写出ddc到unmapped文件夹下

write -format ddc -hier -output unmapped/MY_TOP.ddc -

移除设计

remove_design -hierarchy

DC启动加载文件

.synopsys_dc.setup文件的查找位置

- DC的工作目录

- 用户根目录

- DC安装目录(syn/admin/setup/)

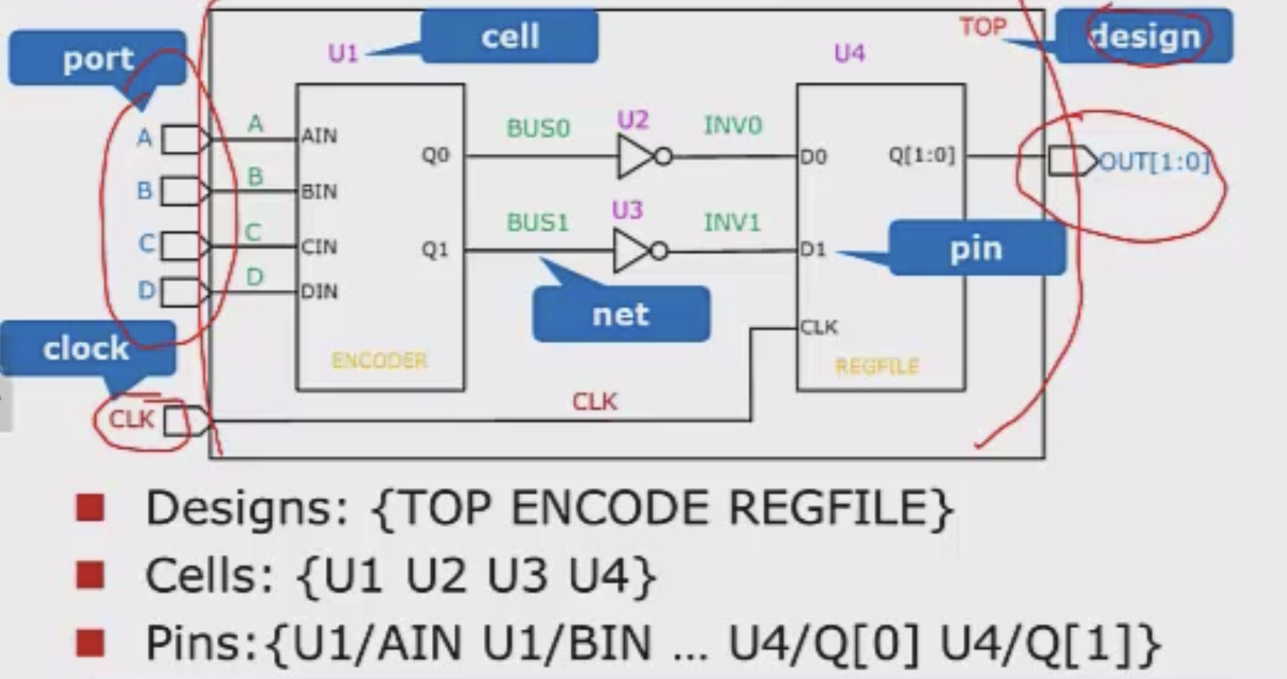

设计包含的Object

Design:设计模块

Clock:时钟

Port:Design的交互接口

Net:连线

Cell:设计中例化的器件

Pin:Cell的交互接口

get_和all_

为net中的SUM添加负载,其中的get_nets是命令,并选出了SUM。

get_nets后的SUM可以使用通配符

set_load 5 [get_nets SUM]

- 所有输入、输出、时钟、寄存器等查找。

all_inputs

all_outputs

all_clocks

all_registers

这些返回都是集合

query_objects $<name_>; sizeof_collection $<name_>

集合是系统中获取到的句柄

echo $a是返回了集合的句柄,在设置了名为a的集合后,

查看集合的内容,查看集合的大小,

set a [all_inputs ]

echo $a

query_objects $a

sizeof_collection $a

filter_collection

过滤掉map的cell

显示出了所有的cell集合

filter_collection [get_cells *] "is_mapped == true"

filter_collection [get_cells *] "name != *"

remove_from_collection

移除输入端口中的CLK

remove_from_collection [all_inputs] [get_ports CLK]

current_design;list_designs

查看顶层,查看所有设计

current_design;list_designs

create_clock

创建时钟

create_clock -name [get_ports Clk]

index_collection

根据编号查看集合

dc_shell-topo> index_collection $a 0

{Clk}

dc_shell-topo> index_collection $a 1

{Reset}

dc_shell-topo> index_collection $a 2

{Crnt_Instrn[31]}

foreach_in_collection

以集合a的长度打印了句柄a。

foreach_in_collection port $a {echo "$a"}

list定义、查看长度、遍历

dc_shell-topo> set name [list xiaohuang xiaobai xiaoli xiaozhang]

xiaohuang xiaobai xiaoli xiaozhang

dc_shell-topo> llength $name

4

dc_shell-topo> foreach xx $name {echo "$xx"}

xiaohuang

xiaobai

xiaoli

xiaozhang

键值对创建、访问

"ages": must be anymore, donesearch, exists, get, names,

nextelement, set, size, startsearch, statistics, or unset

dc_shell-topo> set ages(zhangshan) 12

12

dc_shell-topo> set ages(lisi) 32

32

dc_shell-topo> array names ages

lisi zhangshan

dc_shell-topo> array get ages

lisi 32 zhangshan 12

本质上系统变量env是键值对

dc_shell-topo> echo $env(DC_HOME)

/home/synopsys/syn/O-2018.06-SP1

dc_shell-topo> getenv DC_HOME

/home/synopsys/syn/O-2018.06-SP1

dc_shell-topo> setenv AAAA 1111

1111

dc_shell-topo> echo $env(AAAA)

1111

dc_shell-topo> unsetenv AAAA

dc_shell-topo> unsetenv AAAA

Error: can't unset "::env(AAAA)": no such element in array

Use error_info for more info. (CMD-013)

dc_shell-topo> echo $env(AAAA)

Error: can't read "env(AAAA)": no such variable

Use error_info for more info. (CMD-013)

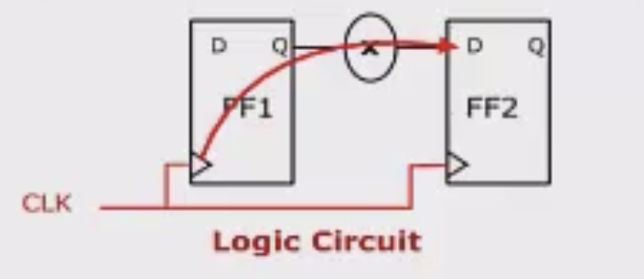

路径约束定义

- 输入逻辑路径(开始在输入端口)

- 内部路径(寄存器到寄存器)

- 输出路径(结束在输出端口)

DC是默认为同步时钟环境的,创建时钟,定义时钟周期为2ns

dc_shell-topo> create_clock -period 2 [get_ports Clk]

1

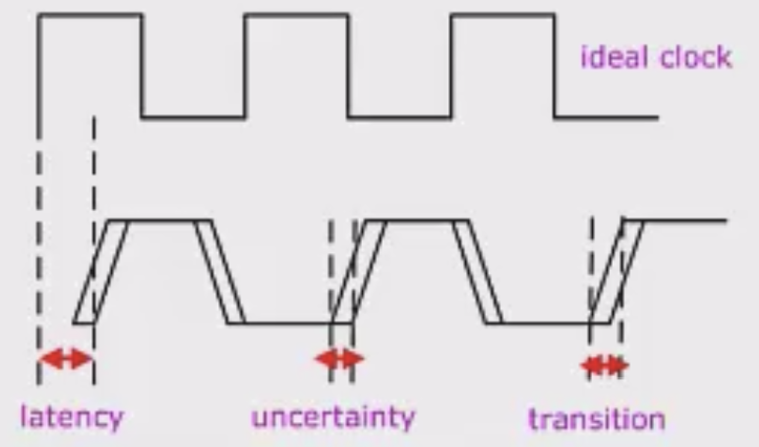

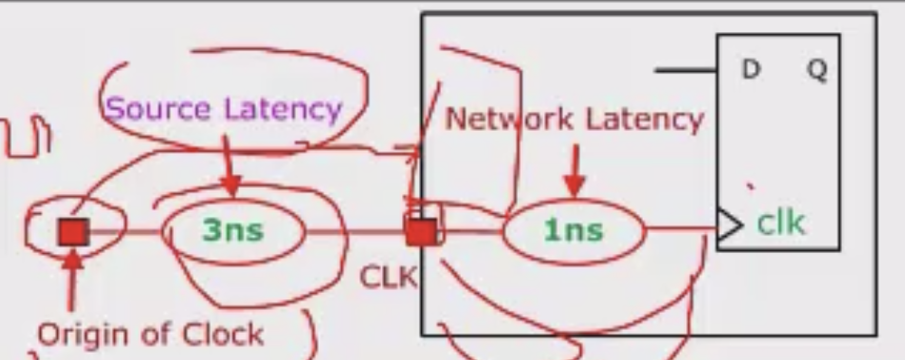

时钟延时

设置内部寄存器延时,setup(建立)的时间=skew+jitter+margin

对应红线部分,从Clk到寄存器x的时间,2-0.14-0.08,0.08是预留值,最大允许延时为1.78

set_clock_uncertainty -setup 0.14 [get_clocks Clk]

设置输入延时

dc_shell-topo> set_clock_latency -source 3 [get_clock Clk]

1

设置时钟坡度

dc_shell-topo> set_clock_transition 0.03 Clk

1

输出相对于时钟的延时

dc_shell-topo> set_output_delay 0.8 -clock Clk [all_outputs ]

1

分析rtl

analyze -format verilog rtl/TOP.v

check_design

reset_design

后端仿真

和sdf文件(标准延时格式)有关,有零延时仿真,单位延时仿真,sdf仿真,检测采样失败的功能缺陷。

Le vent se lève! . . . il faut tenter de vivre!

Le vent se lève! . . . il faut tenter de vivre!

浙公网安备 33010602011771号

浙公网安备 33010602011771号